Cadenceがソフトウェア・ドリブンSoC検証の新製品「Perspec™ System Verifier」を発表

2014年12月11日、Cadenceはソフトウェア・ドリブンSoC検証向けの新製品「Perspec™ System Verifier」を発表した。

「Perspec™ System Verifier」はソフトウェアを用いたSoC検証のためのツールで、簡単に表現すると、SoCの仕様情報とユーザーが定義したシナリオからCのテストコードを自動生成してくれるツールである。同種の製品としては、Breker Verification Systemsが「TreKSoC」という製品を出しているが、Cadenceの「Perspec™ System Verifier」はそのコンセプトからして大きく違う。

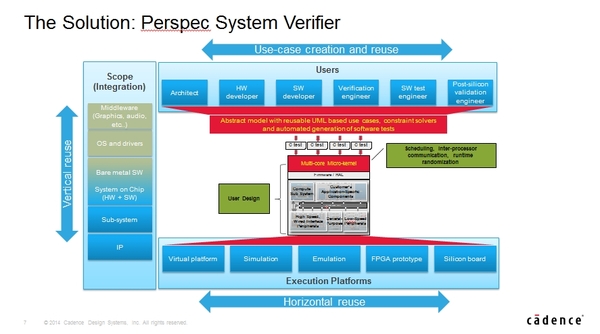

「Perspec™ System Verifier」の目指すのは、同社がこれまで培ってきた制約付きランダム的な考え方やカバレッジ手法をソフトウェア・ベースのダイレクト・テストに取り込む事で、ユーザー、検証環境、検証の抽象度を問わないソフトウェア・ドリブンSoC検証の実現がコンセプトとなっている。

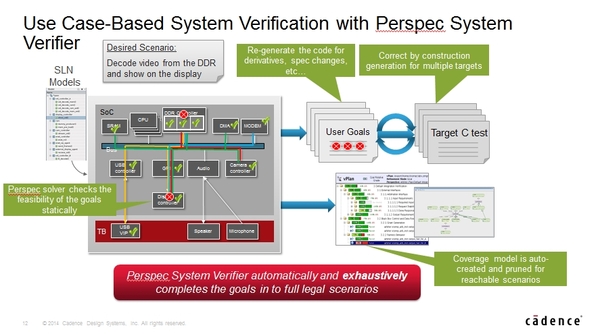

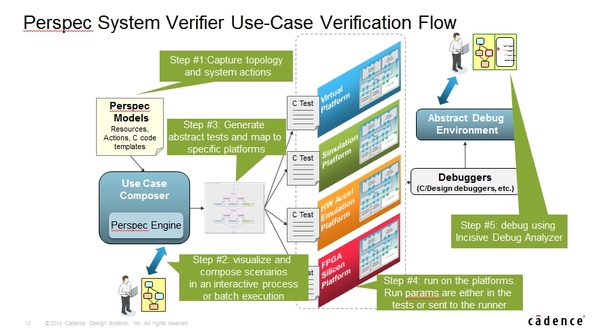

「Perspec™ System Verifier」の具体的な使用法としては、まずCのテストコードを生成するためにSoCを構成するリソースの情報、それら各リソースの機能/動き、接続、Cのテンプレートを用意する。

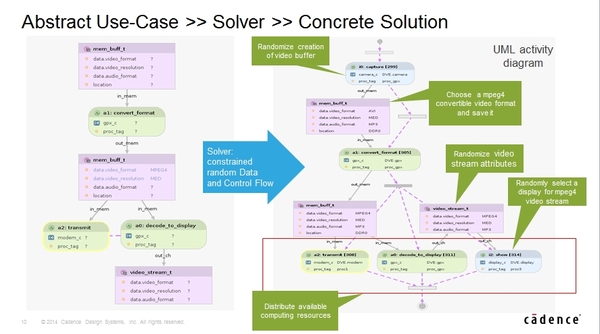

次にシナリオとしてSoCにして欲しい動作、どのように動いて欲しいかをUMLのアクティビティ・チャートで定義する。そうすると「Perspec™ System Verifier」は、前提となるリソース情報から与えられたシナリオに矛盾しないあらゆる処理パターンを自動的に洗い出しそれをCのテストコードとして出力。同テストコードを使えば、シナリオ通りにハードがアクティベートされたかどうか、どのようにハードがチェックされたかを確認出来る。

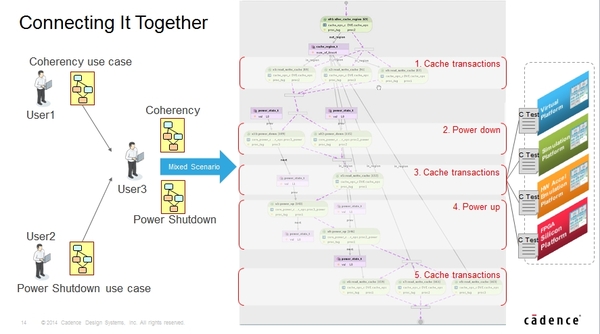

シナリオの記述においてデータ量のパラメータや使用するリソースの条件、処理の順序などを変更すれば、「Perspec™ System Verifier」はその制約条件に応じたテストコードを自動的に出力してくれるほか、複数のシナリオを組み合わせてテストコードを自動生成する事も可能。例えば、キャッシュ・コヒーレンシを確認するシナリオとパワー・シャット・オフを確認するシナリオを組み合わせて、パワー・シャット・オフしてもキャッシュ・コヒーレンシは大丈夫か?といった事を確認するテストコードを生成することも出来る。

「Perspec™ System Verifier」の生成したテストコードは、同社のシミュレータ、エミュレータ、バーチャル・プラットフォーム、FPGAプロトタイピング環境、いずれの環境でも利用する事が可能。テスト結果のカバレッジは、連携する同社の検証プロジェクト管理ツール「vManager」を用いて確認できる。

「Perspec™ System Verifier」の利用にあたってはUMLの記述が一つの壁となるが、CadenceはUMLのサンプルを含んだチュートリアルを用意しているという。

= EDA EXPRESS 菰田 浩 =

(2014.12.12

)