シャープがCMOSイメージセンサー設計の合成/配置配線でCadenceツールを選択した理由

2012年7月20日、Cadenceのユーザー・カンファレンス「CDN Live! Japan」がみなとみらいで開催された。

ここでは同セミナー行われたセッション「CMOSイメージセンサー設計におけるRTL-to-GDSIIソリューション RC/ET/VDIを適用して設計期間が半減!」について紹介する。

同事例に関してはCadenceより先行してプレスリリースが発表されていたが、セッションにてその具体的詳細が明らかにされた。講演を担当したのはシャープ株式会社 電子デバイス事業本部 センシングデバイス事業部の松本康弘氏である。

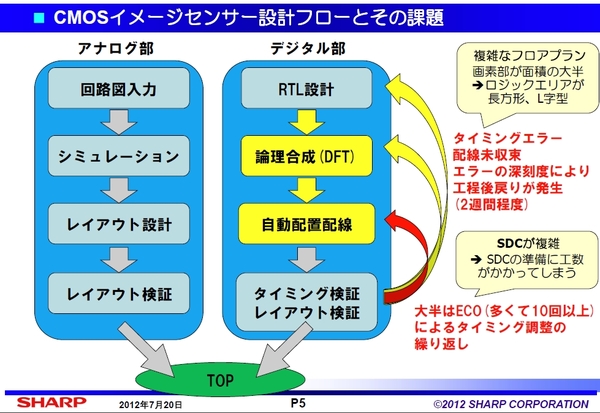

松本氏によると、CMOSイメージセンサーの設計は複数のアナログ・ブロックとデジタル・ブロックを組み合わせる階層設計であり、デジタル・ブロックに関しては画素部が面積の大半を占めるためフロアプランが複雑で、ロジック・エリアが正方形や長方形ではなくL字型や特殊な形状である事が多い。そのためタイミング・エラーや配線の未収束などにより、2週間程度の手戻り発生がしばしばある。また、SDCが複雑で準備に工数がかかり、ECOによるタイミング調整が繰り返され時には10回以上のECOを実施することもある。そこでフロアプラン、タイミング収束、ツールによる処理時間の改善を目指し、Cadenceフローへの移行を検討した。

※画像はシャープ松本氏の講演データ

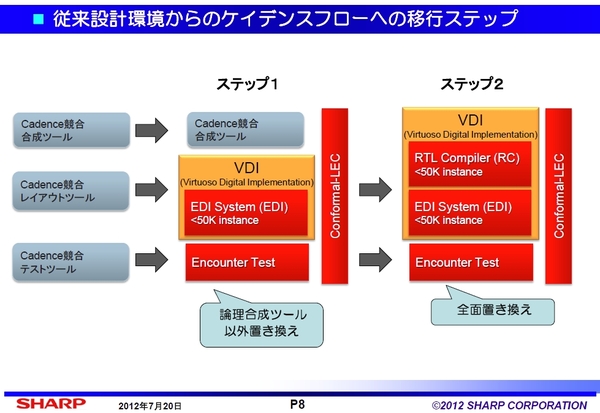

これまでシャープでは、論理合成、配置配線、テストツール共にCadenceの競合製品を利用していたが、論理合成と配置配線に関しては「RTL Compiler」と「Encounter Digital Implementation(EDI)」の両方が使えるパッケージ製品「Virtuoso Digital Implementation(VDI)」を選択。テストツールは「Encounter Test」を選んだ。「VDI」は、1ライセンスで5万インスタンス、2ライセンスで10万インスタンスと規模的な制限があるが、コストパフォーマンスが高く、デジタル部の小さいCMOSイメージセンサーの設計には最適なソリューションとして選んだ。

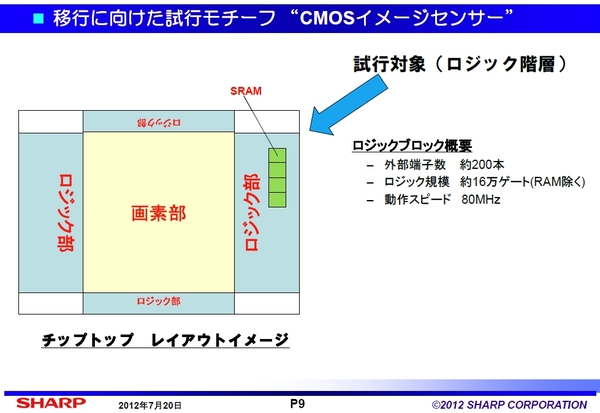

ツール・フローの移行は、部分的にツールを置き換える形と全面的にツールを置き換える形の2つのステップで検討。CMOSイメージセンサーのデザインをモチーフに評価を行った。まず既存のフローで評価デザインを試したところ、配線のバイオレーションが46000も発生し評価を中止した。続いてステップ1として、論理合成は既存のCadence競合ツールを使い、配置配線およびテストツールをCadenceに置き換えてみたところ、配線のバイオレーションが7つ残ったが、全て手修正で対処できタイミングも収束した。続いてステップ2としてCadenceツール全面置き換えで評価したところ、ツール上で全て配線が終了しタイミングもメットした。ステップ1および2いずれも設計は収束したが、ツールの処理時間に大きな差があり、ステップ1では8時間34分要したのに対し、ステップ2では僅か35分だった。

※画像はシャープ松本氏の講演データ

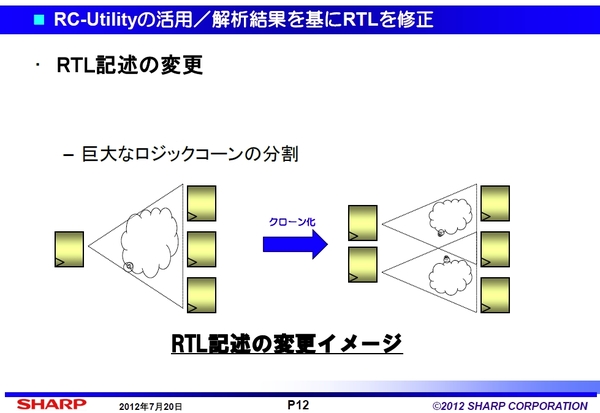

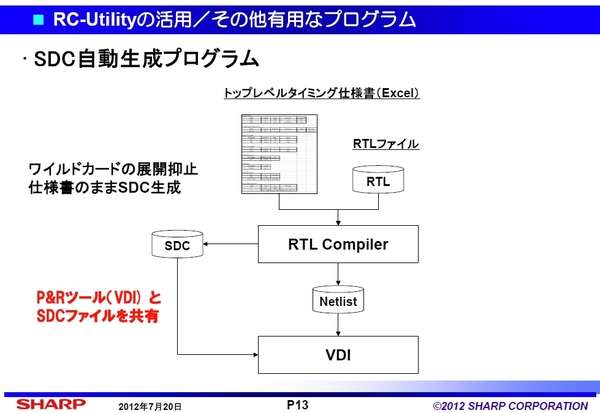

この結果から論理合成、配置配線共にCadence製品の方が優れていると判断し、Cadenceフローの採用を決定。実設計への適用を行った。実際にCadenceフローで設計した例として紹介されたのは、1400万画素、30fps、0.13μmプロセスを用いたCMOSイメージセンサーで、設計にあたってはレイアウトしやすいネットリストを得るために、論理合成「RTL Compiler」の「RC-Utility」を活用。RTLの構造解析を行い配線混雑を未然に防いだほか、SDC自動生成を使い合成とレイアウトでSDCを共通化するなどの対処を行った。これにより、レイアウトは手戻りなく1発で収束。DRC/STA共に一回でパスしデザインをテープアウトできた。結果的にEDAツールのコストと開発TATの双方を削減し、競合製品を上回る低消費電力を実現したという。

※画像はシャープ松本氏の講演データ