Verify2012 検証環境のトップをSystemVerilogでまとめた3つの例 FMSLの事例

2012年9月28日、今回で13回目の開催となるLSI検証技術セミナー「Verify 2012」が新横浜のホテルで開催された。

ここでは、同セミナーで発表されたユーザー事例講演、「SystemVerilogで "まとめる"

検証環境」について紹介する。講演を行ったのは、富士通マイクロソリューションズ株式会社 技術開発統括部 設計技術開発部の鈴木 晃一氏である。

鈴木氏の講演は一言で表現すると、SystemVerilog/UVMを用いた検証環境トライアル事例の紹介で、講演を通じてのキーワードは「まとめる」だった。

一般的に検証メソドロジUVMの事例というと、テストベンチの再利用、制約付きランダム、機能カバレッジ、検証IPの利用など、RTL機能検証にフォーカスした話が多いが、今回鈴木氏が紹介してくれた事例は、システムレベル設計手法にも詳しい同氏ならではの切り口で、SystemC TLMなどESLユーザーにとって有益な内容だった。

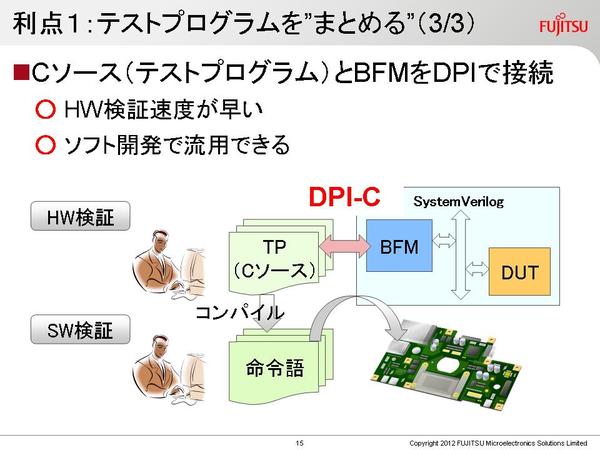

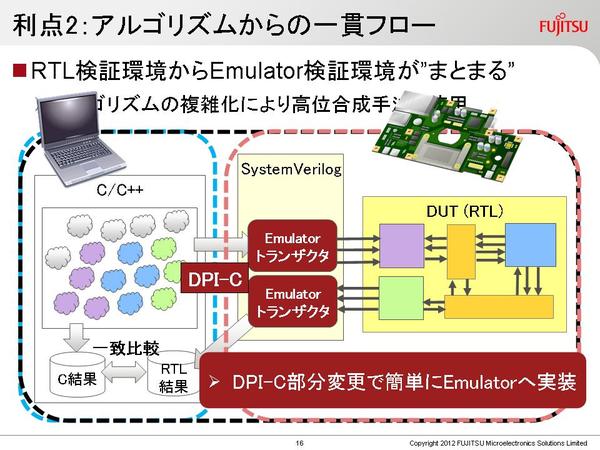

最初に鈴木氏が紹介してくれたのは、SystemVerilogの「DPI-C」を用いたアルゴリズム(C/C++)とRTLの検証環境の例。SystemVerilogとCのインタフェースを容易に実現する「DPI-C」はSystemVerilogユーザーが重宝する機能の一つで、その利用は比較的オーソドックスな手法と言えるが、鈴木氏は「DPI-C」を用いることでハードウェアおよびソフトウェアのテストプログラムをまとめる(流用できる)事が可能と指摘。更に「DPI-C」に関連するトランザクタ部分を変更するだけでエミュレーターへの実装も可能であり、容易に検証を高速化できるとあらためて「DPI-C」の有用性を強調した。

※画像は鈴木氏の講演データ(以下、全て同様)

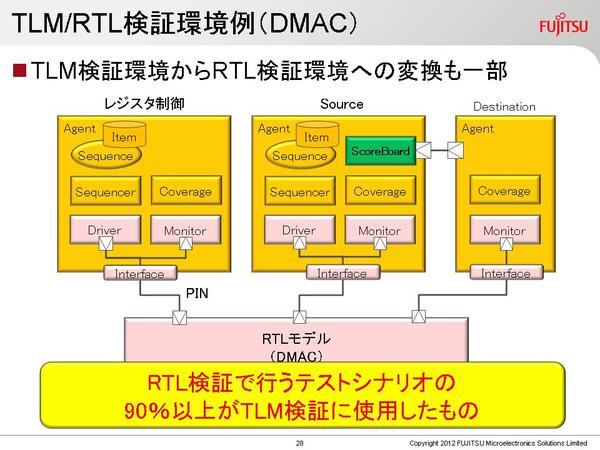

続いてTLM検証環境とRTL検証環境の話。鈴木氏は昨今、先行ソフトウェア開発やアーキテクチャ評価などの目的で作成するTLM検証環境について、RTL検証工程まで考慮したものに出来ないか?と考え、TLM検証環境を改善する一つの策としてUVMの適用を思いついた。

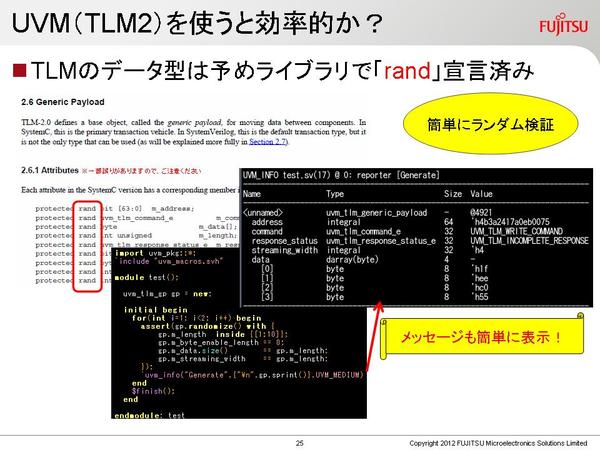

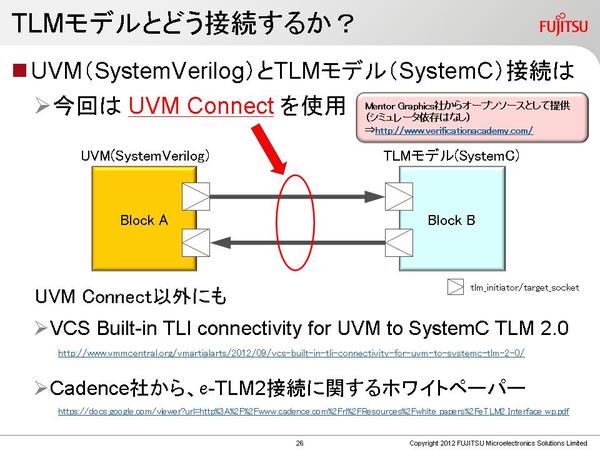

鈴木氏がUVMを適用する上でポイントと考えたのは、TLMで検証データの中身をどう作るか?という点と、UVMとTLMをどう接続するか?という点の2つ。前者についてはTLMのデータ型は予めライブラリで「rand」宣言されており、簡単にランダム検証可能であったと鈴木氏。またUVMの「sprint」を使えばTLMの中身をメッセージで出力可能で、波形を見なくてもトランザクションの中身が分かるなど、デバッグ面でもUVMの利用メリットがあるとの事だった。尚、UVMとTLMの接続については、Mentorが提供しているオープンソースのライブラリ「UVM Connect」を使用。同ライブラリはシミュレーターに依存すること無くUVMとTLMの接続に利用できるという。

実際にUVMを用いて構築したDMACのTLM検証環境は、RTL検証環境へと移行し易いもので、RTL検証向けに実施した手直しは「Driver」、「Monitor」、「Interface」などのごく一部で、RTL検証のテストシナリオも90%以上はTLM検証で使用したテストシナリオを流用できたとの事。鈴木氏によると、逆にRTL設計を行なってからTLMモデルを起こす際にも、RTL検証環境で利用したテストシナリオをTLM検証環境に流用可能で、UVMをベースとしたTLM検証環境とRTL検証環境は大部分が共通化できるという。

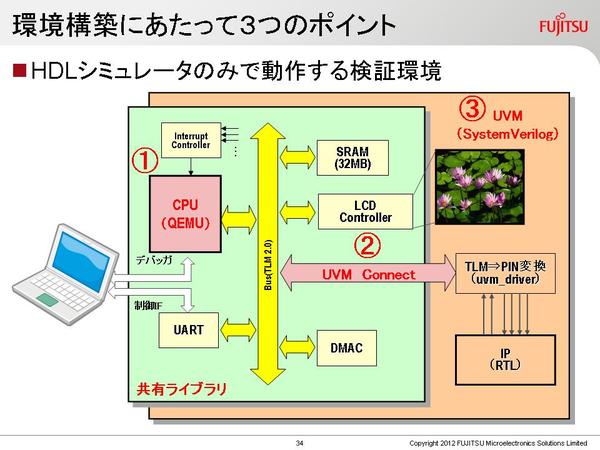

最後に紹介されたトライアル事例はバーチャル・プラットフォームとRTL検証環境の接続。

従来、バーチャル・プラットフォームとRTL(高位合成したRTL、手設計のRTL)の検証は、バーチャル・プラットフォームとHDLシミュレータのCo-Simulationで実現する形が一般的で、最近はRTL部分をエミュレーターやFPGAボードに実装する手法も広がっているが、今回鈴木氏が紹介したのは、HDLシミュレータのみでHW/SW協調検証を実現する手法だった。

鈴木氏が試したHDLシミュレーターのみのHW/SW協調検証環境は、その環境構築に大きく3つのポイントがある。

1.バーチャル・プラットフォーム部分は全てオープンソースでCPUモデルは「QEMU」を利用

2.バーチャル・プラットフォームとRTLの接続は「UVM Connect」を利用

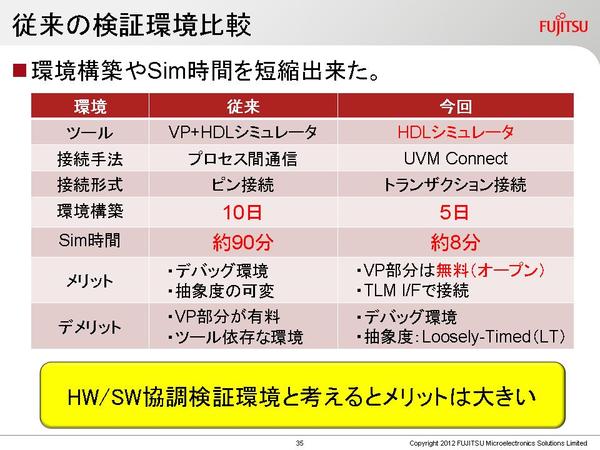

このように、全てオープンソースのモデルやライブラリを用いた、文字通りHDLシミュレーターだけで実現するHW/SW協調検証環境は様々なメリットがある。まず、環境の構築が容易でトライアルの結果では、バーチャル・プラットフォームとHDLシミュレータのCo-Simulation環境の約半分の工数で環境を構築できた。また、シミュレーション速度についても「UVM Connect」を用いたトランザクション接続により高速化を実現。デバッグ環境など商用のバーチャル・プラットフォームには劣る面もあるが、コスト的なメリットも非常に大きいと鈴木氏はコメントした。また、想定するユースケースとしては、IPのドライバ開発などがあり、対象IPに関連するモデルのみの用意で所望のシステム検証(HW/SW協調検証)が実現できるとした。

更に鈴木氏は、この環境はFPGA-SOCの検証やVerilog-AMS+ソフトウェアの検証などにも応用できる可能性がある事を示唆、それ以外にもQEMU上でLinuxをブートする事も可能なため、用途に応じて様々な環境作れるはずであるとした。

鈴木氏の講演のキー・メッセージは、検証環境のトップをSystemVerilogでまとめることで様々なメリットが得られるというものであったが、講演の最後には「検証環境は十人十色。紹介した手法が最適かどうかは分からない、引き続き議論していきたい」と語り、検証手法への更なる探究心を示した。

※本講演資料はこちらのページからダウンロードできます。