【CDNLive Japan】Cadenceのツールでプロセッサー開発の効率化に成功したNSITEXE

2018年7月20日にCadenceが開催したユーザーイベント「CDNLive Japan 2018」のレポート。

ここでは同イベントで行われた株式会社エヌエスアイテクス(以下、NSITEXE)のセッション「先端プロセッサIP開発における設計効率化」-Genus/Conformal Smart LECによる実装フロー改善-について紹介する。

同セッションの講演者は、株式会社エヌエスアイテクスの大久保 直昭氏(開発部 開発1課)である。

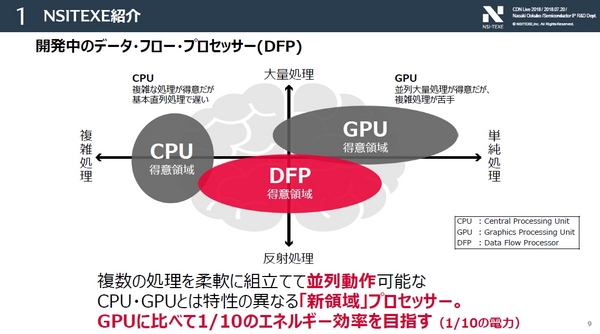

NSITEXEは2017年9月に設立されたデンソー100%子会社の車載向けの半導体IPベンダで、メイン事業として自動運転向けの高性能プロセッサーの開発を行っている。大久保氏によると同社が開発しているのは、自動運転における「瞬時の判断」を担うプロセッサーで既存のCPUやGPUとは異なる領域をターゲットとするもの。NSITEXEはそれをデータフロー・プロセッサー(DFP)と呼んでいる。

大久保氏によるとDFPの開発(RTLの設計)は、DFPのコア技術を持つ米AIチップベンチャーのThinCI社と共同で進めており、NSITEXE側ではRTLの修正がかかる毎に物理的な実装性の確認を行っている。そのため、社内での実装性確認フローを出来るだけ早く回すために、以下のような課題への対処が必要になってくる。

・フロントエンド・エンジニアによる一気通貫な実装確認フローの構築

・短TAT化(合成およびフォーマル検証の実行時間の削減)

・限られた計算機リソースでの様々なパラメータによる実装性の確認

・最適なフロアプランの早期探索

そこでこれら課題への対応策として、Cadenceの論理合成ツール「Genus」と等価性検証ツール「Conformal Smart LEC」を試用してみた。

■「Genus」の試用:複数フロアプランの傾向分析

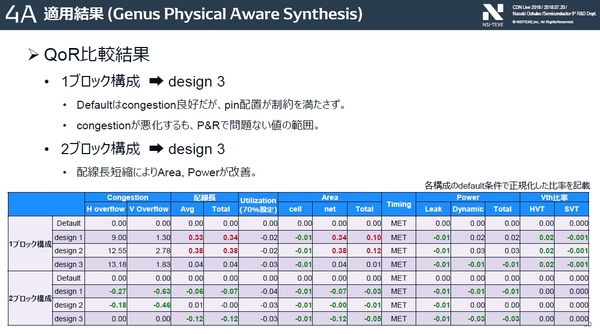

キャッシュメモリを持つメモリ比率の高いプロセッサIPの回路(43万インスタンス)をモチーフに、複数のフロアプランの傾向分析を以下の手順で実施した。

1.Genusでフィジカル合成を行いフロアプランを作成

2.アスペクト比、ポート位置、マクロ位置などを変更して任意のフロアプランを作成

3.再びフィジカル合成を行い結果を確認

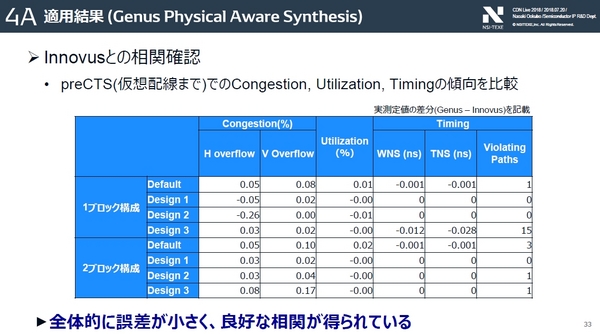

4.配置配線ツール「Innovus」による実行レポート(プレCTSまで)とGenusのレポートを比較

試行の結果、2パターン各4通りのフロアプランでQoRの分析を行い、フロアプラン制約を考慮しても配置配線で問題のないこと、Cell Densityが目標値の範囲内である事を確認。合わせて「Innovus」の結果とも誤差の少ない良好な相関関係が得られている事を確認した。これらは全てフロントエンド・エンジニアによって行われた。

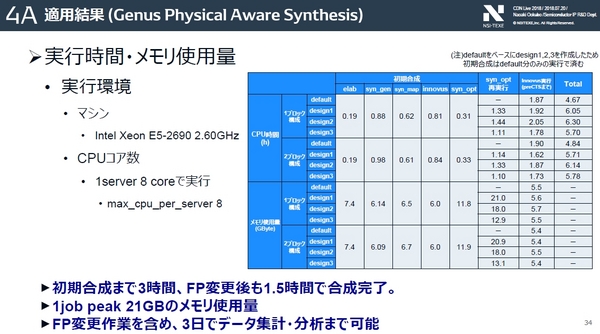

ツールの実行時間とメモリ使用量については下記スライドの通りで、「Genus」による初期フロアプラン合成まで3時間以内、フロアプラン変更後は1.5時間以内で合成が完了。ピークのメモリ使用量は21GBである事を確認した。大久保氏によるとこれら一連の作業はデータ集計、分析を含めて3日あれば十分だったとの事。大久保氏はこの結果から「Genus」を利用することでフロントエンド・エンジニアでも意図するフロアプランを自由に作成可能であり、Innovusとの相関性が高いフロアプランの探索が可能と結論付けた。

■「Conformal Smart LEC」の試用:CPU実行時間と等価性確認フローのTAT比較

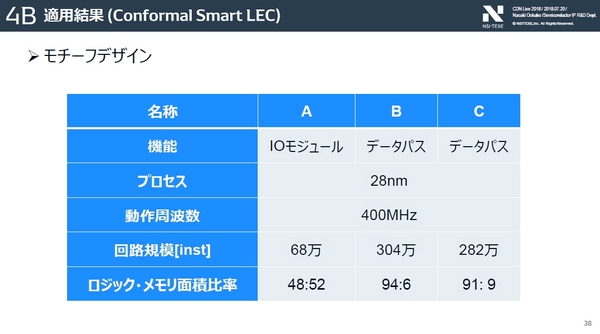

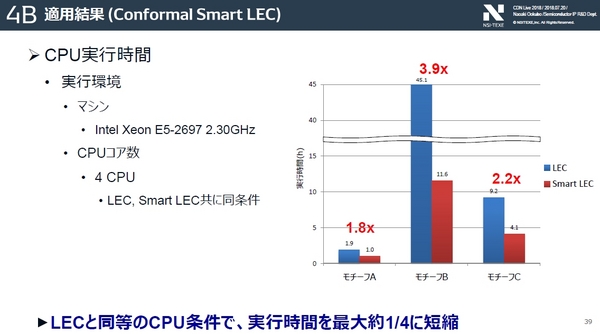

異なる3つの回路をモチーフに、「Conformal LEC」と「Conformal Smart LEC」CPU実行時間とデバッグを含む等価性確認フローのTAT比較を実施した。

CPU実行時間を比較した結果、下記図の通り「Conformal Smart LEC」の利用により同等の条件下で実行時間を最大約1/4に短縮できる事を確認した。

合成から等価性確認までのフローを比較した結果、他社ツールを用いたフローでは合計217時間かかった作業が「Conformal Smart LEC」を用いたフローでは約1/3程度の計75時間で完了できた。大久保氏によるとその大きな違いは合成時間とデバッグに要する時間で、「Genus」による合成時間の短縮効果もさることながら、「Conformal Smart LEC」によるデバッグ時間の短縮が大きかったとの事。「Conformal Smart LEC」によるデバッグは、スクリプトの書き換え、合成オプションの見直し、リネーミングルールの見直しだけで短時間で完了できたという。

今回の試用結果を受けて大久保氏は、「Genus」および「Conformal Smart LEC」の利用でフロントエンド・エンジニアの守備範囲が広がり、バックエンドの実装容易性の向上が可能となり、更に手作業によるデバッグ時間の削減によって、継続的な受け入れ確認/プロダクション・テストを短TATで実現できるようになったとまとめた。