トランザクタ-FPGAベース・プロトタイプの役割を拡大:S2C

誰もが使えなかったFPGAプロトタイプ、その潜在能力

PGAベース・プロトタイプがハードウェア設計者や研究所の技術者たちだけの管轄領域であったのは、そんなに昔の話ではありません。様々なデバイスに搭載され、接続の多いFPGAプロトタイプは細心の注意が必要なボードと考えられ、サイズや複雑さが限られたデザインを完成させるためのバックルームに押しやられていました。

しかし、この状況は変わりました。今日のFPGAプロトタイプ は、高速で駆動する大規模システムの開発を行う上で強力なプラットフォームになっています。このような能力を備えているため、これらのシステムはデザイン・インテグレーション、システム検証、ソフトウェア開発をはじめとする幅広い作業で使用されています。

このソリューションは、FPGAにマッピング可能なRTLで全て書かれたデザインには非常に適しています。しかし、依然としてデザインの一部にC++やSystemC のような記述で書かれたビヘイビア・モデルしか利用できない場合はどうでしょうか?

FPGAプロトタイプの能力を活かす手法

現在最新のシステムは、ビヘイビア・モデルとライブ・ハードウェア間の抽象度レベルを繋ぐ「トランザクタ」と呼ばれるトランザクション・レベルのインターフェイスを提供しています。トランザクタは、ホスト・マシン上で駆動するソフトウェアとメモリ、プロセッサ、高速インターフェイスを含むFPGAベース・プロトタイピング・プラットフォーム間の通信を行います。

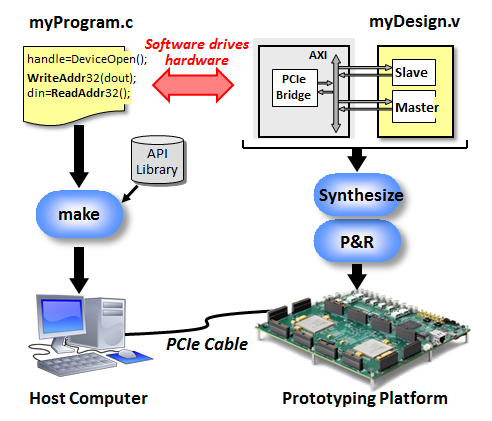

その一例としてS2CのProtoBridge™システムがあります。このシステムは、ソフトウェア・プログラムとAXI準拠のハードウェア間のトランザクタ・インターフェイスを ご提供します。また、このシステムは、ホスト・コンピュータに接続するAXI-to-PCIe ブリッジとこのブリッジを経由してデザインと通信を行うC-APIという2つの重要な部分で構成されています。software-to-AXIトランザクタは、ARMベース・システムが構築可能な柔軟性をご提供します。最大500 Mbytes/sec の転送速度に対応可能なPCIeインターフェイスと組み合わせることにより、データ集約度の高いアプリケーション向けのプラットフォームの開発を完璧に行うことができます。

豊富なアプリケーション利用

このようなシステムを使用することにより、アルゴリズム検証、IP設計、シミュレーションの高速化、コーナーケース・テスト等のデザイン・プロジェクトにおいて、はるかに早い段階でFPGAベース・プロトタイプを最大限に活用することができます。トランザクタ・インターフェイスを取り入れたプロトタイプは、デザインフローを通じて様々なアプリケーションの利用が可能です。

アルゴリズム/アーキテクチャの妥当性検証

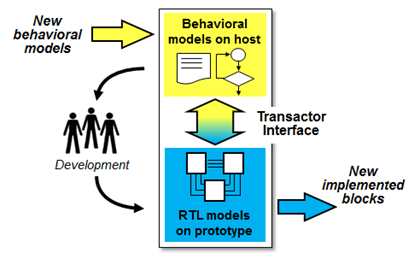

新しいシステムを開発する際、異なるアルゴリズムやアーキテクチャの妥当性を検証するために、ビヘイビア・モデルを作成します。しかし、新しいシステムは通常既存のIPを土台に構築され、RTLで利用することが可能です。トランザクタ・インターフェイスを利用することにより、ビヘイビア・モデルをRTLモデルと共にシミュレーションし、抽象度やブロック定義に使用される言語を考慮することなくフルシステムを検証することができます。

早期ソフトウェア開発

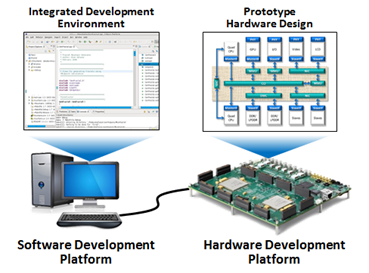

可能な限り早い工程でソフトウェアを駆動する重要性はますます高まっています。ソフトウェアを駆動できる仮想プラットフォームの実装に必要な全ての高位モデルにアクセスすることは難しいかもしれません。しかしESL設計環境にトランザクション・レベルでリンクするFPGAを利用することで効果的なソリューションになります。プログラマの開発環境とハードウェア・チームのターゲット・プラットフォームを繋ぐことで、開発工程の早期段階でソフトウェアを開発することができ、各グループは他のチームの作業に対して変更点の妥当性を検証することが可能になります。

ブロックレベル・プロトタイピング

デザイン全体をFPGAプロトタイプにマッピングすることは、特に膨大なデバイスが必要な場合では難しいかもしれません。トランザクタを使用することにより、ブロックごとにデザインをマッピングし、各ブロックをRTLベースのシミュレーション結果と比較検証することができます。この手法は、特に異なるチームが個別にIPブロックを開発する場合に効果的です。また、このアプローチは、インテグレーション工程に発生する問題回避にも役立ちます。

シミュレーションの高速化

RTLレベルのシミュレーションだけでは、大規模デザインの検証が非常に遅くなる場合があります。シミュレーション環境からFPGAプロトタイプへデザインをマッピングすることで、高性能かつサイクルアキュレートでのテスト環境を構築することが可能です。このようなシステムは、RTLレベル・シミュレーションの3桁以上に相当する数百キロヘルツで駆動することができます。

デザイン・デバッギング

FPGAでの複雑なデザインのデバッグは、特に膨大なFPGAの内部メモリが必要な場合には困難です。トランザクション・レベルのインターフェイスを使用することにより、メモリの内外で膨大なデータを簡単かつ高速に転送することができます。この手法は、メモリやレジスタに保存されたデザイン状態を読み込む場合や、メモリに状態を書き込む場合に使用することができ、デバッグに必要なデザイン・ステータスを迅速に得ることが可能です。

コーナーケース・テスト

インサーキット・テストは、恐らく今日プロトタイピングを行う最も重要な理由でしょう。しかし、通常インサーキット・テストは、常に完全なテストカバレッジを保証するわけではない制約の弱いランダムテストで、実際の操作状態を反映するものではありません。トランザクタ・インターフェイスを使用することにより、シミュレーションを実行したテストケースをプロトタイプ上で直接駆動することができ、このテストケースを即座に利用し、整合性を確認することができます。さらに、このテストケースを簡単に大容量データにまで広げ、コーナーケースや検出が難しいバグのカバレッジに利用することが可能です。

開発を大幅に促進するシステム改善のエンジン

FPGAベース・プロトタイプにトランザクタ・インターフェイスを加えることにより、様々な方法で簡単に新しいシステムを開発することができます。ビヘイビア・モデルについてご説明したように、アーキテクチャは改善され、ブロックの機能性は確定されます。このようなブロックは最終的には新しいシステムの一部として定義され、実装されます。しかし、RTLで定義され、記述されたブロックは次世代システムのIPになり、この開発工程を繰り返し使用することが可能です。このように、FPGAプロトタイピング・プラットフォームは開発を大幅に促進するシステム改善のエンジンとなり得ます。