システム-モデリングを用いたAMBA AHBとAXIバスの比較-Mirabilis Design

システム-モデリングを用いたAMBA AHBとAXIバスの比較

Mirabilis Design Inc.

組込みシステムで用いられるバスには、共有バスもしくはポイント・ツー・ポイント・バスがあります。また典型的な組み込みシステムは、プロセッサ、キャッシュ、SDRAM、DMAポート、およびAdvanced

Microcontroller Bus Architecture (AMBA)や Advanced

Peripheral Bus (APB)といった低速なI/Oブリッジ・ポート等から構成されます。さらに、多くのアプリケーションにおいて動画の使用頻度が高くなり、DSPプロセッサやハードウェア・アクセラレータに接続されるケースも増加しています。チップレベルはプロセスの微細化に伴い、前世代と同等のダイ・サイズあたりの消費電力やコストを維持しつつ、より多くの機能を実装可能です。システム・モデリングはVerilog, System Verilog, VHDL, SystemCやC/C++などのコードを用いた詳細なチップ実装と比べ、より高い抽象度でデザインの探求を可能にする新たな手法です。これにより、開発期間を大幅に短縮すると同時に、実装開始前のデザイン・トポロジの探求に、より多くの時間を費やす事が可能となります。本稿ではAMBA Advanced High-performance Bus (AHB) バスと、 AMBA Advanced eXtensible Interface (AXI)ポイント・ツー・ポイント・バスの構成に関して、約95%のサイクル精度を持つグラフィカルなモデリング環境を用いて説明します。グラフィカルなモデリングとシミュレーションによる解析は約1週間で終了致します。

下記の考察ポイントより、2種類のバスをフロー、スループット、レイテンシの観点から評価します。

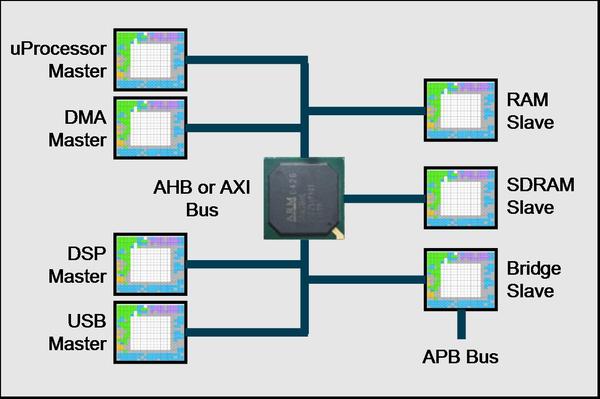

1.AHBはシングル・チャネルの共有バスです。AXIは読み/書きに最適化されたマルチ・チャネルのバスです。AHBの場合、各バス・マスタや要求を出すバス・ポートはシングル・チャネルの共有バスに接続されるのに対し、AXIの各バス・マスタはリード・アドレス・チャネル、リード・データ・チャネル、ライト・アドレス・チャネル、ライト・データ・チャネル、ライト・応答チャネルに接続されます。AXIの主要なスループット・チャネルはリード/ライト・データ・チャネルであり、アドレス・チャネルと応答チャネルは複数のリクエストによるパイプライン化を改善するためのものです。4つのマスタが各バスに接続され、3つのスレーブにアクセスしていると仮定します。4つのマスタにはマイクロ・プロセッサ、Direct Memory Access(DMA)、DSP、USBが含まれ、スレーブにはオンチップRAMやオフチップSDRAM、APBバスブリッジなどが含まれます。

2.2つのバス帯域を近似させるために、3つのバス・スレーブに対しAXIバスのリード/ライト・チャネルの数を6回数えなければなりません。AHBバスの場合データのスループット合わせるために、複数のバス幅やスピードをサポートする必要があります。システム・モデルではこれらの組み合わせをシンプルなパラメータによって変更可能ですが、AHBバスのスピードはAXIバスの倍、また倍のバス幅を仮定する必要があります。これにより、2つのバスの比較はより現実的になるでしょう。

3.両方のバス効率を評価するために、大・中・小の異なるバースト・サイズを選択します。小はAHBバス幅、中は2倍のAHBバス幅、大は4倍のAHBバス幅とします。

4.AXIが200MHzの64bitバスで動作している場合、AHBは400MHzの128bitバス幅で動作している事になります。バースト・サイズは小(16バイト)、中(32バイト)、大(64バイト)とします。

本稿では、迅速なモデル構築に必要な条件、モニタされる属性および生成する負荷に注目します。設計目標は、シングル・チャネルまたはマルチ・チャネルにおけるスループット、レイテンシおよび利用率の観点から最適なバスを選択することです。解析によって2種類のバスを16, 32, 64バイト転送ごとに比較します。チャネル利用率毎の平均は消費電力に関係します。AXIバスはパフォーマンスを改善するために複数のリード/ライト・チャネルを持ち、より良い平均とピークのレイテンシが実現されるべきですが、それは内部バスの転送とどれだけ一致するかは明確ではありません。共有AHBバスはより効率的に利用されるべきですが、アービトレーション・アルゴリズムに依存するため明確ではありません。システム・レベル・モデルは設計者に特定用途に向けた適切なバス選択の手法を提供します。

本モデリングを実行するにあたり、Mirabilis Designが提供しているVisualSimと標準システム・デザイン言語SystemCを使用しました。VisualSimは組込みシステムのパフォーマンスと消費電力のトレードオフの短期間での探求をコンセプトとしています。グラフィカルな環境上でコンフィグレーションを変更可能な、パラメータ化されたライブラリ・ブロック、アプリケーションに特化した機能、標準コンポーネント・ジェネレータ(プロセッサ、メモリ、キャッシュ、バスやスイッチ)及びテンプレート化されたSystemCなどを用いてモデリングを行うことができます。このシミュレーション環境は、最善のアーキテクチャを実行可能な仕様にするために、一連のモデルの改良および抽象化を通し最初のコンセプトの最適化を行います。

システム・モデル概要

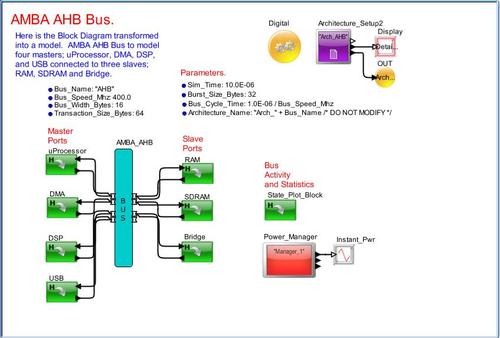

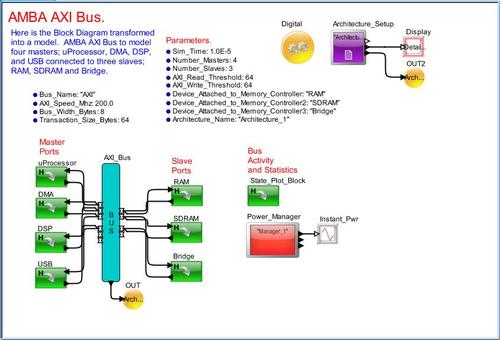

AHBバスの比較モデルを図2に、AXIバスの比較モデルを図3に示します。システム・モデルは、以下から構成されています。

1. マイクロ・プロセッサ、DMA、DSP、およびUSBマスタ・バス・ポート

2. AHB、またはAXIバス・アービタ

3. RAM、SDRAM、およびブリッジ・スレーブ・バス・ポート

4. 結果はプロット表示及び統計情報がウィンドウに表示されます。

図1: バス比較モデルのブロック図

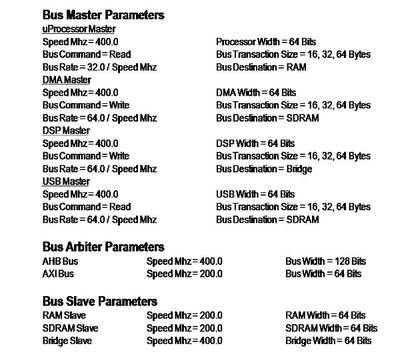

バス・マスタ・パラメータ

uProcessor

Master Speed Mhz = 400.0 Processor Width = 64 Bits

Bus Command = Read Bus Transaction Size = 16, 32, 64

Bytes

Bus Rate = 32.0 /

Speed Mhz Bus Destination =

RAM

DMA

Master Speed Mhz = 400.0 DMA Width = 64 Bits

Bus Command = Write Bus Transaction Size = 16, 32, 64

Bytes

Bus Rate = 64.0 /

Speed Mhz Bus Destination = SDRAM

DSP

Master Speed Mhz = 400.0 DSP Width = 64 Bits

Bus Command = Write Bus Transaction Size = 16, 32, 64

Bytes

Bus Rate = 64.0 /

Speed Mhz Bus Destination = Bridge

USB

Master Speed Mhz = 400.0 USB Width = 64 Bits

Bus Command = Read Bus Transaction Size = 16, 32, 64

Bytes

Bus Rate = 64.0 /

Speed Mhz Bus Destination = SDRAM

バス・アービタ・パラメータ

AHB

Bus Speed Mhz = 400.0 Bus

Width = 128 Bits

AXI

Bus Speed Mhz = 200.0 Bus

Width = 64 Bits

バス・スレーブ・パラメータ

RAM

Slave Speed Mhz = 200.0 RAM Width = 64 Bits

SDRAM

Slave Speed Mhz = 200.0 SDRAM Width = 64 Bits

Bridge

Slave Speed Mhz = 400.0 Bridge Width = 64 Bits

テーブル1: AMBA AHBとAMBA AXIのシミュレーション用パラメータ

図2: AHBバス比較モデルのブロック図

図3: AXIバス比較モデルのブロック図

結果

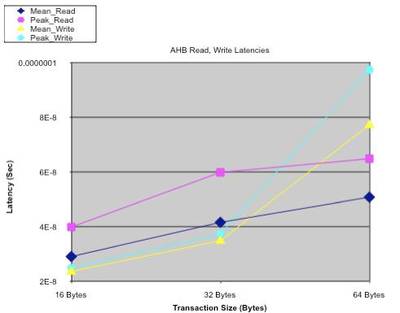

図4a: AHB

リード/ライト・レイテンシ

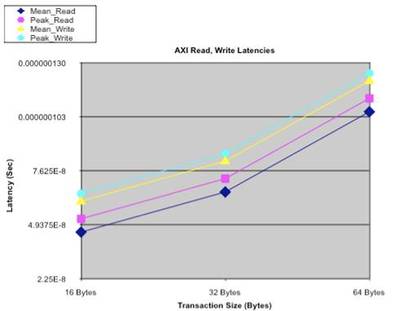

図4b: AXI

リード/ライト・レイテンシ

AHBのレイテンシは16バイト転送でAXIより低くスタートし、64バイト転送でもAXIを超えてはいません。しかしグラフの傾向より、Transaction_Size_Bytesパラメータを128バイト転送に変更して再実行すると、AXIバスの方が低レイテンシであることが予測できます。

注:Y軸のスケールは異なります。

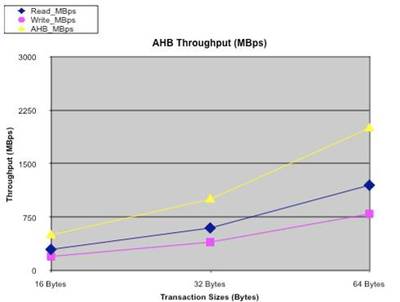

図5a: AHB

スループット

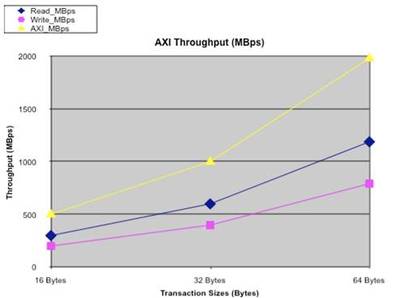

図 5b:

AXI スループット

スループットのプロットは、AHB,AXI共に同一のソース・トラフィック・レートでサイズも同じ場合、期待値も同一となっています。

注:Y軸のスケールは異なります。

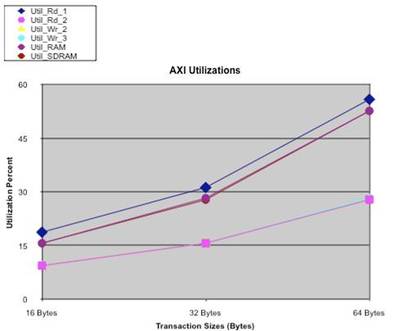

図 6a: AHB 利用率

図 6b:

AXI利用率

AXIバスは6つのチャネルを持つ事から、AHBバスの利用率は全ての転送サイズにおいてのAXIのチャネルより高くなります。AXIバスの利用率はAHBバスのスピード、バス幅において1/2で動作している為にAHBバスの物と一致しません。

注:Y軸のスケールは異なります。

解析

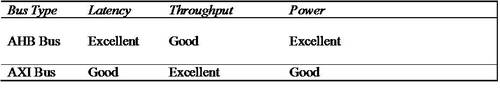

本システム・デザイン環境は2つのバスを比較するために必要なグラフを提供します。AHBバスでは64バイト転送まではレイテンシが低くなる事をレイテンシ・プロットで確認できます。

AHBバスは2倍のスピード、2倍のバス幅で動作していますので、同じトラフィック・ソースであればスループットは同一となります。利用率に関しては、AXIが6つのリード/ライト・チャネルを持つためAHBの方が高くなります。消費電力に関しては、与えられたスピードとバス幅に対して、単一のAHBバスはAXIバス1チャネルのおよそ4倍になります。AXIには6つのチャネルと追加チャネルがあるので、AHBバスに対して約1.5倍の電力を消費します。

デザイン・インパクト

このバス・モデルの比較結果より、いくつかのバス・デザインが考慮できます。

(1)バス・チャネルのピーク利用率を考慮すると、ピーク時の負荷が70%?80%の場合、バスは再設計なくトラフィックを追加可能です。

(2)例えばマイクロ・プロセッサからRAMへのクリティカル・パスのピーク・レイテンシを考慮した場合に、そのデザインはビデオ・フレーム・レートのような全体的なタイミング要求を満足できますか?

(3)バス・トポロジーの消費電力を考慮した場合、共有バスは消費電力を抑える事ができますか?

結論

AHBバスは与えられたトラフィック・レートやサイズにおいて最適なパフォーマンスを実現できます。AXIバスは同一条件下でのスループットは同一ですが、より多くのトラフィック容量をもつため、スループットを追加できるという点で優れています。電力消費の点では、同一プロセス技術を使うと仮定すると、AXIバスはAHBと比較して約1.5倍の消費電力が必要となります。

テーブル2: AMBA AHBとAMBA AXIのシミュレーション結果

Mirabilis Design Inc. CEO, Deepak Shankar

Deepak Shankar氏はシステム・エンジニアリング・ソフトウェアを提供するirabilis Design社の創設者であり、Shankar氏は20年以上に渡り、組込みシステ、半導体、リアル・タイム・ソフトウェアのアーキテクチャ探求に携わってきました。彼はMirabilis Designにおいて、システムの仕様検証の短縮化、アーキテクチャ探求を正確化、システム・エンジニアリング・プロセスの加速化に従事しております。

Deepak Shankar氏は以前、Cadence、Spincircuit、そしてMemcallにてテクニカル・マーケティングとマネージメント・エグゼクティブに従事。世界中のテクニカル・ジャーナルに40以上の記事を投稿、また様々なIEEEおよびその他の組織において講演を行っております。Shankar氏はクレムゾン大学にて電気工学修士、カリフォルニア大学バークレー校でMBAを取得、そしてコインバトール技術研究所にて電子通信の学士を取得しております。

Mirabilis Design

Field Application Engineer(フィールド・アプリケーション・エンジニア)中村幸二

(略歴)

工学院大学電気工学科にて学士を取得。通信装置の開発、FPGA/MCUのサポート業務を得てMirabilis DesignのField Application Engineerとして従事。