コントローラブル・オートメーションと相互運用性規格 SpringSoft社

コントローラブル・オートメーションと相互運用性規格:

次世代チップデザインのためのカスタム・デジタルレイアウトのスケーリング

SpringSoft社

SpringSoft社、Laker テクニカル・マーケティング・マネージャ、Rich Morse

Ryxis Technology社、アプリケーション担当副社長、Mitch Heins

大規模なデジタルIC(集積回路)設計におけるレイアウトには通常、高度に自動化された配置配線(APR)ツールが用いられています。カスタムレイアウトの代わりにAPRを使用するにはトレードオフを行う必要がありますが、APRがもたらすスピードや信頼性の高さは、多くのデザインにとって面積や性能の面で、はるかに重要な意味を持ちます。しかし、最高の性能や可能な限り最小面積といった条件のあるデザインは、未だにカスタムICレイアウト手法を使用して「手作業」行われています。

次世代のカスタムチップでは、複雑なルール、厳しい納期、設計のサイズや複雑さが、フルカスタム・デジタルブロックの設計方法をますます困難にしています。完全に自動化されたAPRフローは、必要なレイアウトや配線をインタラクティブに制御することができません。設計者は、高度に自動化されていると同時に、性能/速度/領域を最適化することができる制御可能なフルカスタム・デジタルICデザインフローを必要としています。

本稿では、消費者製品市場に身を置く大手ファブレス半導体会社のデジタルIC設計チームが、大規模かつ高性能な40nmプロセスで、どのように標準規格のツールを利用し、手作業によるレイアウトのメリットを維持するかを詳しくご説明します。このチームは、より生産性の高いカスタムICレイアウトフローを構築するため、さまざまなベンダーが提供するツールを使用できる、Si2(Silicon Integration Initiative)のOA(Open Access)インターオペラビリティ標準効果によって実現した機能を活用しています。

■カスタム・デザインでのコントローラブル・オートメーションの利点

多くのストレージ・ソリューションを設計する上で、設計チームは長年に渡ってアナログ/カスタム・デジタル設計にカスタムICレイアウト・オートメーションを利用してきました。アナログ設計者は常にカスタムデザイン・メソドロジを使用していましたが、デジタル設計チームが通常カスタム・デザインツール/フローを使用するのは、性能/パワー/速度/面積等の要件がAPRツールの能力を超えた場合のみです。

最適な性能と処理時間を実現するために、エンジニアは、最新のコントローラブル・オートメーション技術を採用し、より迅速かつ少ない労力でカスタム・デジタルデザインを生成します。このような最新技術には、高度に調整可能でプロセスに依存しないパラメータ化されたセル技術と、デザインスタイルの変更や結果品質の妥協をせずに、最高の性能と密度を実現するために必要なスピードと制御を提供するデバイス・レベルのフロアプランニング・ツールを使用できる、最先端SDLフローがふくまれている。

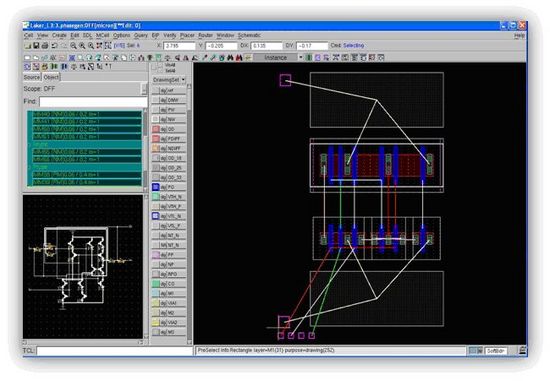

<図1>フライトラインは接続性を示し、ルール・ドリブンの手動配線を誘導

<図1>フライトラインは接続性を示し、ルール・ドリブンの手動配線を誘導

回路図から自動的に取り込んだ接続性を基に生成されたフライトラインを使用することにより、エンジニアは、内蔵されたルール・ドリブン・インタラクティブ配線を利用して、2GHzを超える厳しいクロックレート条件を満たすために、手作業でクリティカル・ネットを配線します。この性能レベルでは、個々のネットの配線は、その配線環境や他の配線、ネット、また他のレイヤーからも非常に影響を受けやすくなっています。これらの要素すべてのバランスをとるために、設計チームは、設計環境のすべての要素に対処する必要があります。手動配線時、設計チームは配線後、クリティカル・ネットのタイミングを抽出/評価し、目標値に達するまで変更を行うことができます。

■次世代カスタム・デジタル設計の課題に直面する

カスタムレイアウトと手動配線アプローチは性能要件を満たすことができましたが、次世代カスタム・デジタル・ブロックを適切な期間内で完成させることが難しくなってきています。

デザインの大規模化、複雑化するに伴い、レイアウト設計者は、深刻な配線問題に直面しています。また、配線チャンネルに設計余白(オープンエリア)が生じてしまい、ますます巨大化するブロック上で、手作業や自動Point-to-Point配線を行うために、密度に関して妥協する場合が出ています。性能目標をなんとか達成できたとしても、しばしば面積が拡大してしまい、コスト重視の市場傾向から見て理想的とは言えません。 加えて、設計の完成までに時間がかかってしまい、レイアウトをもう一つ試みることすらできません。

さらに、40nm製造プロセスに移行し、増加する性能条件に対応するために、さらなる課題が発生しました。このノードでは、ブロックがあまりに大きく(ネットも多く)なり、デザイン・ルールも、手動配線や既存の自動カスタム配線ソリューションを実行するには、難しくなっています。最先端プロセスに必要なディープサブミクロンでDRCクリーンかつDFMを考慮する配線が可能な大規模カスタム配線機能はありませんでした。

当初設計チームは、既に述べたように、レイアウト・エディタを使用してクリティカル・ネットを手作業で配線し、その後非クリティカル・ネットを完成させるために最先端DRCルールをサポートするAPRフローでデジタル・配線機能を使用するというハイブリッドフローの利用を試みました。残念ながら、複数のツール間を移行するという方法は逆効果でした。個々の操作がどんなに効率的であったとしても、カスタム・デザイン領域とデジタル・デザイン領域が共にうまく進むことはありませんでした。さらに、この手法はインタラクティブではなく、階層情報と接続情報双方を失ってしまいました。また、しばしば自動化された配線機能は、苦心して描いたクリティカル・ネットのいくつかを再配線し、膨大な手作業による編集や、自動配線機能によるさらなる配線、もしくはその両方が必要になりました。その結果、次善的ではあっても、許容できる結果で収束させるために、設計作業に6週間を費やしました。

非クリティカル・ネットであっても、自動配線を行うことで、スムーズに繰り返し作業が行え、設計チームの生産性は向上したはずです。また、APRツールに必要な部分的なプリ配線や細かいスペーシング制約を表す手段がありませんでした。同様に、これはカスタム・ブロック内の寄生的な相互作用に悪影響を及ぼし、労力を要する手作業による再配線や、長時間の再実行を何度も行う必要が生じます。

通常、自動化は生産性を向上させますが、この事例では、設計者が結果を制御することができなかったため、より難しい工程となってしまいました。事実、すべてのネットが配線されたレイアウトでクリティカル・ネットを手動で編集するのでは、はじめから手動で配線する場合と比べ時間がかかってしまいます。このデザイン・チームは、短期間で最適化結果を実現するには、制御可能な自動化が利用でき、階層、接続性、デザイン・インテグリティを保持できる異なる環境が必要であると結論を下しました。

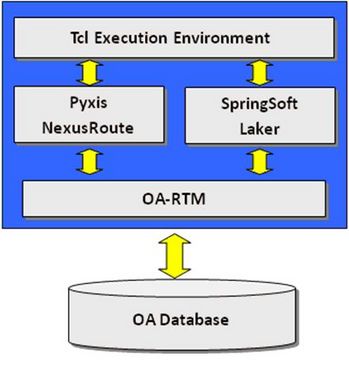

■インターオペラビリティが期間を短縮する

標準化団体Si2(Silicon Integration Initiative)は、近年カスタム・デザインの標準規格になった、OpenAccess(OA)と呼ばれるEDA(設計の自動化)ツール向けのインターオペラブル・データベースを実現しました。あまり知られていないOAの機能に、OA-RTM(OA Run Time Model)というものがありますが、これはEDAツール向けにメモリ内に納められたモデルで、OA上で駆動する際に使用することができます。つまり、全く異なるツールが、メモリ内に存在する設計データを、同時に操作することになります。OA-RTMを使用する複数のベンダーのツールを、単一ベンダーのツールのように、シームレスに動作させることができるのです。

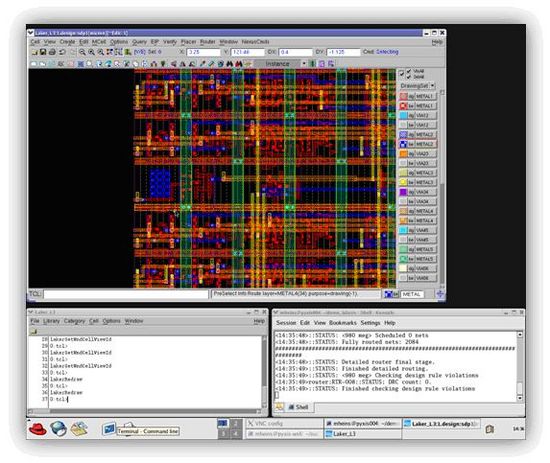

OA-RTMを使用することにより、OA上で駆動する既存のLakerカスタムレイアウト環境内で、Pyxis Technology社の新しい高性能カスタム・配線機能を使用することができます。この容量が非常に大きいカスタム・デジタル配線機能は、45nm以下でDRCに問題がなく、DFMを考慮する配線を行うことを、顧客が認証しています。あらゆるレベルの階層を配線し、手動で生成された既存のクリティカル・ネットを変更する必要がありません。カスタムICレイアウトシステムを利用する際、チップの領域を選択し、統合ラウタを使用して、ウィンドウ内で全てのネットを配線することができます。特定の配線チャンネルを指定するゲートウェイは全て、ブロッケージ、変更、修正済み/既存配線と同様、ラウタによってデータを変換することなく、もしくはディスクにデータを保存することなく、認識することができます。

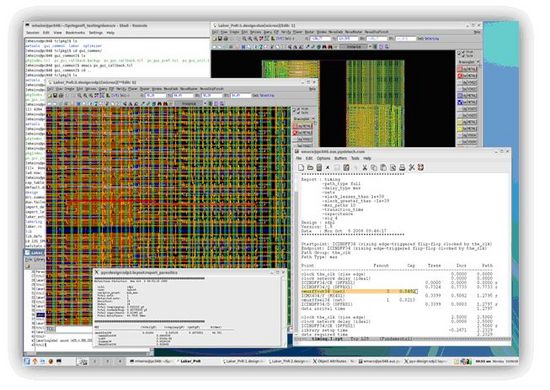

この相互運用可能なソリューションを適所で利用することにより、設計チームは、従来SDLメソドロジを利用するカスタム自動ICレイアウトシステムを使用していた場合と同様に、レイアウトを作成することができます。クリティカル・ネットの場合は、レイアウト・ツールを使用してトランジスタ・レベル配線を実行します。もしくは、別の方法として、クリティカル・ネットの配線をプリ・ワイヤを使いレイアウト・エディタで定義することができます。配線は様々なフェーズで実行されます。クリティカル・ネットの配線から始まり、(階層的に)優先グループ順に配線、もしくはブロック全体を一度に配線することができ、所要時間はわずか数分です。

また、カスタム配線機能に内蔵された抽出機能やタイミング・エンジンを利用して、寄生の相互作用や簡単なタイミングを迅速にフィードバックすることができます。この方法により、エンジニアは、配線トポロジがレイアウトにコミットする前に、「十分」である時点を決定することができます。さらに、このカスタムフローのスピードと制御性により、レイアウト素子の配置を迅速に評価し、最適な結果を実現することができます。また配線機能は、悪影響を及ぼす寄生効果を特定するために「ダミー・フィル」(配線の厚さのばらつきを抑制することを目的にデータ密度を増やすため、レイアウトに挿入される余分なメタル)を加え、ファウンダリによるダミー挿入が予期せぬ問題を引き起こすのを防ぎます。

EDAベンダーとの協業において、このような機能を高度に自動化されたカスタムレイアウト・システムと組み合わせることにより、設計チームは、レイアウトと配線を同時に最適化する、迅速な反復「what-if」解析が可能なソリューションを構築できるようになりました。配線、抽出、タイミング解析、修正、検証の繰り返しが可能になり、高性能を実現するために必要であった設計マージンを削減し、消費電力や面積を削減することができます。これらは全て、従来単一のレイアウトをインプリメントするために要した時間よりも短時間で実行することが可能です。

■ベンチマーク結果

今回参考例として挙げたベンチマークには、重要かつ高性能なブロックが含まれており、適当なソリューションを使用して収束するまでに、これまでは6週間かかっていました。このブロックの性能要件は、面積とパワー要件で矛盾があり、無事完成させることが非常に難しいものでした。配線機能の性能を確認するために、既存の配線は取り除きました。この設計をレイアウト・エディタでオープンし、ブロック全体を数分以内で自動配線しました。スタンダード・フローを再現するために、急遽追加バージョンを作成し、レイアウト・エディタを使用して手作業でクリティカル・ネットを配線し、その他のネットは自動配線機能を使用してインプリメントしました。自動配線シーケンスの際に、クリティカル・ネットの変更は行わず、DRC違反もありませんでした。

コンセプトの初期検証を経て、設計チームは、これまで完成に3?6週間かかっていた大規模かつ高性能なカスタム・デジタル・ブロックを、このフローを使用して、わずか1週間以内で作成できるという一貫した結果を出しました。これにより、設計チームはカスタム・ブロックの性能、面積、電力消費量の最適化により多くの時間をかけることができ、最終的に製品価値をさらに高めることができました。

***

著者について

Rich Morseは、SpringSoft社のカスタムICデザイン・プロダクト担当、技術マーケティング・マネージャー兼EDAアライアンス・マネージャーです。 (rich_morse@springsoft.com, 408-467-7888)

Mitch Heins氏は、Ryxis Technology社のアプリケーション担当副社長です。(mitch@pyxistech.com 512-637-0500)

お問い合わせ:株式会社スプリングソフト