PowerPro MG による SoC 設計時のメモリ消費電力削減 Calypto Design Systems

PowerPro MG による SoC 設計時のメモリ消費電力削減

Anmol Mathur, CTO, Calypto Design Systems

Lisa Minwell, Director Technical Marketing, Virage Logic

要約

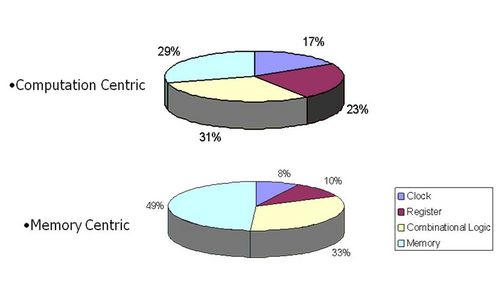

最新のSoC では、メモリがシリコン面積の50%以上を占有し、消費電力に至っては50-70%を占めるまでになっています。従って、最適なメモリ・アーキテクチャを選択し、最適化されたメモリ・アクセスになるように確実に制御することは、あらかじめ仕様で決められたSoC の総消費電力量に収める上で非常に重要です。

消費電力はすでに設計上の重要な検討課題になっているため、SoC 設計者がスリープ・モードや動的な電圧制御、周波数の可変化など、様々な電力削減技術を駆使できるよう、メモリ・ベンダは提供するメモリIP において、より電力効率の高いメモリ・アーキテクチャと省電力モードを提供しています。

しかしながら、メモリのスリープ・モードを活用したり、冗長なメモリの読み出しや書き込みが行われる場面を特定するためには、設計者は複数のクロック・サイクルに渡って、メモリと周辺の論理を解析する必要があります。

この論文では、ビラージロジック社から提供されている 40nm と32nm プロセス・ノード向けに設計されたメモリIP で利用できる主要な省電力技術について述べます。また、カリプト社のPowerPro MG ツールが、メモリへの無駄な読み書きを排除するため、あるいはメモリIP が持つスリープ・モードを制御するために、メモリ・ゲーティング論理を自動的に挿入することにより、メモリの動的消費電力と静的リーク電力の両方でかなりの削減を得ることができることを示します。

序論

ひとつのシリコン・ダイ上に多数の機能を統合するSoC は、今日、多くの電子機器の心臓部となっており、それは、システムの設計者が機能、性能、コスト、消費電力などの要求仕様を満たすことを可能にしています。プロセスの微細化に伴い、設計チームは、ライン・バッファ、FIFO などに加え、演算系コアがデータを格納するキャッシュなどとして機能するメモリを組み込み統合し、新たに利用可能になったシリコン面積を益々多くメモリへ使用するようになってきました。

オフ・チップ・メモリが使用される場合と比較して、これらの組込みメモリでは、特筆すべきシステム性能の向上と低消費電力化を得ることができます。そのため、最新の設計では、チップ面積の50%以上を組込みメモリで使用するようになりました。更に、これらのメモリの消費電力はSoC の総消費電力の50-70%を占めます(図1 参照)。このことから明らかなことは、SoC の消費電力を削減するためには、デザイン中の組込みメモリの消費電力を削減させることが必要不可欠だと言うことです。

SoC に組込まれるメモリの多くは、スタティックRAM(SRAM)かレジスタ・ファイルです。そのようなメモリにおける主要な電力消費源は以下の通りです。

? メモリ読み書き時に消費される動的電力、いわゆるスイッチング電力

? メモリに電源が入っているときは、読み書きにかかわらず常時周辺のロジックとコアのメモリ・アレイで消費される静的電力、いわゆるリーク電力

更にメモリの読み書き時に消費される動的な消費電力の要因は、以下のよう

に分類することができます。

? クロック・ネットワークの切り換え

? アドレスを解読する周辺論理回路

? メモリ・アレイのビット線

? 状態を変えるコア・メモリ・セル

? メモリ入出力にラッチをかけるアドレス/データのためのレジスタ

書き込み時だけに動的な電力消費が発生する通常のレジスタとは異なり、メモリは、書き込みの時だけでなく読み出しの時にも動的に電力を消費します。そのため余計な読み書きをなくすことは、メモリの動的消費電力に相当な削減をもたらします。これを達成するために必要とされるシーケンシャル・アナリシス技術については、後ほど述べることにします。

プロセス・ノードが40nm や32nm になれば、リーク電力は総メモリ消費電力の中でより重要な位置づけとなります。それは、先端の高速プロセスでは、総メモリ消費電力の40-50%に達するほどです。メモリ・ベンダは、メモリIP の中にメモリが使用中でないときに、リーク電力を減少させるいくつかの機能を提供しています。

現在、組込みメモリでいくつかのスリープ・モードが利用可能になっていますが、これらのモードを使用するには、スリープに入る際とそこから復帰させる際の信号を発生させるコントローラを作成する必要があります。更に、スリープ・モード中のリーク電力の削減は、メモリのスリープ・モードへの出入りで生じる動的消費電力とトレード・オフを考慮しなければいけません。

このことは実際に消費電力を削減するためには、一旦スリープ・モードに入った場合、ある最低限のサイクル期間はその状態に留まらなければならないことを意味しています。スリープ・モードへの遷移が、メモリ・アクセスがない期間だけで起こることを確実にすることは言うに及ばず、メモリの総消費電力において確実に削減できるようにスリープ・モード制御信号を生成する際には、デザインのもつ機能を複数のクロック・サイクルに渡って解析する必要があります。

消費電力に注意を払う設計チームは、不必要なメモリの読み書きを排除するために、メモリのゲーティング(イネーブル)条件の最適化のために最終的に数人月を費やすこともあります。このようなメモリ・ゲーティング論理の生成が難しい理由はいくつかあります。第一に、メモリ読み出しや書き込みが冗長であると判定するために、設計者は複数のパイプライン・ステージに渡ってデザインの動作を解析する必要があります。さらに最終的なゲーティング条件を組み立て、それをRTL に実装するためには、しばしばデザイン中の他の部分からの信号を活用する必要があります。これは根気のいる作業で、かつ誤りが混入しやすい作業です。実装されたゲーティング論理の正しさを確かめるためには、更なる努力を必要とします。最後に、新しいゲーティング条件を付加する際には、付加される論理が消費する電力、タイミング、および面積への影響を注意深く解析する必要があるのは当然のことです。

カリプト・デザイン・システムズ社から提供されるPowerPro CG とSLEC は、デザイン中のレジスタに新しいシーケンシャル・ゲーティング論理の生成を自動化し、かつ、その条件の機能的な正しさまでも包括的なシーケンシャル等価性検証で証明する自動化ソリューションを提供します。

この論文では、PowerPro MG について述べてゆきます。PowerPro MG は、最適化対象のRTL デザインに対してシーケンシャル・アナリシスを実行し、組込みメモリへの不要な読み書きを防ぐ論理を自動生成します。これによりメモリの動的消費電力を削減し、またメモリ・ベンダが提供するライト・スリープ・モードを制御する論理を自動生成しリーク電力も削減します。カリプト社は、PowerPro MG の開発において、メモリの消費電力削減の機会を最大限に得るために、業界の主要メモリIP ベンダであるビラージロジック社と提携しました。

ビラージロジック社メモリ IP のパワー・モード

ビラージロジック社製SiWare メモリ・コンパイラは複数の先進的な電力管理モードを持ち、SoC 設計者が重要な設計の目標である電力仕様を満たすだけでなく、それを上回る実装をも可能にするための柔軟性を提供します。SiWare メモリ・コンパイラの製品ラインには、1 ポートとデュアル・ポートのSRAM、1 ポートと2 ポートのレジスタ・ファイル、ROM、および大容量の1 ポートSRAMコンパイラを有する高速、高密度アーキテクチャを含んでいます。これらのコンパイラは、それぞれに動的な電力管理、歩留まり、面積、および性能トレード・オフのための複数のコンパイル時オプションを提供します。

SiWare メモリ・コンパイラはライト・スリープ、ディープ・スリープ、およびシャット・ダウンを含む先進の電力管理モードを提供します。これらのモードは、バイアス技術と統合電源スイッチの組み合わせで静的消費電力を減少させ、主な組込みプロセッサの電力管理モードと適合するように作られています。

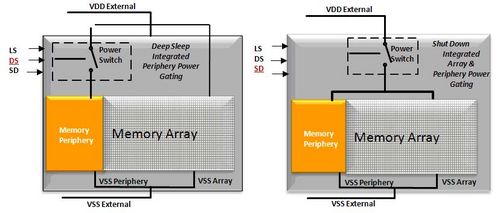

ライト・スリープの間、メモリ・アレイはソース・ダイオードの実装によってバイアスされています。また、きめ細かなパワー・ゲーティングは周辺回路部でも実装されます。仮想の電源ネットは短く、セルの中に隠されているためグラウンド・ノイズ耐性は弱くはありません。また、この実装方法ではキャパシタンスが限られているため、ウェイク・アップ時のレイテンシーと突入電流は小さくなます。このモードは、独立した制御ピンで有効することできます。

ディープ・スリープとシャット・ダウンの両モードは、メモリ・インスタンス内に、周辺またはメモリ・アレイおよび周辺の両方を停止させる内部スイッチを組込みます。具体的には、ディープ・スリープ・モードの間、このスイッチはメモリ・アレイへの電源供給は維持しながら、周辺回路への電源供給を遮断します。メモリ・アレイはライト・スリープ・モードと同じ実装でソース・バイアスされています。このためメモリ・アレイの内容は保持されます。シャット・ダウン・モードでは、このスイッチはメモリ・アレイと周辺の両方への電源供給を遮断します。メモリ・アレイの内容はこのモードでは保持されません。

図2:ビラージロジック社製SiWare 統合パワー・ゲーティング

図2:ビラージロジック社製SiWare 統合パワー・ゲーティング

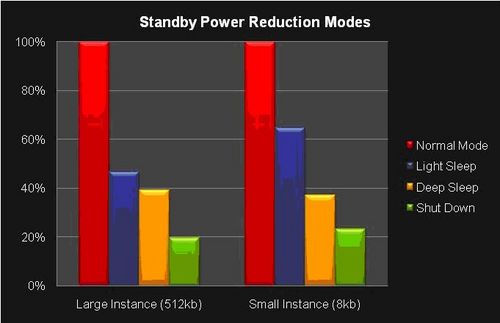

これらの電力管理モードを適用する利点は特筆すべきものがあります。ライト・スリープは、高速ウェイク・アップでスタンバイ電力の最大50%を削減します。ディープ・スリープはメモリ周辺をシャット・ダウンし、アレイのデータを保持したままソース・バイアスするスイッチを組込みます。このモードはスタンド・バイ電力を最大70%まで節減します。一方、シャット・ダウンはアレイと周辺の両方への電力を遮断します。シャット・ダウン・モードは、メモリ・アレイ状態を保持しませんが、スタンバイ電力を最大90%まで削減します。すべてのモードにおいて出力が管理されます。ライト・スリープでは、出力は最後の状態を保持します。ディープ・スリープとシャット・ダウン・モードでは、出力はローに固定されます。

図3:SiWare メモリ・コンパイラはスタンバイ電力削減を標準化

図3:SiWare メモリ・コンパイラはスタンバイ電力削減を標準化

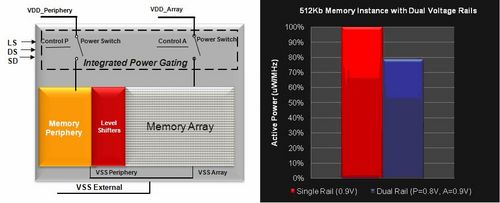

SoC 設計では、複数の電源の使用が増加しています。メモリのための電圧低減はビット・セルによって制限されます。ファウンドリによって供給されるビット・セルは、保持のための最低電圧の仕様があります。この最低電圧(VDDMIN)は公称電圧VDDNOM より10?20%少ない電圧に制限されるかもしれません。バッテリーによって駆動されるアプリケーション用に設計した多くのSoC は動的消費電力を最小にするために電圧を下げることによって大きな利益を得ます。メモリ内のアレイと周辺回路の電源を分離することにより、設計者はメモリ・インスタンスの周辺回路の電圧をさらに下げながら、アレイ内のデータを保持するためのビット・セル仕様を満たすことができます。メモリはタイミングのクリティカル・パス上にある場合が多いため、メモリ・インスタンス内にレベル・シフタ、クランプ等を持つことはタイミング制約を満たすことに大いに助けになります。SiWare メモリ・コンパイラは電源スイッチに関連する内蔵レベル・シフタを含んでいます。

図4:SiWare メモリ・コンパイラにおける2 電源実装と40nm G のための動的消費電力の削減例

図4:SiWare メモリ・コンパイラにおける2 電源実装と40nm G のための動的消費電力の削減例

冗長なメモリの読み書きを最適化

最新の SoC はその設計上、複雑なデータ・パイプラインを持ち、様々な演算だけでなく、プロセッサ・コア上のソフトウェアとも相互に作用し合います。その際にメモリは、データ・パイプラインにおける計算の途中結果を格納するために使用されます。また相互作用する際のバッファとしての役割も果たします。更に頻繁に読まれるデータを格納するためのキャッシュとしての役割も果たします。

局所的視点に立った場合、メモリへの読み書きが必要に見える場合であっても、デザイン中の機能モードや複雑な制御シーケンスによっては、それらは最終的には必要ではないかもしれないというケースがあるかもしれません。そのような不必要なメモリ・アクセスを取り除くと、メモリの動的電力消費量をかなり削減できることになります。

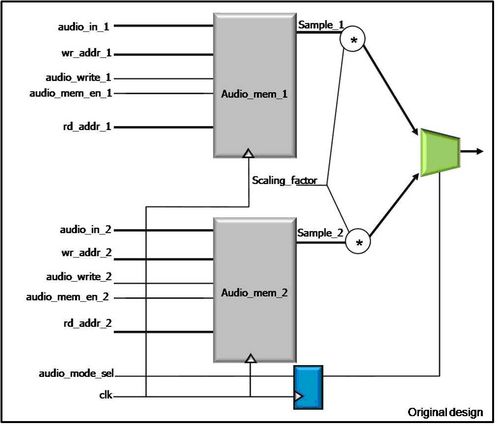

図 5 中の上側に示されるデザイン・ダイアグラムについて考察してみます。このデザインは、2 つのオーディオ・ストリームを処理します。audio_mode_sel 制御信号に基づき2 つのストリームを切り替えます。これを制御する方法としては、1 つのオーディオ・ストリームの優先権に基づいて行うこともできますし、入って来るデータのサンプリング・レートと要求されるサービスの質に基づいて、いつオーディオ・ストリームを処理するかを決定する何らかの複雑なアルゴリズムに基づいて行うことも可能です。

ここで、audio_mem_2 の出力はaudio_mode_sel の信号が1のときにだけ使用されていることに注意して下さい。しかし、両方のメモリは読み書きの制御を簡素化するために、設計者によっていつもイネーブル状態になっています。その結果、オーディオ・ストリームが選択されるときだけ、メモリからの出力データが実際の演算に使用されますが、両方のメモリはそれとは関係なく、毎サイクル、読み出しがおこなわれるか、書き込み操作が行われています。

この場合、デザインの処理シーケンスを解析すれば、audio_mode_sel が0 にもかかわらず、audio_mem_2 からデータの読み出しが行われているならば、その読み出し操作は冗長(無駄)であると見つけることができます。同様に、audio_mode_sel が1 で、audio_mem_1 からデータの読み出しが行われているならば、その読み出し操作も冗長であるということになります。この解析結果を

使用してRTL を最適化すると、これらの冗長なメモリ読み出しがおこらないような論理を追加したメモリ・イネーブル信号を、2 つのメモリに対して持つようなRTL となります。

図5:元のデザイン(上)とPowerPro MG の生成した可観測性(OBS;observerbility)ベースのリード・ゲーティング・ロジック(赤色)が挿入された最適化後のデザイン(下)

図5:元のデザイン(上)とPowerPro MG の生成した可観測性(OBS;observerbility)ベースのリード・ゲーティング・ロジック(赤色)が挿入された最適化後のデザイン(下)

PowerPro MG は、メモリから読み出された値が論理後段の処理で使用されないような条件を探索するためにシーケンシャル・アナリシス・エンジンを用いて自動的にデザインを解析します。そして、発見された冗長な読み出し操作を無効にするためにメモリ・イネーブルにゲーティング論理を追加します。この最適化は可観測性(OBS; observerbility)ベースのリード・ゲーティングと呼ばれます。上の

図5 の例では、可観測性ベースのゲーティング条件は、順序回路中の1 サイクル前にさかのぼって伝播されています。しかし、より複雑なデザインにおけるゲーティング条件は、順序回路中の制御シーケンスを何サイクルにも渡り伝播させることによって、はじめて余計なメモリ読み出しを遮断するためのゲーティング条件を生成出来るようになります。その結果として、メモリの動的消費電力の削

減が得られるのです。

多くのメモリは、データが書き込まれるよりも読み出される機会の方が多くなることが一般的です。1 つの例は、デジタル・フィルタで使用される係数を格納するメモリです。そこでは同じアドレスに対し、書き込み処理を挟むことなく繰り返し読み出し操作が行われます。このようなシナリオでは、最初の読み出しを行った後では、そのメモリの同じアドレスへの読み出しが全ての冗長である場合があります。その際には、これらの読み出し操作を無効化することができ、そのためのリード・ゲーティング論理を追加するために、メモリのリード・アドレスとリード・イネーブルの持続性(STB; stability)を基に行われます。そのため、このような最適化は持続性ベースのリード・ゲーティングと呼ばれます。

メモリ・イネーブルに新たなゲーティング論理を挿入する際に考慮すべき重要な点、さらにそれらに対するPowerPro MG の対応に関して、次のようにまとめることができます。

? メモリ・イネーブルの信号は、よくタイミング・クリティカル・パスになっている場合があります。従って、新たな論理を追加するとタイミング違反を引き起こす場合があります。PowerPro MG は、タイミングへの影響を最小限に抑えるために、可観測性ベースもしくは持続性ベースのゲーティングに必要な論理を最適化します。

? メモリ・ゲーティング論理を作成するオーバー・ヘッドが大きければ、メモリ・アクセスを止めることによって削減される消費電力は、ゲーティング論理自体による消費電力の増加で相殺されるかもしれません。PowerProMG は、冗長なメモリ・アクセスを止める能力を落とすことなく、ゲーティング論理そのものの電力コストを下げるための最適化を行ないます。

? 新しいゲーティング論理に含まれるフリップ・フロップは、回路中のリセット・シーケンスからのどのような干渉も避けるために、回路が立ち上がるとき、適切に初期化される必要があります。PowerPro MG は、リセット期間中の回路動作を適切に保つための論理を自動的に挿入します。

メモリのスリープ・モードの利用

メモリへのバースト・アクセスが頻繁に起こり、その結果として多くのメモリ・アクセスがある期間と、逆にメモリ・アクセスを必要としない期間が分散して存在します。また多くの設計ブロックでは、論理の大部分が動作しない特別なモードを持っています。そのようなアイドリングの期間の電力消費の主な原因はリーク電力です。先に述べたように、メモリ・ベンダは、設計ブロックがアイドリングの場合、設計者がメモリをスリープ状態にできるように組込みメモリIP にいくつかのスリープ・モードを提供しています。そのようなスリープ・モードは、メモリ中の様々な部分の消費電力を止めることによって、実装されます。

有効にスリープ・モードを利用するためには、次に示す主要な問題ついて考慮する必要があります。

? 仕様上の機能が正しく動作することを確実にするためには、メモリ・アクセスが全く起こらない時だけメモリをスリープさせなければいけません。さらに、タイミング仕様に従って、メモリ・アクセスが行われる数サイクル前には、メモリをスリープ・モードから復帰させる必要があります。スリープモードからの復帰に必要なサイクル数は、メモリのどのくらいの部分がその特定モードの間に止められているかによって異なります。スリープ状態が深ければ深いほど、スリープ・モードからの復帰には時間が長く

かかります。これは、スリープ・モードを制御する論理が、メモリ・アクセスがいつ起こるのか、すなわち対象ブロックの機能的なシーケンス特性を把握しなければならないことを意味しています。

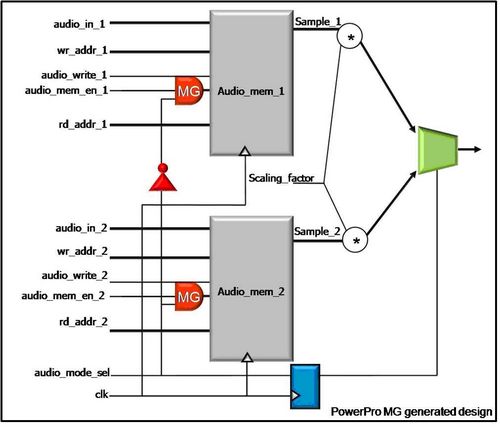

? メモリをスリープ・モードに設定したり、そこから復帰させたりする操作には動的な電力消費を伴います。そのためにメモリの総消費電力を削減するには、スリープ・モードに入れてからある最低限のサイクル期間はそに留まる必要があります。図6 は、総消費電力を削減するために必要となる最低限のスリープ・サイクル数が、メモリの動作周波数とメモリ・イネーブルの確率によってどのように変化するかを示しています。また、それはメモリが高速アクセス向けに最適化すべきかどうかについてを示した関数とも言えます。より高速なメモリは、リーク電力の対動的電力比がより高くなる傾向があります。

シャット・ダウンやディープ・スリープ・モードのようなメモリ省電力モードは、ウェイク・アップ時により長いサイクル数を要します。そのため、設計者はメモリの状態を保持すべきかどうかを決める必要があります。その結果として、シャット・ダウンやディープ・スリープ・モードは、設計のブロック・レベルでアイドリング状態やスリープ状態のような設計アーキテクチャに基づく状態をうまく適応することで、最も効果的に制御されることができます。

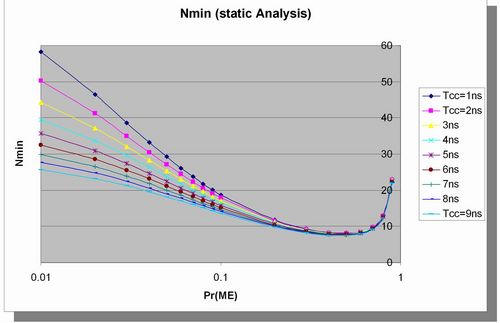

ライト・スリープ・モードは、より細かな粒度で活用ができます。PowerProMG は、自動的にライト・スリープの制御論理を追加することにより、メモリ消費電力の最適化を行います。通常、ビラージのメモリでは、ウェイク・アップに1 サイクルが必要ですので、メモリ・アクセス前に確実にライト・スリープ・モードから復帰させるために、その制御論理はアクセスが起こる1サイクル前には、それを予測し、メモリをスリープから復帰させます。さらに、PowerPro MG によって追加されたライト・スリープ制御論理は、メモリの総消費電力を削減するために必要なサイクル期間、ライト・スリープ・モードに留まることを確実にします。

図6:メモリの総電力削減に必要なライト・スリープの最小サイクル期間をメモリ・アクティビティと動作周波数による関数で表したグラフ

図6:メモリの総電力削減に必要なライト・スリープの最小サイクル期間をメモリ・アクティビティと動作周波数による関数で表したグラフ

PowerPro MG はメモリ読み出しのゲーティングを行うことによって、ライト・スリープを活用できる機会を増やします。これはメモリの不活性頻度とその期間を増加します。図7 は、PowerPro MG がどのようにライト・スリープ・モードを管理するコントローラを作成するかを、それにより生成される関連信号の波形と共に示しています。

図7:ME(Memory Enable)とライト・スリープ・モードを制御するためにPowerProMG が挿入したメモリ・ゲーティング論理(上)とライト・スリープからの復帰に必要な1 サイクルを含むLS(Light Sleep)とME との関係(下)。クロック周期3 と5 の間では、ME=0 ですが、PowerPro MG コントローラはメモリをライト・スリープに入れないことに注意して下さい。しかし、クロック周期X とY の間では、ライト・ス

図7:ME(Memory Enable)とライト・スリープ・モードを制御するためにPowerProMG が挿入したメモリ・ゲーティング論理(上)とライト・スリープからの復帰に必要な1 サイクルを含むLS(Light Sleep)とME との関係(下)。クロック周期3 と5 の間では、ME=0 ですが、PowerPro MG コントローラはメモリをライト・スリープに入れないことに注意して下さい。しかし、クロック周期X とY の間では、ライト・ス

リープ・モードにすることでトータルで省電力化できます。また、クロック周期Yでライト・スリープ・モードから出ることによって、クロック周期Y+1 でME=1 になる時にはメモリにアクセスできます。

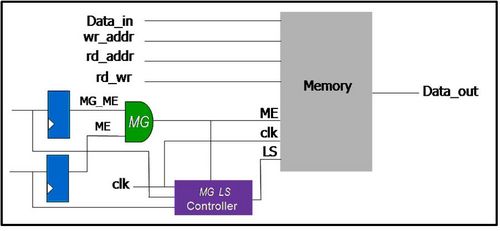

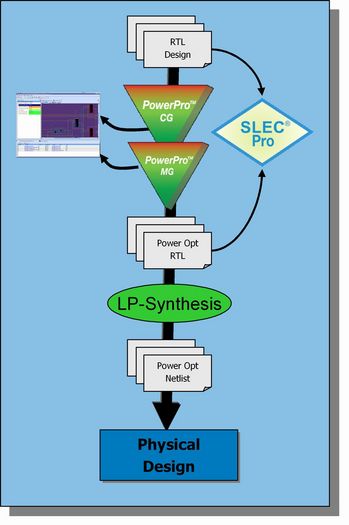

PowerPro MG を利用する設計フロー

PowerPro MG は、SoC 設計グループのRTL 設計からの論理合成へのフローにシームレスに適合します。さらに、設計の非メモリ部分へシーケンシャル・クロック・ゲーティング条件を挿入するためにPowerPro MG と共にPowerPro CGを使用することできます。PowerPro MG とPowerPro CG の両方のライセンスを持っている顧客は、同じPowerPro シェルの中からCG とMG の最適化の両方を起動することができます。

図8:PowerPro MG とPowerPro CG を論理合成のプリ・プロセッサとして使用するフロー

図8:PowerPro MG とPowerPro CG を論理合成のプリ・プロセッサとして使用するフロー

PowerPro MG とPowerPro CG のどちらの最適化処理においても、シーケンスの変更、つまり順序回路としての変更を伴います。このためPowerProMG/CG によって生成された最適化されたRTL を、元のRTL に対して機能的に等価であることを形式的に証明するためには、一般的な等価性チェッカーを利用することができません。カリプト社のSLEC は、回路内部とインタフェースの両方で異なるシーケンスを持つ2つの設計間の機能的等価性について検証することができる業界唯一のシーケンシャル・ロジック等価性チェッカーです。PowerPro MG とPowerPro CG は、等価性検証のためにSLEC の実行に必要なスクリプトを自動生成します。

また、PowerPro MG/CG は、下流工程の論理合成や物理的実装フローへの統合を容易にするために他のいくつかの機能を提供します。これらの特徴は以下の通りです。

? ECO フロー: ECO があった場合、PowerPro MG/CG をECO モードで実行せることができます。このモードでは、元のRTL 上にPowerPro が挿入したゲーティング論理の中で、ECO 後においても機能的に有効であるかどうかを判定し、無効化しなければならないゲーティング論理をECOファイルとして生成し報告します。

? PowerPro MG/CG によって挿入されたゲーティング論理の可視化のためにPowerPro Analyzer が提供されます。

ケース・スタディ

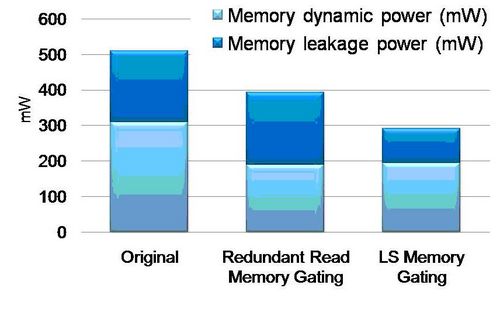

ネットワーク系チップの設計ブロックを例に、PowerPro MG を利用することで達成できる省電力化について説明します。このブロックには14 個の組込みメモリがあり、これらのメモリは、総ブロック面積の約40%を占め、総ブロック消費電力の50%を占めます。また、動的消費電力と静的リーク電力間の比率は、60%と40%です。この数値は、サード・パーティーの論理合成ツールと合成後の消費電力予測ツールを用いて算出されました。また、これらの数値は、この顧客が提供した、対象ブロックの代表的な動作時におけるスイッチング・アクティビティ・ファイル(SAIF)に基づいています。

この設計ブロックに対してPowerPro CG とPowerPro MG を実行すると、PowerPro CG は非メモリ設計部分で、動的な消費電力を15%減少させることができました。PowerPro MG は、14 個のメモリのうち5 個で可観測性ベースのリード・ゲーティング可能な箇所を発見しました。これに対する最適化により、メモリの読み出し頻度は、動作期間中の50%から3%までに減少しました。その結果は、40%のメモリの動的消費電力の削減として表れました。さらに、ライト・スリープ・メモリ・ゲーティングが適応されました。ライト・スリープ制御論理は、14 個の全てのメモリへ挿入され、メモリからのリーク電力は全体で55%の削減となりました。その結果、総メモリ消費電力は約45%減少しました。また対象ブロックの消費電力全体では約30%の削減が得られました。

図 9 は不要なメモリ読み出しの削除とその後のライト・スリープ・コントローラの挿入の結果として、設計ブロック中の全メモリにおける動的消費電力と静的リーク電力の削減の様子を示しています。

図9:PowerPro MG で逐次最適化が実行される際のメモリ消費電力量の推移

図9:PowerPro MG で逐次最適化が実行される際のメモリ消費電力量の推移

結論

組込みメモリにおいて、不要なメモリ・アクセスを取り除いたり、省電力モードを利用するためには、複数のパイプライン・ステージに渡る回路動作の連続した分析を必要とします。このような局所的ではない可観測性、持続性の条件の分析とその最適化を設計者が手作業で行うことは非常に困難であり、かつ検証にも時間と労力を要するため、メモリの消費電力を削減ができる余地は多くのRTL設計中に残されています。

PowerPro MG はメモリ最適化のためにシーケンシャル・アナリシス、消費電力 - タイミング - 面積間のトレード・オフ、および最適化されたRTL の生成を自動的に行います。SLEC は、最適化後のRTL に対する包括的な形式的検証を提供します。PowerPro MG とPowerPro CG の組み合わせは、RTL 設計の全体での自動的な低電力最適化を行う環境を提供します。

参照資料

Ramachandran, Venky. "Minimizing Power Consumption in RTL Designs Using Sequential Clock Gating and Low-Power Synthesis." EDA Design Line. 26 May 2009.

<http://edadesignline.com/howto/digitalic/

英語版原文 題名

Memory Power Reduction in SoC Designs Using PowerPro MG

日本語訳、補足

山本 修作、Japan Technical Account Manager & Business Development、Calypto Design Systems, Inc.

竹尾 啓亮、テクニカル・ディレクター、ビラージロジック株式会社

発行

カリプト・デザイン・システムズ?

横浜市港北区新横浜2-3-4 クレシェンドビル9F

電話: 045-470-2070

EMAIL: calypto_info_japan@calypto.com