人が共に働く時、EDAツールも共に駆動する SpringSoft社

人が共に働く時、EDAツールも共に駆動する

SpringSoft社‐Richard Morse著

2006年の終盤に、エレクトロニクス・デザイン・オートメーション(EDA)・ソフトウェア企業5社が集まり、インターオペラブルPCellライブラリとこれらを使用するためのオープンなインフラの構築と提供を目的に、協力することで合意しました。この"proof-of-concept PCell Library"は、6ヶ月以内で開発、リリースされ、その後1年以内に開催された「The fall 2007 Si2 OpenAccessコンファレンス」で異なるEDA企業5社の8つの異なるツール上で動作することが公開されました。それ以来、このライブラリは1,000回以上もダウンロードされています。このような、あり得そうもない競合会社が集まっての成功は、集積回路(IC)設計ツールのサプライ・チェーンにとっては、協業することがメリットになることを表しています。

■従来の方法

歴史的に、ICデザイン・フローは、膨大なソフトウェア・スクリプトや複数のデータ・フォーマット変換を使用することによって、実行可能なデザイン・メソドロジや "フロー"を繋ぎ合わせたソフトウェア・ポイント・ツールの集合体でした。この方法は、互換性を持たないツールを使いより効率的なデザイン"フロー"を作るために、単独の"孤立した"アプリケーション専門知識をまとめたもので、これまで長い間使用されてきました。この方法は、場合によっては、ソフトウェア・ツール・ベンダーが自社のツール群に対しても採用していました。EDAソフトウェア・ツール1ドルに対して、その統合に2ドルから4ドル、あるいはそれ以上の費用がかかると言われています。半導体製造においても、大抵の場合はハードウェア・ツールで定義されるのですが、ウェハー工程が別々の工程を繋ぎ合わせたもので、ウェハー・ボートが手作業でマシンからマシンへ移される場合と類似点がありました。

最終的には、マシン・インターフェイスの標準化、ウェハー処理の自動化、ファクトリ・オートメーション・ソフトウェアを必要とし、実行した顧客が、多大な効率化が図ることができました。装置業界のサプライ・チェーンも、共に協力して標準化を行い、サプライヤ、ファブ、顧客の誰もがこの協業から恩恵を得られるようになっています。

今日、複数のツールからなるデザイン・フローの作成支援を行うEDAスタンダードが、多く存在しています。しかしながら、互いにシームレスに動作するインフラの提供は、あまり十分ではありません。Interoperable PDK Library(IPL)Allianceを自称するグループ・ワークは、カスタムIC設計に対してオープンな環境を作ろうというグループ協業の積極的な活動の一例です。

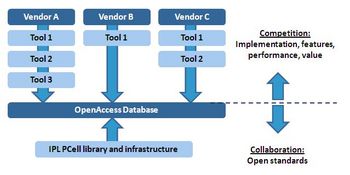

IPL Allianceの設立メンバーであるAWR社、Ciranova社、Silicon Navigator社、SpringSoft社、Synopsys社が初めて一同に介して行った最初の仕事は、EDAデータベース向けにSilicon Integration Alliance (Si2) のOpen Access (OA)を スタンダードとして採用することでした。過去EDA企業は、必要に迫られて、あるいは自社独自の見解が自社製品に競合力を与えると考えていたために、自社独自のデータベースを開発していました。外部のベンダーがこのような特定企業所有のデータベースにアクセスする場合は、特定の付加価値のあるサードパーティ・ツールにだけアクセス権限が与えられ、ツール間で情報を受け渡すために、一般にデータ変換を非公開にしていました。小さな新興企業が、しばしば革新的な技術を発表したため、合併した会社、あるいは買収によって技術を獲得した会社では、同じデータベースを使用しないツールばかりで製品ポートフォリオが構成されてしまうことが多々ありました。もちろん、この問題は、異なるベンダーのツールを使用して業界最高水準のデザイン・フローを作ろうとする顧客や、自社ツールと市販ツールを統合しようとする顧客にとっては、さらに大きな問題になっていました。

■オープン・データベースの課題

他のグループの数十年に渡る努力が不成功に終わった後、2001年にSi2はオープンなEDAデータベース・スタンダードを定義/開発するために、さらにもう一つの委員会を主催しました。数年後に、OpenAccess(OA)データベースがSi2に寄付され、EDAツール間のインターオペラビリティの未来はついに視野に捉えられました。当初、競争的懸念があったにも関わらず、今日、全てのSi2メンバーはOAを利用することができ、少なくともカスタム設計とアナログ設計に関しては、OAは急速に標準的EDAデータベースとして定着してきています。現在では、EDA業界の売り上げの80%以上を占めるEDA企業と、多くの主要顧客からなる約34社の提携メンバーで構成されています。このOA提携メンバーの数が、設計で成功を収める上での協業に大きな価値があることを物語っています。しかし、OAスタンダードの採用がいいスタートを切ったとはいえ、まだ十分とは言えません。Linuxのようなオープンなオペレーティング・システムのように、オープン・データベースの実現が、必ずしもオープンな設計環境というビジョンを達成したこと表しているわけではありません。確かに、OAが多くの企業で採用されたことは、インターオペラブル環境を作るという努力において、大きな出来事として記憶されるでしょう。しかし、OpenAccessデータベースが設計側の標準化に対して基本的なインフラを提供する一方で、広範囲にわたって採用されるには、未だにIPL Allianceがターゲットとしている主要機能要件に左右されています。

■インターオペラブル・ファウンダリ・デザイン・キット

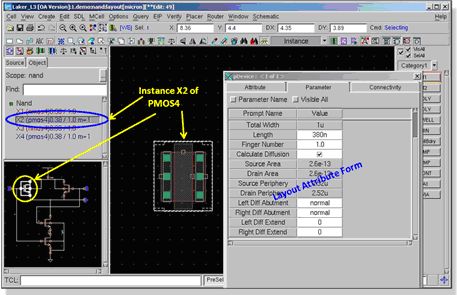

このような要件の1つに、全てのファウンダリ・フィジカル・デザイン・キット(PDK)で重要な要素であるPCellライブラリがあります。PCellは、アナログとカスタム・デジタル回路設計で使用されるパラメータ化されたセルで、特定の次元変数(パラメータ)を異なる値に置き換えることによって、多くの固定セルの代わりに使用することができます。例えば、NMOSトランジスタ向けの1つのPCellを、特定の位置に配置した"インスタンス"に対して、ゲート長のパラメータを特定の値に置き換えることによって、簡単に、デバイス・サイズの制限を受けることなく、固定セルの代用として使用することができる。加えて、変数の代わりに式や機能を用いる等、PCellに関連した最先端機能があり、必要な相関性を維持することが可能です(例えば、拡散幅が変化した場合、ポリ・エンドキャップを自動的に拡張します)。さらにまた、いくつかのPCellは、特定の状況に応じて適切な値を得るために、シミュレーションからの入力に、自動的に適応することができます。また、主要な構成要素であるライブラリや機能が全てインターオペラブルになるまでは、オープン・データベースの効果だけでは、とりわけアナログ設計やカスタム・デジタル設計に対しては、かなり限定されてしまいます。

図1.: PCellと属性フォーム

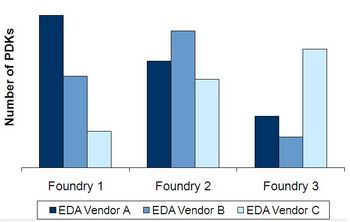

アナログ回路は、特定の値を使用して、特定のデバイスと一致するシンボルを使用するスケマティック・フォームで設計されます。今日、レイアウト設計者は、手作業で一つずつ図形を描く必要はなく、最先端のレイアウト・ツールが配置効率のために複数のデバイスをマージし、回路パラメータに正確な値でDRCコレクトなPCellレイアウトを自動的に生成できること知っている。セル同士の接続は、スケマティックで指定され、Routerはレイアウト・ツール環境内で、手作業もしくは自動で、正確に配線(ワイヤリング)できる様々な手段を提供します。事実、ハイエンドのレイアウト・ツールの全てに、この方法で動くPCellメカニズムがあります。問題は、今日使用されているほとんどのPCellが、特定のベンダーによる互換性のない言語で書かれているということです。他のベンダー向けに他の言語でPCellを提供し、確実に本来のバージョンとして正確に機能させるこを保証するには、ファウンダリ、顧客、EDAベンダーに大きな負荷がかかります。顧客は、好む好まないに関わらず、経済的理由からファウンダリPDKでサポートされたこのようなツールだけを使用することは、あまりありません。図2では、ある顧客がファウンダリ3社とEDAベンダー3社のツールを使用していますが、各テクノロジ・ノードに対して、9つのPDKが必要になる可能性があります。オープン・スタンダードを使用することで、このPDKの数を3つにまで減少することができ、最先端ツールを使用することで、1つのPCellライブラリを共有できるようにさえなるかもしれません。

図2: PDKマトリックスのカスタマ・ビュー

■協業する人々

これまで述べてきた、またそれ以上の理由から、IPL Allianceの創業者達は、共に開始したOAの残りのインフラを完成させ、この作業を完了させることに意欲を燃やしました。複数の企業からなるこの協業の一翼を担う参加企業は、誰もがこの試みの多くが失敗し、多くの共通結果がパワーポイントのスライドとなり、多くのことが約束どまりになってしまうであろうと考えています。このことから判断すると、これら5社によって始められ、現在約20社によってサポートされているIPL Allianceは、急速なスピードで効果を表しています。前述のサンプルPCellライブラリは、2007年4月にリリースされました。マルチベンダー、マルチツールによるインターオペラビリティ・デモが、2008年のDACで公開されました。2009年7月には、TSMCが包括的な65nmアナログ設計であるRF PCellライブラリを含む、業界初のインターオペラブルPDK(iPDK)の提供開始を発表しました。今年の2月に、IPLはリファレンス・デザインとPCellライブラリを含むIPL 1.0スタンダードのリリースを発表しました。これにより、全ての企業が現在、同じテクノロジの恩恵を受けることができるようになりました。

この非公式で、資金もないIPLグループが、このような短期間で、こんなにも多くのことを達成することができたのは、この問題に関して協業を行う時期がきたという、大きな根拠になります。共通の関心とメリットが、協業を成功させる原動力です。そして、このIPL Allianceの結果は、まさしく期待されていたメリットを表しています。半導体業界の歴史において初めて、集積回路の設計者が、社内で開発されたツールを含め、ほとんど全てのOAベース・ツールで、同じPCellライブラリを使うことができるようになりました。多くの場合、わずかな労力とIPLスタンダードに準拠する最先端機能によって、複数の工場またはファウンダリ間で、少なくとも特定のテクノロジ・ノードで、"ポータブル"なPCellsを作るという夢を実現することができます。

■共に駆動するツール

2007年秋のSi2 OpenAccessカンファレンスにおいて、スタンダードのシンボル(Si2より提供)を使用して、あるベンダーの1つのツールで作成され、OAに保存されたスケマティックを、他のベンダーのツール上で開き、データを修正し、データ変換が困難であったサード・ベンダーのツールに渡されましたが、接続性は依然として損なわれませんでした。このスケマティックを用い、IPLのインターオペラブルPCellライブラリを使用して作成したレイアウトを、別のツールで若干PCellのパラメータを変更し、接続性を維持したまま1組のノードを配線した。同時に、意図的にDesign Rule(DRC)違反を作成した。他のベンダーのツールでDRCを実行し、さらに別のベンダーのツールでレイアウトにエラー・フラグを表示させました。このエラーは、レイアウト・ツールで修正し、さらに配線を加え、また別のベンダーのツールでDRCを実行し、レイアウトに違反がないことを示しました。GDSIIのように、OAから他のフォーマットにオリジナル・データを変換する上で、時間はまったくかかりませんでした。

図3: オープン・デザイン・ツール環境

なぜ、このような素晴らしい結果を出すことができたのでしょうか?結局、これこそが、全ての顧客がツールに期待する、方法だからです!これが本当に並外れたものであるということは、大手半導体企業の多くが内製EDAツールを使用し続けることからもわかります。コンピュータの世界では、標準化されたプラグとコネクタを使用するシームレスなネットワークで、共有の通信プロトコルを使用し、ハードウェアとソフトウェアがシームレスに駆動すべきだと考えられています。市場で受け入れられるために、ベンダーはツールを、シームレスに相互動作させなければなりません。もし、より互換性のあるツールが市場に参入してきたら、また、これは常に起こりうることですが、ベンダーは危険にさらされ、スタンダードからそれて、取り残されてしまいます。あらゆる顧客がインターオペラブルなツールを望むため、インターオペラブルであるということは、競争上優位であると言えます。それではなぜ、EDAは違うものであるべきなのでしょうか?

このSi2 OpenAccessカンファレンスでのデモンストレーションが2007年の主な実績でしたが、現在、複数のベンダーのツール上で同じPCellライブラリを使用可能なIDM、ファウンダリ、ファブレス・デザイン・チームの数は急速に増加しています。初めて、顧客はファウンダリ認可のデザイン・キットが彼らのデザイン・フローでシームレスに稼動するということがわかり、業界最高水準のデザイン・ツール・セットのメリットを得ることができます。

■まとめ

オープンなPCellとその機能がOAデータベース上で稼動する場合、革新的なEDA新興企業とトップEDAベンダーは同じ競争の場に立つことになる。一旦、データベースを開発するためのコストや労力が軽減され、インターオペラビリティに対する障害が解消されれば、新たなアイデアや製品が登場してくることになるでしょう。既に、多くのEDA新興企業やベテランが、アナログの自動化と全体的な設計生産性のレベルを向上させるために働いています。公平な競争の場を得ることで、優れた起業家や大学研究者達による、新しいアイデアの創造、実行を促進することになるでしょう。

同時に、既存の製品は、生き残るために進化しなければなりません。デザイン・チェーンにおける競争力の欠如は、マーケット・リーダーのみならず、他の誰のためにもなりません。オープンなPDK開発で協業する人々は、競争が競合会社はもちろん、彼ら自身の製品を改善するということ、また、自分たちには顧客の要望に合わせて技術を革新し、協業する義務があると確信しています。顧客のインターオペラビリティに対する要求は、ますます増えています。協業で失敗すれば、より良いものを作るために喜んで協業する他の競合会社やグループに、協業の持つ優位性を譲ることになります。

設計側のサプライ・チェーンは、半導体サプライ・チェーンの他のどの部分とも、変わりありません。「我々が常に行ってきた方法」は決して十分ではなく、協業は最優先事項になっています。IPL Allianceのようなグループは、十分な動機づけがあれば、具体的で意味のある成果を出すことができることを示しています。人々が協業すれば、驚くような結果を出すことができます。

Richard Morseは、SpringSoft社のEDA Alliances and Technical Marketing Managerです。

Si2に関する情報は、www.si2.orgを、またIPL Allianceに関してはwww.iplnow.comをご参照ください。