半導体と物理、アナログ回路とSpice Simulationその2 -パイリサーチラボ柳氏

半導体と物理、アナログ回路とSpice Simulation

第二回:アナログ回路と芸術

PI Research Labo(パイリサーチラボ) 代表 柳 孝裕

1. はじめに

第一回目は、連載のPrologueということで、うんちくをいろいろ語りましたが、二回目からは真面目に技術情報を提供したいと思います。第二回目は、アナログ回路と芸術と題して、さらに大袈裟な言葉で、アナログ回路の設計の奥深い部分を語りたいと思います。ですので、アナログ設計者以外の方が読まれても、面白い内容かと思います。

アナログ回路設計で重要なのは、前回一部書きましたが、デバイスの知識、回路知識、経験等があります。それに加えて、レイアウト技術が必要になります。ここまで書くと今回のテーマにだんだん近づいてきます。

アナログ設計者という、対象者が広くなるのですが、ここでは半導体のアナログ設計者ということで、非常に対象となる人は少なくなります。プリント基板設計者は、基本的に配線パターンしかデザインすることはできないですが、半導体設計者は、配線だけでなく、デバイスのレイアウトをしなければいけません。さらには、配線だけでなく、デバイスの良し悪しを決定づける根本のデザインを半導体のアナログ設計者はしなければいけません。

良く、基板設計者が、○○のICはいまひとつ性能が悪いとか、△△の製品が断然性能が良いとか聞きます。まったく同じレイアウトをしても、同一性能にならない事が多々あります。つまりアナログ設計者が、どうしても乗り越えられない部分があります。それは、メーカによりデバイス(MOS,Bipolar等)の基本特性が違う事、いわゆるプロセスやデザインルールが違う事に起因しています。詳細は、次回のアナログ設計と物理にてお話するので、これぐらいにして本題に戻ります。

2. レイアウト技術について

レイアウト技術というと漠然としているの、アナログで重要な項目を以下に列挙します。

※ここでは、アナログ全般の通説を記載するのでPCBデザインも含まれます。

1. 電源、グラウンドは一点で結ぶ

2. 信号線をクロスさせない(特にデジタルラインと)

3. 電源、グランドはべたで面積を広く取る

4. 差動線は、対称になるように

5. 電源、グラウンド、信号線は、出来るだけ短く

6. デジタルとアナログは基板上でもアイソレーションする

7. ノイズが気になる配線には、シールド構造を用いる

8. 製造公差を見越したデザインにする

等々です。

文章だけですと読むのも疲れますので、実際のアナログのレイアウトを見てみましょう。

対称性の美しいレイアウトが見て取れます(レイアウトにも芸術的な要素を感じることが出来ます)

以下ご紹介するのは、7年前のものですので、若干今のレイアウトとは違うと思います。

そして、Wi-FiのRFフロントエンドです。

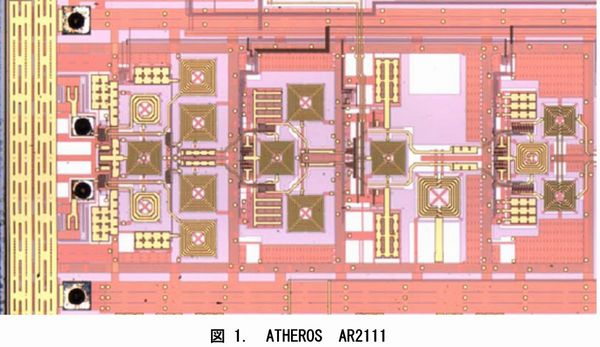

図1のChip写真がATHEROSのAR2111、802.11b/gに対応したRFフロントエンドChip写真の一部です。RFの設計者でない方にもわかるように説明しますと、四角の渦巻きがスパイラルインダクタンス(L)になります。

図1のChip写真がATHEROSのAR2111、802.11b/gに対応したRFフロントエンドChip写真の一部です。RFの設計者でない方にもわかるように説明しますと、四角の渦巻きがスパイラルインダクタンス(L)になります。

まだこの頃のスパイラルインダクタンスのQ値は低く10未満でした。レイアウト見て気づいた人は、かなりの人だと思います。(スパイラルインダクタンスの下の基板には、何も対策されていません。)

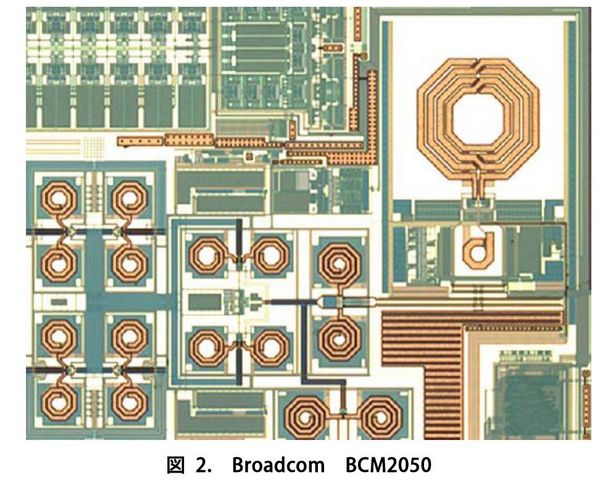

続いて、BroadcomのBCM2050という同じくWi-FiのRFフロントエンドのChip写真です。

Atherosの違いはスパイラルインダクタスのレイアウトになります。

Atherosの違いはスパイラルインダクタスのレイアウトになります。

巻き数(設計回路と定数が違うので比較はできませんが)が明らかに違います。

一番大きなスパイラルインダクタスのレイアウトです。

昔、国内某メーカ様のスパイラルインダクタンスの解析をしていた時に、このようなレイアウトを拝見したことがあります。ただ、Atherosと同様、基板には何もありません。

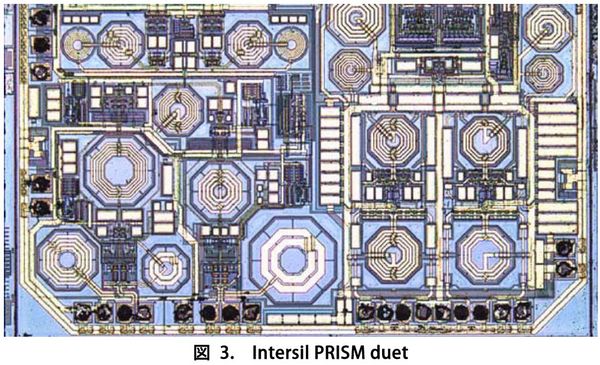

図3はIntersilのPRISM DuetでDualバンドのWi-Fi chipになります。

図3はIntersilのPRISM DuetでDualバンドのWi-Fi chipになります。

こちらは、スパイラルインダクタンスのレイアウトが完成系に来ておりまして、グラウンドシールのパターンも見ることができます。(本当はまだまだなのですが)

基本的に、物理法則がここでも働いていまして、スパイラルインダクタに電流が流れると

基板にも誘導電流が流れます。一般には渦電流(Eddy current)と呼ばれているもので、スパイラルインダクタに流れる電流を打ち消す方向に作用しますので、これをなくすように

さまざまなグラウンドシールドデザインがあります。皆様がいろいろと検索して調べてみると面白いと思います。

そこで、資料や論文を見るときに一点注意して調べて欲しい点『電磁界ツール頼みで、最適解を求めようとしている論文が多いかも、そして物理、数学的な考察がない』で見てください。

話戻りまして(話はよく脱線します)、3製品共通しているのは、CMOSプロセスで製造されているということです。写真を見てわかるのですが、きれいに対称レイアウトがされているのが見て取れます。繰り返しになりますが、どれもレイアウトは美しいですね。その美しいレイアウトにはいろいろな苦労や努力、さらにはこういうレイアウトでないといけない理由があります。現場のアナログエンジニアになりますと、chip写真を見るだけで、いろんなことがわかってきます。

このようなchip写真をみると、昔、私が新入社員の頃、レイアウトの仕方を上司からいろいろと教えていただいた頃を思い出します。中でも、『美しくなければ動かない』という言葉が印象的でした。また、レイアウトには必ず意味がある。ということで、設計前の予備検討では、必ずchipの分解写真を撮るようになりました。

最近のICの実物を撮って見ること*は大変なのですが、この事は、いまだに役にたっています。

3. 対称性:オペアンプのレイアウト

RFが先に出てきましたが、続いてはオーソドックスなオペアンプのレイアウトについて話をします。オペアンプのレイアウトについては、あまり表に出てこないもので、あまり書物もないかと思います。

オペアンプ、差動のオペアンプの場合よく言われるのが、『たすきがけ』です。

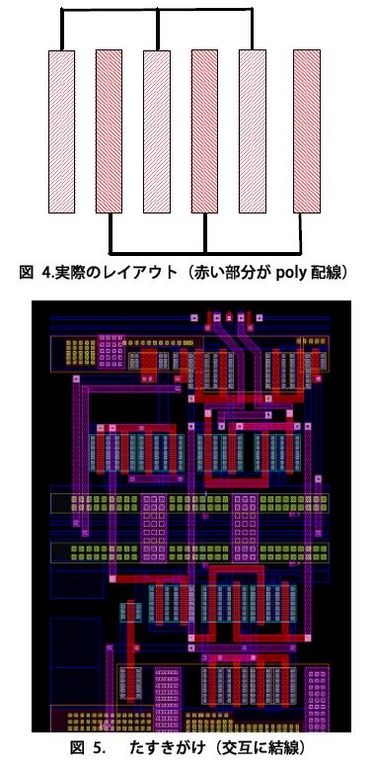

具体的には図4に示すように、差動の部分をレイアウトします。理由は、プロセス変動による影響を対称性を利用して打ち消す為です。これをしないと、CMOSのオペアンプではオフセットが10mVぐらいでは収まらず数10mV半ば近くになって使い物にならなくなります。実際のレイアウトは図5に示します。これは差動2段の構成になっています。(メモリの差動センスアンプ)

デジタルのレイアウトとは違い、レイアウトに対称性が必須で図5のレイアウトはイマイチですが、信号の流れは上から下へと一応レイアウト上で注意点と呼ばれるものはクリアしています。

このようなレイアウトは、レイアウトする人によっていろんなレイアウトが存在します。

デジタルの場合は、基本となるセル(スタンダードセル)が決まっており一からレイアウトするというよりも配置するので、アナログのレイアウトはまさに芸術とまではいかないですが、レイアウトする人の技量によって変わってきます。

実際にレイアウトを描いても、出来上がりの寸法(デザインに依存する性能)はどのように変化しているか確認する手法は作って見るしかありません。アナログは必ず試作がいるというのは、大部分はここから来ています。

実際試作してみないと、出来上がりの性能が予測できないからです。

試作をして実際の性能を見た後、いろいろと対策を施します。

当然回路の定数をいじることもあり、それらは必ずレイアウトに反映するのです。

では、現在試作をしないと予測できないのでしょうか?

いくつかの問題は、現在のEDAツールを用いることで解析が可能です。

ここで紹介する内容は2002年に日経エレクトロニクスに私が解析し掲載した内容を使用しています。

(当然デザインルールも古いのでご容赦ください。)

図6に差動回路の3次元構造を示します。ツールは、SILVACO社のCLEVERを使用しています。

このCLEVERの良いところは、レイアウトからプロセス(MASKを使用します)コマンドを使用して3次元構造を

作成できます。これらのツールは、TCADのプロセスシミュレーションと呼ばれるツールに該当するですが、CLEVERはこのエンジンを搭載して実際の3次元構造を模造することが出来ます(限界はあります)

中でも、アナログ設計者が手をつけられなかった部分、実際にレイアウトを描いたオペアンプのオフセットがレイアウトのばらつきにどれだけ変化するか、こういった事もCELVERではMASKのミスアライメント機能で実際の出来上がり構造かLPE(Layout Parasitic Extraction)によってトランジスタの出来上がり寸法さらには周辺の寄生RCまで抽出できます。

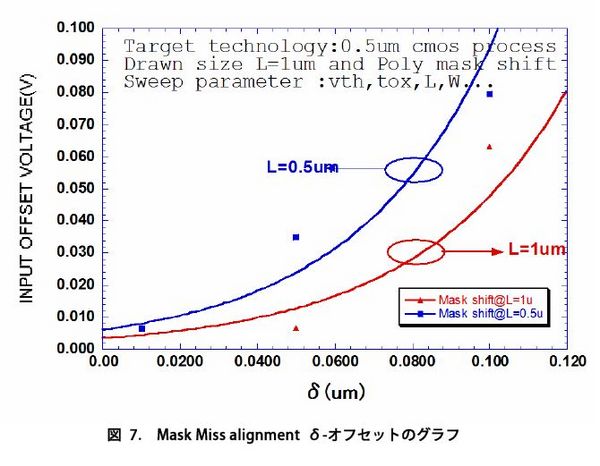

では、実際に図6の構造に対して、ばらつきのSimulationをした結果を以下図7に示します。

条件として、0.5umのデザインルールで敢えて最小のL=0.5umで差動部分をレイアウトした場合、1.0umでレイアウトした場合とマスクずれの変動をδ(um)として差動回路の入力オフセットを求めたものです。

最小のL=0.5umでレイアウトした場合、マスクがδ=0.1umずれると約80mVずれるとなっています。

この図7のグラフでは、トランジスタの酸化膜厚も変化させているので、マスクのミスアライメント-オフセットのグラフになっていません。一つの目安としてください。

CELVERにより、3次元構造作成後、LPEによりトランジスタ+寄生RCの抽出を行って、最終的にSpiceによりSimulationして得られた結果です。

あとは、ユーザとして『する』か『しないか』で大きく変わってきます。

おそらく、各会社ではいろんなツールを持っていますが、100%使いこなしているところはないと思います

50%ぐらいではないでしょうか?その使いこなしの部分で10%あげるだけで、詳細な解析、Simulationが出来ますし

試作の回数も減ることもあるかも知れません。

HDLABで開催するSpice Simulationの講座は、単なるSpiceの講座ではありません。

Spiceと連携するツールの紹介を含めて、以下内容で講座をしております。

現在、初級講座と中級講座に分かれまして初級では、一般的なSpiceの記述をマスター、そして収束しなかった時の対処方法や、精度の上げ方等より実践的な内容をご紹介します。

中級講座では、RFーCMOSで必須なHB法、PSSの解析手法、そしてノイズの解析等を

増幅回路の例題を通して学習していきます。

Spice Simulation初級講座:

http://www.hdlab.co.jp/web/a010education/b018trainingexpt/0025spicesimulation.php

Spice Simulation中級講座:

http://www.hdlab.co.jp/web/a010education/b018trainingexpt/0075spicet.php

おそらく他では、このような講座はされてないのでは?と思います。

アナログ設計者としてツールは道具に過ぎません、しかしツールを使いこなすことによってさらに解析能力(表現力)が高まることは言うまでもありません。是非是非受講してください。

次回

第三回:アナログ回路と物理(予定)

第四回:アナログ回路と制御理論(予定)

reference:

Semiconductor Insight: http://www.semiconductor.com/

Silvaco CLEVER : http://www.silvaco.co.jp

著者プロフィール:

PI Research Labo(パイリサーチラボ) 代表 柳 孝裕(やなぎ たかひろ)

年齢:43歳 牡牛座 AB型 大学:理工学部 物理学科 専攻:一般相対論と宇宙論 Einstein方程式の厳密解の解法

大手自動車メーカにて:メモリ回路の高速化研究、高速ADCの開発、ADC/DAC評価&Simulation技術を開発や半導体でない部分では、F1のEMSの開発、電子スロットルの開発

外資系メーカおよびにて:ΔΣADC、高精度電源回路、FPDの3次元高精度モデリングおよび抽出、

センサー系のモデリング、SDR(UMTS,WiFi)/DPDのProject Management、1bit ΔΣD-ClassアンプProject 責任者、Noise Simulation技術の開発(Spice )、jitter分離法の研究

M2M(UMTS/GSM) Project Managerを得て昨年独立。

尊敬する人:レオナルドダヴィンチとアインシュタイン 趣味:オーディオ、音楽、写真、天体観測、物理学

夢:大学に戻って物理学の研究