16nmFFデザインの消費電力を確実に15%削減するGUCの最先端ローパワー設計フローとは?

約1ヶ月前の2016年7月15日、みなとみらいのホテルにてCadenceのユーザー・カンファレンス「CDNLive Japan 2016」が開催された。

同イベントはCadenceが世界各地で開催しているローカル・イベントの一つで、各地域のCadenceユーザーによる設計事例の講演が主体となっている。今年の「CDNLive Japan 2016」では、Cadenceの講演も含めて計30のセッションが行われ700名以上の来場者を集めた。

ここでは「CDNLive Japan 2016」で行われたユーザー講演の一つである、Global Unichip Japan株式会社 DSセンター長 入江 和幸氏の講演について、入江氏へのインタビュー内容も含めて紹介する。

講演タイトル:

「16FFCプロセス製品開発におけるケイデンス合成-レイアウト高親和性による高パフォーマンス実現、及び確実な低消費電力実現フローの確立」

入江氏は元国内大手半導体メーカーのハードウェア設計者でバックエンド設計のエキスパートと言える人物。2014年からGUC社に在籍しており、現在は同社日本拠点のデザイン・チームを指揮している。入江氏は現役のエンジニアとしてバックエンド設計ツールに精通しており、EDAの世界でも名の知れた存在だ。

同氏によると、GUCはTSMCが筆頭株主の設計会社である事から、2012年からいち早く16nm製品の開発に着手。既に最先端のTSMC 16nmFFCプロセス製品を含む10製品以上の16nmチップを開発済みで、うち2製品はGUC Japanのチームによって開発を完了している。なお、既に同社では7nmチップの開発にも着手しているという話だ。

今回「CDNLive Japan 2016」で入江氏が語ってくれたのは、Cadenceの新型配置配線ツール「Innovus」の話とGUCの構築したローパワー設計フローの話と大きく2つ。

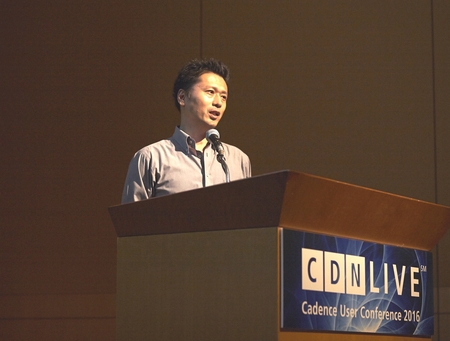

まず「Innovus」については、Cadenceの前世代の配置配線ツール「EDI(Encounter Digital Implementation System)との比較という形で、TSMC 16nmFFCプロセスをターゲットとしたデザインを例にその性能について紹介してくれた。

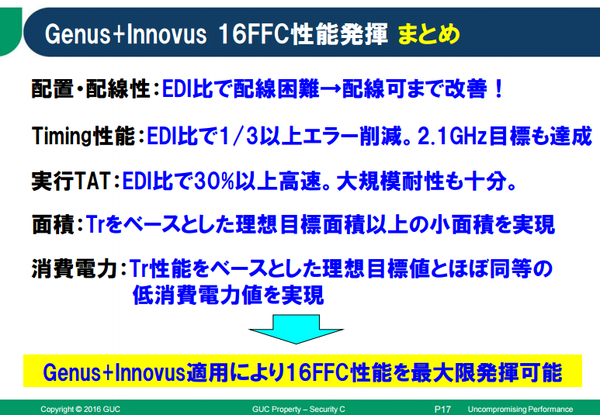

結論から言うと入江氏は「Innovus」を「16nmにチューニングされた最適なツール」と高く評価。入江氏が実際の設計プロジェクトを通じて確認した「Innovus」の主な性能改善項目は下記のスライド通りで、先端プロセス向けに強化された「Innovus」によって数々の課題を解決し、「EDI」では達成が難しかったデザイン目標を理想的な形でクリア出来たという話であった。

※GUCではCadenceの論理合成ツール「Genus」と「Innovus」を組み合わせて適用

※EDIバージョン14.1、Innovusバージョン15.1の利用結果

もう一つのローパワー設計の話は、今回の入江氏の講演の主題となるもので、最先端のTSMC 16nmFFCプロセスのデザインにおいて、新たに構築したローパワー設計フローを用いて大幅な消費電力削減を実現したという興味深いものであった。

入江氏によるとGUCでは、TSMCプロセス向けのローパワー・ソリューションとしてGUC独自の思想でカスタムしたカスタムセル・ライブラリ「PowerSlim」、「PowerHero」を用意しており、デザイン業務に活用している。GUCのカスタムセルはローパワー以外にも面積やスピードに特化したセルも含まれており、今回、GUCでは16nmFFデザインのローパワー化に向けて自社のカスタムセルをフル活用したインプリメントを試みた。

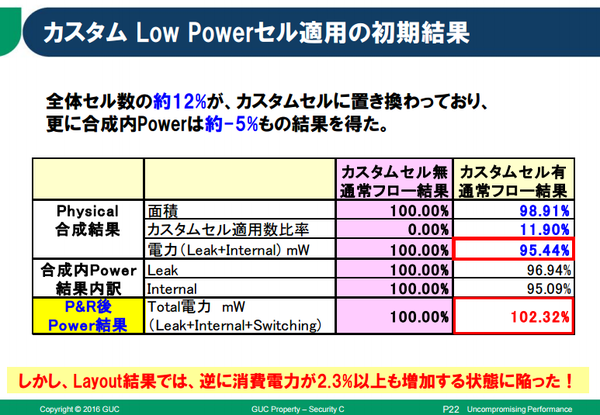

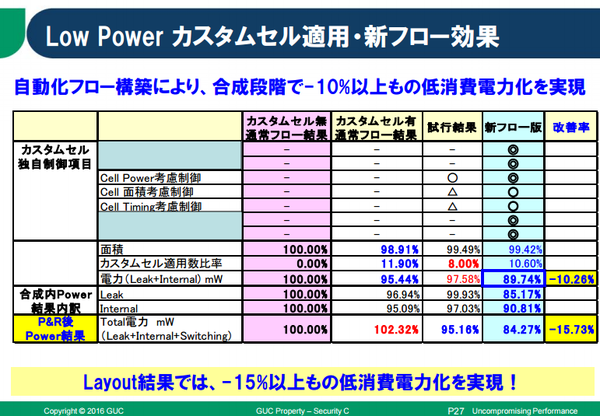

最初にカスタムセルを適用した結果、全体セル数の約12%がカスタムセルに置き換わり、「Genus」のフィジカル合成結果として約5%の消費電力削減を達成。しかし、レイアウト後には逆に消費電力が2.3%以上も増加してしまった。

この結果を受けて入江氏はカスタムセルの適用を最適な形に制御する必要があると判断。というのも、カスタムセルには面積、速度、パワー、配線性、駆動能力、遅延差、など様々なトレードオフがあり、カスタムセルのデメリットがレイアウトに悪影響を及ぼしてしまう事があるためだ。入江氏によると、その傾向はFinFETプロセスでは特に顕著になっているとの話。また、合成およびレイアウトツールは、面積、速度、パワーのバランスを重視する傾向があり、ツールの自動処理では必ずしも狙った結果を得られない事があるという。

そして入江氏は次なる試行として、ローパワーに特化したカスタムセルだけを用いてみた。その結果、カスタムセルの適用率は最初の12%から8%に減り、フィジカル合成の結果は面積、消費電力ともに最初の結果よりも悪化。ところがレイアウト結果としては消費電力が約5%も削減できローパワー化が改善された。

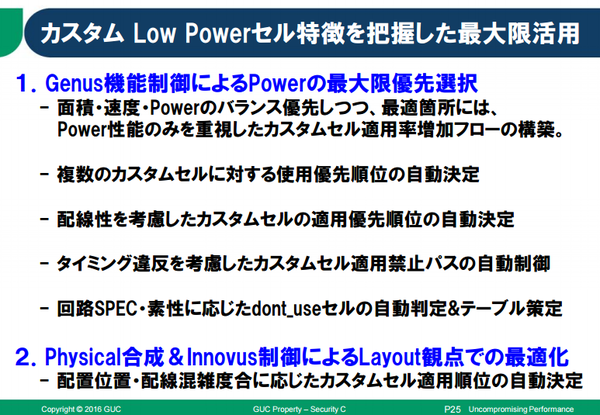

この結果から入江氏は、ローパワー・カスタムセルの効果を確信する共に、レイアウト後に得られたローパワー効果を合成段階から得ることが更なる低消費電力化への鍵であると結論付け、合成&レイアウト工程で適材適所に最大限のカスタムセルを活用するローパワー化に特化した設計フローの構築に取り組んだ。

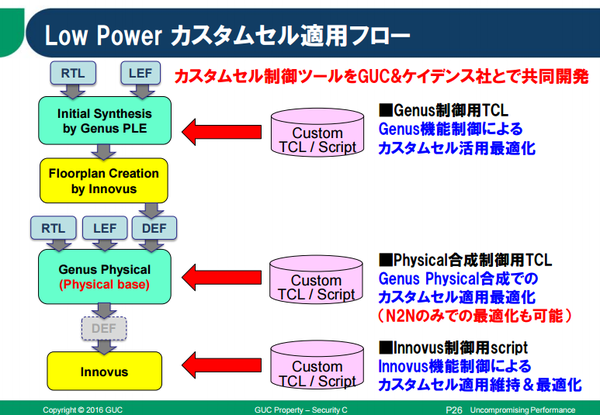

入江氏の考案

したローパワー設計フローは、「Genus」と「Innovus」の両ツールでローパワーに特化したカスタムセルの適用を自動制御するというもので、具体的には下記スライドの通り。GUCのカスタムセルを用いたローパワー設計フローはCadenceと共同で開発され、両ツールを制御するTCLにはカスタムセルの適用箇所や優先順位に関するGUC独自のノウハウが取り込まれた。

したローパワー設計フローは、「Genus」と「Innovus」の両ツールでローパワーに特化したカスタムセルの適用を自動制御するというもので、具体的には下記スライドの通り。GUCのカスタムセルを用いたローパワー設計フローはCadenceと共同で開発され、両ツールを制御するTCLにはカスタムセルの適用箇所や優先順位に関するGUC独自のノウハウが取り込まれた。

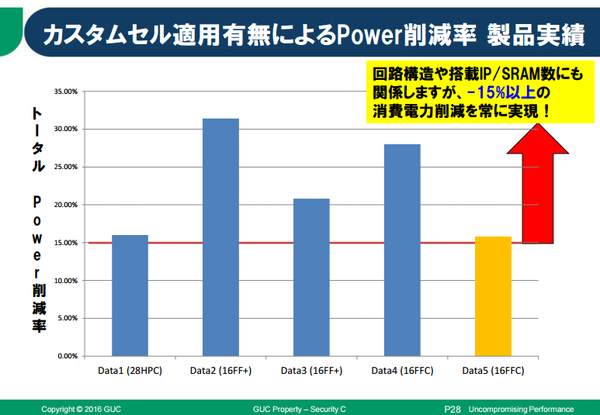

実際に構築した自動ローパワー設計フローを使用した結果、カスタムセルの適用率は10.6%に上昇し、フィジカル合成結果の段階で10%以上、レイアウト結果では15%以上もの消費電力削減を実現。期待以上のローパワー効果を得る事に成功した。同フローは他の28nm/16nmFF+デザインにおいても15%から最大30%という驚くべきローパワー効果を発揮しているという。

※画像資料は全てGUC提供の講演データ

入江氏によると開発した自動ローパワー設計フローを利用すれば、目的に応じて誰でも自動的に、そして常にローパワー化を実現できるという事で、この「誰もが」という点が現場にとって大きいとコメント。また、各社ローパワー設計に取り組んでいるが、常にこれほど大幅な消費電力削減を実現しているのは恐らく世界でもGUCが上位に位置付けられるだろうと付け加えた。

GUCのカスタムセルとCadenceのツールを利用すれば、ある程度同様のローパワー化が可能かとも思えるが、入江氏曰くフローに取り込んだGUCのカスタムセル適用ノウハウがローパワー化の肝であり、例え同じカスタムセルとツールを用いたとしても、今回構築した自動ローパワー設計フローとの合わせ技でなければ、15%以上のローパワー化(通常セルの利用と比較して)はほぼ不可能だろうという事だった。

GUCはTSMCの顧客を支える世界最先端のデザイン会社で、最先端の16nmFFCプロセスもGUCで開発を手がけたと聞く。その最先端の現場で世界の顧客を相手に最先端のローパワー設計手法を生み出しているのが日本人エンジニアである事を知り、今回の入江氏の講演には驚くと同時に非常に感銘を受けた。半導体の設計技術を発展させるも衰退させるも人次第。入江氏のような業界を牽引するエンジニアの更なる活躍に今後も期待していきたい。