JSNUGレポートその1:Design Compilerリタイミング機能の賢い使い方‐カシオ計算機

2015年9月4日、品川でSynopsysのユーザー・ミーティング「JSNUG 2015」が開催された。

ここでは同イベントで行われた講演の一つ「QoR を改善するためのデータパス・リタイミングの活用 ?Design Compilerの先進的なテクノロジとメソドロジ」について紹介する。

講演者は、カシオ計算機株式会社 研究開発センター 第二開発部 24開発室 鳥越 真志氏である。

※写真の人物が講演者の鳥越氏

鳥越氏は研究開発センターにおいて設計技術の開発に従事されている人物。

今回の講演では、Synopsysの論理合成ツール「Design Compiler」のリタイミング機能の使い方について語ってくれた。

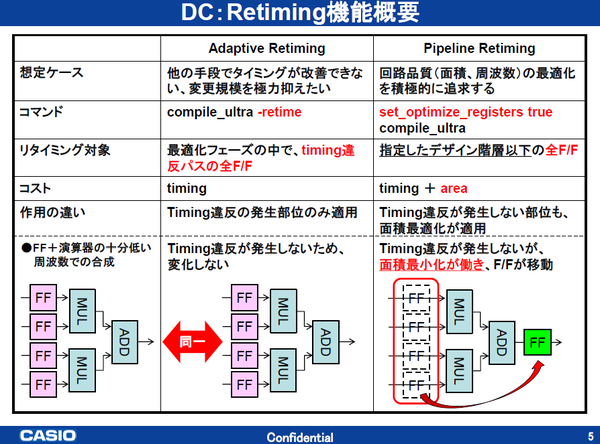

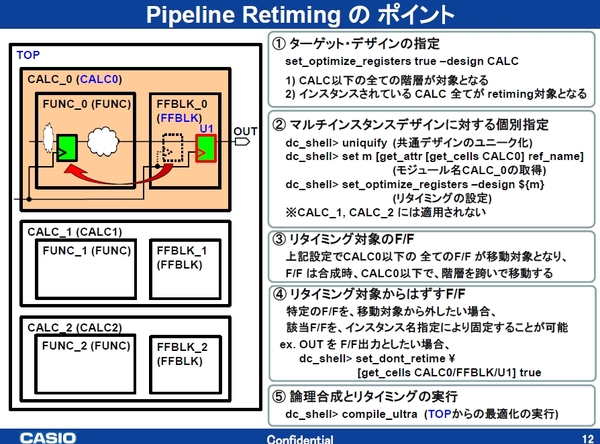

まず鳥越氏は、話の前提として「Design Compiler」にはAdaptive RetimingとPipeline Retimingの2種類のリタイミング機能が備えられている事(下図参照)、そして「Design Compiler」のバージョン2014.09からPipeline Retimingのアルゴリズムが変わった事を紹介し、新たなPipeline Retiming機能を使う上でのポイント(下図参照)と同機能の評価結果について語った。

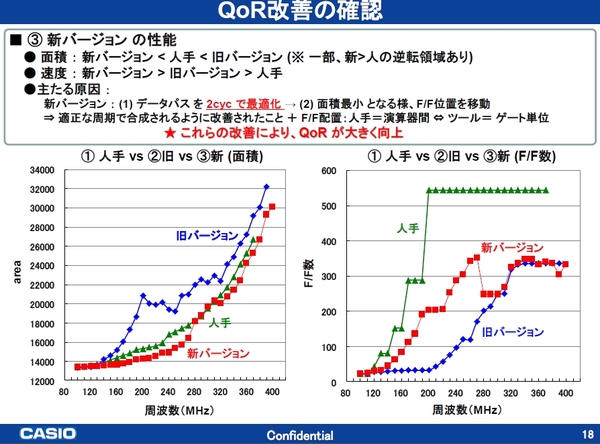

鳥越氏によると、64ペアの入力の差分二乗和を題材にPipeline Retiming機能を評価したところ、面積、速度の両面においてバージョン2014.09のリタイミング機能が旧バージョン(2013.12)および人手最適化の結果を上回る事を確認。バージョン2014.09では、データパスを2サイクルで最適化するように変更され、旧バージョンよりも面積の最小化が可能となった。また、ツールはゲート間へのF/F移動が可能なため人手よりも優れた最適化結果を出せた。

この評価結果に満足した鳥越氏は、実デザインへの適用を試み、Pipeline Retiming機能の向き/不向きを知った。

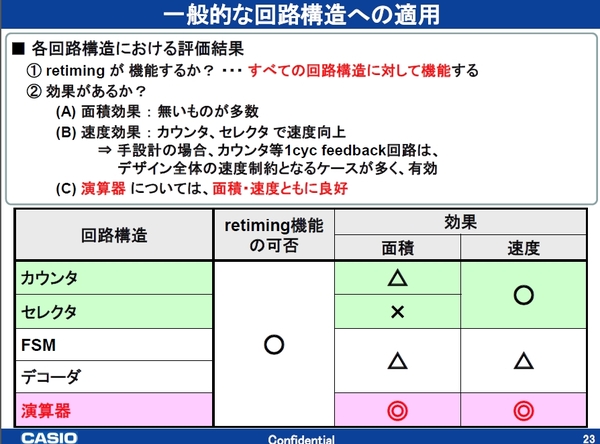

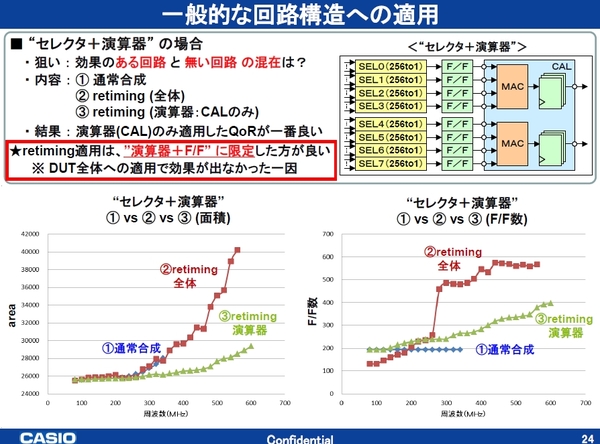

まず様々な機能ブロック11種類に対してデザイン全体にPipeline Retiming機能を適用したところ、処理時間は増加し面積削減効果は出なかった。その原因究明が困難なことから、鳥越氏は一般的な回路構造ごとにリタイミングの効果を調べてみることにした。その結果、演算器については面積効果も速度効果も高い事が分かり、セレクタについてはF/F増加が著しくPipeline Retiming機能には不向きな回路である事が分かった。また、演算器とその他回路の組み合わせに対してはあまりPipeline Retiming機能の効果が出ない事も判明した(下図参照)

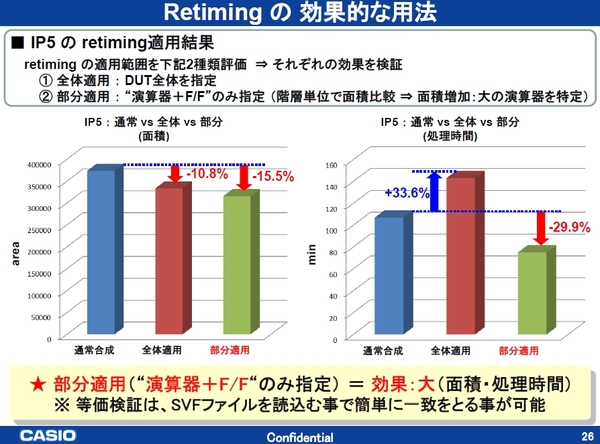

鳥越氏はこれら試行結果から、データパス比率が高く、タイミングが厳しいデザインが最もPipeline Retiming機能の効果が得られると結論づけ、実際に条件にあてはまるデザインに対してPipeline Retiming機能を使ったところ、演算器+F/Fのみに部分適用することで、面積・処理時間ともに大きな削減効果を得られた。

これらの取り組みを通じ鳥越氏は、人手では到達できない「究極の回路」を実現するために、「Design Compiler」のPipeline Retiming機能は非常に重要な機能であるとしながらも、その適用効果は使い方次第であることを指摘。同機能の適用範囲の拡大を訴え講演を終えた。