Calypto Users Forum:富士通QNETの「成功する高位合成フロー」

2013年10月18日、フォーマル検証、パワー最適化、高位合成など各種EDA製品を展開する米Calypto Design Systemsは、新横浜のホテルでプライベート・セミナー「Calypto Users Forum」を開催した。

同イベントは昨年に続いての開催となるユーザー向けのセミナーで、会場には60名を超える参加者が足を運んだ。

ここでは、同イベントで発表された、富士通九州ネットワークテクノロジーズ株式会社による事例講演、「富士通QNETにおける高位合成の活用方法」について紹介する。講演を行ったのは、富士通九州ネットワークテクノロジーズ株式会社、第一開発統括部 第一技部 兼技術戦略室 技術戦略企画部 シニア・プロフェッショナル・エンジニアの山下 公彰氏である。

山下氏は、音声処理や画像処理のチップ開発に従事するエンジニアで設計と合わせて先端設計技術の実用化にも取り組んでいる人物。今回の講演ではCalypto社の高位合成ツールを用いた成功事例というよりは、同社における高位合成フロー、その成功の秘訣について語ってくれた。

山下氏によると、富士通QNETでは2002年から高位合成ツールの実用に取り組み始め、現在では下記4種類の高位合成ツールを所有し本格的に設計で活用。

・Calypto社「Catapult」

・SystemCベースHLS(高位合成ツール)

・FPGA向けHLS(高位合成ツール)

・SystemVerilogベース合成ツール

中でも「Catapult」は稼働率が高く投資に見合った効果を得ているとの事で、当初は「Catapult」の研究開発利用が多かったが最近では製品開発向けに利用するケースが増えたという。山下氏が示したグラフから読み取ると、2013年は高位合成ツールを用いた6件の製品開発のうち3件で「Catapult」を使用したようだ。

複数の高位合成ツールを保有し、高位合成ツールベースの設計を上手く実践しているように見える富士通QNETだが、利点の一方で課題もあると山下氏。高位合成の利用者が限られている点、様々な要因で生産性が左右される点などを挙げ、効果の出る領域は限定的で成果は簡単に得られないとコメント。また言語の壁やノウハウの伝授など人材育成の難しさについても指摘した。

実際の高位合成ツールの活用方法については、山下氏より富士通QENT流とも呼べる「成功法」が紹介された。

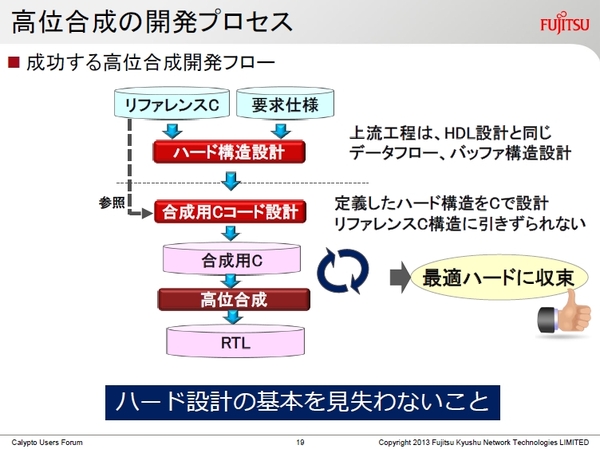

まず、設計フローについては、「リファレンスとなるCコードを引きずらない事」を強調した。C言語からの高位合成というと、リファレンスとなるC言語で記述されたアルゴリズムをハード向けにリファインメントして合成用のCコードを作成するというアプローチがとられる事があるが、富士通QNETではこの手法はNG。リファレンスのCコードはあくまでもリファレンスとし、HDL設計と同様に上流工程でしっかりとハードの構造設計を行い、それをベースに合成用のCコードをスクラッチから設計というのが富士通QNET流で、山下氏はこうする事によって最適なハードが得られ設計の収束も早まるとした。

また、複数の合成ツールを使い分けている富士通QNETならではの話であるが、高位合成ツールの適用分野など活用方針についても、ツールの入力言語の特徴から以下の資料画像の通り富士通QNET流の方針が定められているとの事。この方針により、高位合成ツールの利用に関する現場の混乱を避け、高位合成ツールの適用効果を最大限に引き出す設計を実現しているという。ちなみにCalyptoの「Catapult」は、SystemCでの利用はせず、C/C++ベースの設計の際に利用されているという事だった。

※画像は全てCalypto社提供の山下氏の講演データ。

山下氏は講演の最後に「Catapult」の強みとして、C/C++で設計可能な点や検証環境を自動生成する「SC_Verify」機能を挙げ、これら強みによって高位合成導入の目的である「開発効率の向上」が実現できると強調。逆に弱みとしては、幾つかある中で「遅延見積りの精度」が低いと最優先での改善を求めた。

= EDA EXPRESS 菰田 浩 =

(2013.11.07

)