Xilinxが次の10年に向けた高位合成搭載の新設計環境「Vivado」を発表

2012年4月25日、Xilinxは、Vertex-7シリーズ以降の次世代デバイス向けの専用設計環境「Vivado」を発表した。

Xilinxによると「Vivado」は、次の10年を見据えて新規開発した設計ツールで、SoC化するFPGAの効率的な設計を実現するもの。論理合成、配置配線、シミュレーターと設計環境を構築する各エンジンが既存の「ISE」で使われているものから刷新され、新たに高位合成のエンジンも搭載された。

これまでの設計環境「ISE」は、プログラマブル・ロジック・デバイスの設計環境として、FPGA上のロジック設計を中心としたものであったのに対し、新たな「Vivado」は、ARMプロセッサをはじめとする様々なIPの搭載やデバイスの三次元化などFPGAの進化に対応するもので、言わばFPGAシステム全体のインテグレーションを実現する環境。

今回の「Vivado」の発表と合わせXilinxは、「ALL PROGRAMMABLE」という企業のキャッチ・コピーを新たに打ち出しており、既に出荷しているVertex-7シリーズのFPGAと新たな設計環境「Vivado」によって、同社のソリューションが更にプログラマブルなソリューションとして進化・強化していくことを強調。Xilinx日本法人社長のSam Rogan氏は、今回の「Vivado」の発表を「Xilinxの方向を定義する重要な発表」とコメントしている。

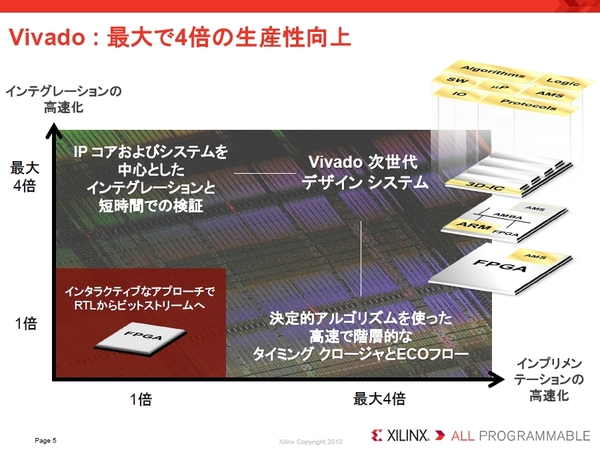

「Vivado」は、既に100社を超える企業が1年に渡るベータ版プログラムに参加し試用しており、その生産性の高さは実証済み。Xilinxは「Vivado」の実行速度をシステムのインテグレーションにおいてもインプリメンテーションにおいても、ISE現行バージョンおよび他社ツールと比較して最大で4倍高速としており、実際に「Vivado」を試用した国内のパートナーからも以下のような評価結果が報告されている。

・OKI情報システムズ

Vivadoベータ版をXilinx-7 LX690ターゲットにPCI-E gen3のデザインで評価したところ、を実装したところ、ISE14.1よりもインプリメントのランタイムが3.3倍高速、インプリメント実行中のメモリ使用量は1.2倍向上、フロアプランにおいて省スペース配置を実現。

・東京エレクトロンデバイス

評価ボード試験用の回路と画像処理回路をミックスした複雑なデザインでVivadoベータ版を評価したところ、ランタイムはISEよりも2倍高速、ISEでは要求性能を満たすために多数のカット&トライが必要だったが、Vivadoでは一発で配置配線を完了できた。

・ベリフィケーション・テクノロジー

512ビットの高速バスを内蔵するブロードキャスト用チップの実製品設計でVivadoベータ版を評価したところ、ISE13よりもイタレーション回数を大幅に削減。苦労した配置配線がスムーズに実行でき、全体的な設計生産性3-4倍向上できた。

※画像はXilinx提供のデータ

具体的に「Vivado」の大きな特徴と言える機能は大きく2つ。

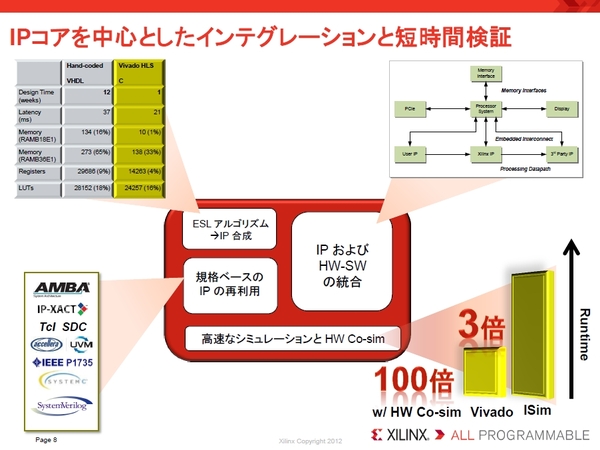

まず、システムのインテグレーションを高速化する機能として、昨年2月に買収したAutoESL社の技術をベースとした高位合成機能が用意され、C言語ベースでのFPGA設計が可能となった。この高位合成エンジンは、C/C++/SystemCからの合成が可能でこれら言語の混在記述にも対応可能。ループのパイプライン化をはじめとする各種合成指示や面積、パフォーマンス、消費電力などの各種パラメーターを設定した自動合成が可能なほか、合成したRTLをIP-XACTフォーマットでパッケージ化する事もできるという。

FPGA向けの高位合成は、これまで多くのEDAベンダがツールを提供してきているが、FPGAベンダの提供する設計環境に高位合成エンジンが搭載されるのは今回の「Vivado」が業界初。競合のAlteraは、並列プログラミング向けの言語OpenCLを用いたFPGA設計の研究を積極的に進めているが、Xilinxは高位合成を用いたC言語によるFPGA設計手法を推し進め、その環境の提供で先行した格好だ。システムレベルの設計環境に関しては、今後両社のソリューションはそれぞれ異なる方向へと発展していくのかもしれない。

※画像はXilinx提供のデータ

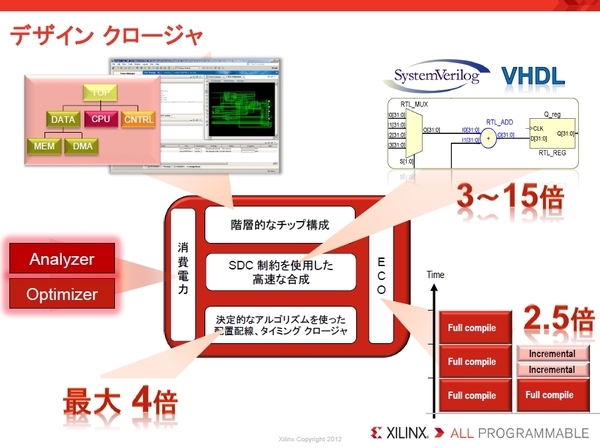

もう一つ「Vivado」の特徴と言えるのが進化したインプリメント機能である。「Vivado」では、「shared scalable data model」と呼ぶ新たなデータモデルを採用しており、各ツールで利用するデータモデルが統一された。このモデルを利用することで階層的なチップのプランニングやパーティショニングが可能となった。また論理合成エンジンも刷新され、SystemVerilogからの合成が3-15倍に高速化されたほか、そのキャパシティは1億ロジック・セルに拡張された。更にタイミング、ワイヤ蝶、配線密度などを同時に考慮する新たな配置配線エンジンによってデザインの収束時間が最大4分の1に短縮可能となり、ECOにおいてもインクリメンタル機能のサポートでその生産性は2.5倍向上された。その他、自動クロック・ゲーティング機能により消費電力も最大30%削減可能となるなど、インプリメント作業全般に渡ってその生産性が大きく向上された。

※画像はXilinx提供のデータ

その他、今回「Vivado」で実現された新機能としては、IP-XACTの技術を用いたシステムレベルのIPの接続機能「IP Integrator」やC言語ベースのモデルを利用した、ブロック単位あるいはシステム全体のビヘイビア・シミュレーションなどがある。

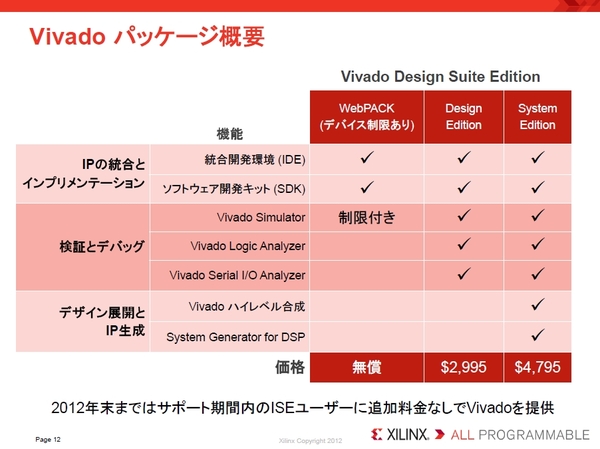

尚、「Vivado」は既に早期顧客向けに提供されており、一般顧客向けには2012年Q3(7-9月)に有償版を提供開始予定。無償版の提供は2012年Q4からを予定している。「Vivado」のリリースにより既存の「ISE」のエンハンスは終了するが、既存ユーザー向けのサポートは引き続き継続される。高位合成機能を含む「Vivado」の最上位パッケージの米国でのライセンス価格は年間$4,795?となっている。

※画像はXilinx提供のデータ

= EDA EXPRESS 菰田 浩 =

(2012.04.25

)