【JSNUG2011】リコー、MATLAB/Simulink環境にSynopsysのASIP開発環境をリンク

2011年9月7日に開催された、Synopsys Users Meeting 2011(JSNUG2011)における、株式会社リコーの講演レポート。

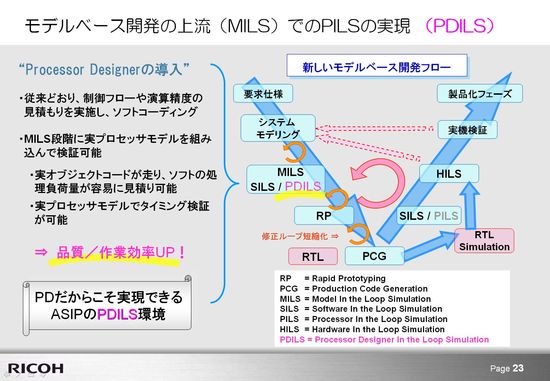

株式会社リコーはSynopsysのユーザーとして、「Processor DesignerによるASIP開発におけるモデルベース信号処理開発との協調検証について」と題したシステムレベル設計の成功事例を発表した。

今回発表を行ったのは、株式会社リコー、研究開発本部、基盤技術開発センターの久保田修司氏で、無線システムにおけるデジタル信号処理部の設計に関するものであった。

久保田氏によると、リコー社内ではデジタル信号処理開発にMATLABを用いたモデルベース設計手法が定着しており、MATLABで開発したモデルからSynopsysの高位合成ツール「Synphony」を用いてRTLを合成し、FPGAへ実装するという早期プロトタイプ・フローが確立されていた。

※画像はリコー提供のデータ

しかし近年、無線規格が多数登場し、デジタル信号処理がより複雑になり、回路規模の増大を抑えるために、伝播路の計算やモードによって切り替える誤り訂正処理など、ベースバンド処理の一部をソフトで処理する事を考えるようになった。

そこで同社では、既に社内で利用実績のあるSynopsysのカスタム・プロセッサ開発環境「Processor Designer」を用いて専用プロセッサ(ASIP)を開発する事にした。これをきっかけに久保田氏はMATLABを用いたDSPのモデルベース設計フローにカスタム・プロセッサ開発環境「Processor Designer」をリンクさせる手法を思いつく。

※画像はリコー提供のデータ

久保田氏曰く、「V字フロー」と呼ばれる一般的なモデルベース開発フローでは、開発の早期段階でMATLABを用いてシステムのモデリングを行っても、そのシミュレーションでは制御フローや演算精度の見積りまでしか評価できず、ソフトウェアの処理量の見積や物理モデルとのタイミング検証などは、より後工程の「PILS」または「HILS」以降の実機検証で行うしかなかった。そこで久保田氏はMATLABを用いた「MILS」のフェーズで実ソフトを検証したいと考えるようになった。

MILS:Model In the Loop Simulation

PILS:Processor In the Loop Simulation

HILS:Hardware In the Loop Simulation

当初久保田氏は、「PILS」にあたるSynopsysの「Platform Archtect」をベースに、MATLABで設計したモデルと「Processor Designer」の出力するSystemCモデルをインポートしてシミュレーションを行うという事を考えていたが、「Processor Designer」の出力するモデルをMATLAB/Simulink環境にインポートするという手法を思いついた。

※画像はリコー提供のデータ

具体的には、「Processor Designer」の出力するSystemCモデルのDLLのみを利用してISSを作成。次に「Microsoft Visual C++」を用いてISSのラッパーを作成。そして「MATLAB」で「Simulink」のS-Functionを作成しS-Functionを用いてSimulinkシミュレーションにプロセッサーモデルをインポートする。

実際にこの手法によって「Processor Designer」で開発したASIPモデルをSimulink上にインポートしたところ、通常のシミュレーションよりも「Processor Designer」モデルをインポートした方がより高速にシミュレーションでき、従来のMATLAB/Simulink環境のみでは確認できなかった、割り込みタイミングのオーバーヘッドや、ソフトウェアの処理量およびレイテンシ、初期化処理の挙動などを確認。通常、実機評価の段階で判明する問題を「MILS」のフェーズで確認することが出来たという。

※画像はリコー提供のデータ

久保田氏は従来手法よりも作業効率が高く、製品の品質向上にも役立つこの手法を、「Processor Designer」ならではのモデルベース・シミュレーション手法として「PDILS(Processor Designer In the Loop Simulation」と独自に命名。今後リコー社内の様々なプロジェクトに同手法を展開していきたいと意気込みを語っていた。

= EDA EXPRESS 菰田 浩 =

(2011.09.15

)