Cadenceが待望のバーチャル・プロトタイピング・ソリューションを発表

2011年5月3日、Cadenceは、新製品2種を含む最新の「Cadence System Development Suite」について発表した。

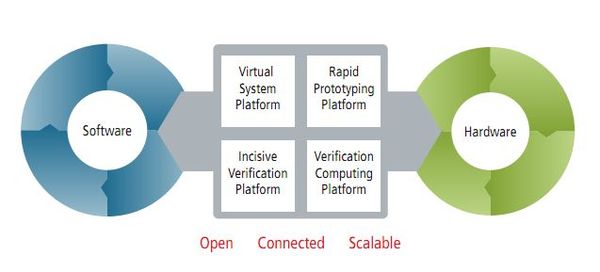

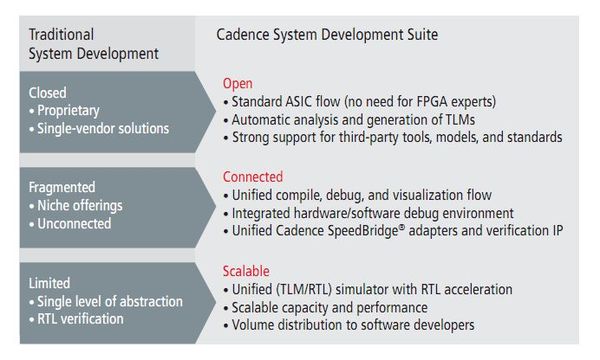

発表によると「Cadence System Development Suite」は、アーキテクチャ検討からFPGAプロトタイピングまでを包含するハード・ソフトの協調設計ソリューションで、同社のエミュレーター環境「Palladium XP Verification Computing Platform」、シミュレーター環境「Cadence Incisive Verification Platform」の他に、新製品となる「Cadence Rapid Prototyping Platform」および「Cadence Virtual System Platform」の4つのプラットフォームで構成されている。

※画像は「Cadence System Development Suite」の構成イメージとその特徴 CadenceのWeb上のドキュメントから抜粋

新製品「Cadence Virtual System Platform」は、今回ようやく明らかにされたいわゆるCadence独自の「バーチャル・プロトタイピング環境」で、実機同等の仮想的なハードウェア・プラットフォームを作成し、ハード上で走るソフトウェアの開発効率アップを狙うもの。基本的にSystemC TLMをベースとした環境で、作成したバーチャル・プラットフォームをシミュレーター、エミュレーター、更にはインプリメントまで繋げる事が出来るというのが、Cadenceソリューションならではの大きな特徴と言える。

競合他社のソリューションとしては、Synopsysの「CoMET/METeor」、「Platform Architect/Virtual Platform」、Mentorの「Vista」などがあるが、それら競合製品と「Cadence Virtual System Platform」とでは「プロセッサ・モデル」の扱いをはじめ、各所に大きな違いがある。

例えば、Synopsysのソリューションでは、独自のプロセッサ・モデルを提供する事で高速あるいは高精度なシミュレーションを実現しており、それが他のソリューションとの大きな差別化要因となっているが、「Cadence Virtual System Platform」は、独自のプロセッサ・モデルは提供せず、ARMから提供される「Fast Models」またはImperasから提供される「OVP fast processor model(ARM, MIPS, Renesas, PowerPC) 」を利用する。

Cadenceのこのアプローチは、ARMをはじめとしたメジャーなプロセッサをターゲットとするユーザーにとっては、ツール環境に依存しない仮想環境を構築できるという大きなメリットがある。しかし、裏を返せばARMとImperasがモデルを提供していないプロセッサはターゲットに出来ないという事になってしまうため、Cadenceは何か手立てを用意しているのかもしれない。

(※Platform Architect/Virtual Platformでは、サードパーティの提供するプロセッサ・モデルも利用可能。)

また、「Cadence Virtual System Platform」は、バーチャル・プラットフォームを「自動的に作成」する仕組みを用意しているようで、プロセッサ・モデル以外の各種周辺機能モデルは、IP-XACT仕様のメタデータを読み込むことで自動生成できるほか、Cadenceの用意するSystemC TLM 2.0のテンプレートを元に自動生成できるようだ。ライブラリとしては下記のような多様なモデルが用意されている。

【Cadenceの提供するVirtual System Platform向けモデル】※ブローシャからの抜粋情報

・Basic components

UART, keyboard/mouse controller, real time clock, programmable timer, interrupt controller, multimedia card, audio codec interface, programmable LED, color LCD, etc.

・Complex components

Ethernet controller, I2C, SPI, bus controller, serial interface, buffer, memory logger, battery, touch screen input, flash memory, initiator, multi-plexor, arbiter, router, etc.

・Virtualized hardware

terminal, Ethernet, etc.

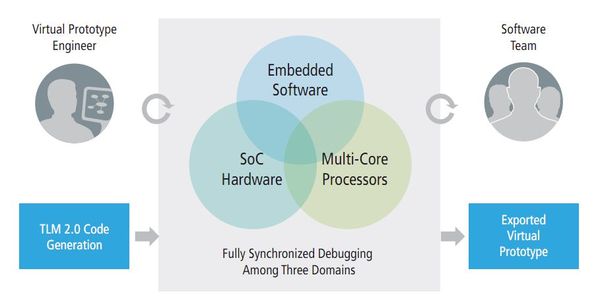

「Cadence Virtual System Platform」には、作成したバーチャル・プラットフォームをパッケージしてソフト開発向けにエクスポートする機構が備えられており、ソフトウェアのみならずハードウェアも同期して可視化・デバッグできるGUIも用意されている。また、バーチャル・プラットフォーム上でのソフトウェアのデバッグには、ARM、Lauterbach、GDBなどのデバッガを利用する事も可能。ソフトウェアの検証および解析には、Imperasの提供するツールも利用できるという。

※画像は「Cadence Virtual System Platform」の運用イメージ CadenceのWeb上のドキュメントから抜粋

尚、「Cadence Virtual System Platform」は、シミュレーター(Incisive)と接続する事も可能でHDLでモデリングされたRTL資産も取り扱う事ができるが、基本的なコンセプトは、SystemC TLM 1.0またはTLM 2.0ベースのバーチャル・プロトタイピングの容易な実現で、SystemC TLMベースのオープンなプラットフォームを容易かつ短時間で作成するという方針を打ち出している。

「Cadence Virtual System Platform」は、「バーチャル・プロトタイピング環境」としては業界の中で後発の製品となるが、SystemC TLMをベースにCadenceの包括的な検証ソリューションならびにサードパーティーとの各種ソリューションに繋がる点は、他社ソリューションに無い大きな差別化要因と言える。年内には正式リリースされるという同製品の今後の活躍に注目したい。

= EDA EXPRESS 菰田 浩 =

(2011.05.07

)