アルテラ、28nmFPGAに向けた3つの新技術を発表

2010年2月2日、アルテラは、開発中の28nmFPGAで使用される3つの新技術を発表した。

発表された新機能は以下の3つ。

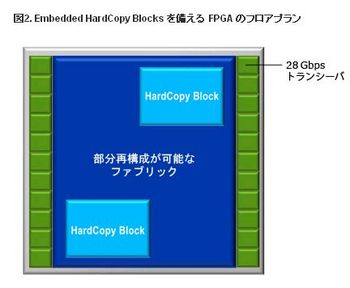

・Embedded HardCopy Blocks

Embedded HardCopy Blocks は、アルテラのストラクチャードASIC「HardCopy ASIC」の機能を活用したカスタマイズ可能なハードIPブロックで、アプリケーション・スペシフィックな機能、トランシーバ・プロトコル、ユーザー独自に所有するカスタムIPなどの実装を迅速かつ低コスト、低消費電力で実現するもの。標準的なファンクションやロジック比率の高いファンクションを最適化したIPブロックとしてFPGA内に取り込むイメージとなる。

・パーシャル・リコンフィギュレーション(部分再構成)

パーシャル・リコンフィギュレーション機能は、文字通りFPGAを動作させたまま、一部分だけを再コンフィギュレーションする技術。この技術を使えば、FPGAと外部メモリで複数のアプリケーションを実現できるようになり、FPGAには必要な機能のみを実装することで、FPGAサイズ、消費電力、ボード面積の削減が可能となる。システムを中断する事無く、リモート操作でシステムを拡張できる点も大きなメリットとなる。

・28Gbps エンベデッド・トランシーバ

現在提供している11.3Gbps エンベデッド・トランシーバの更に上をいく28Gbps エンベデッド・トランシーバを用意。このトランシーバにより、デザインの機能を維持しつつ、外部コンポーネント、I/O数、消費電力、コストを削減することが可能。400Gシステムなどの次世代デザインを、コストの高い外部コンポーネントを追加することなく、ワンチップ上に実装することも可能となる。

アルテラは、同じデザインを40nmFPGAから28nmFPGAに移行し、これら新技術を適用することで、面積、消費電力、トランシーバのチャネル数ともに、4分の1程度まで削減可能としている。

= EDA EXPRESS 菰田 浩 =

(2010.02.03

)