Synopsys SNUG Japan 2024 参加レポート〜ホンダ、ソニー、富士通の事例など

2024年9月20日、日本シノプシスは都内のホテルでユーザーズ・ミーティング「SNUG Japan 2024」を開催した。

コロナ禍以降、数年ぶりに盛大に開催された同イベントでは、Synopsysおよび同社のユーザーによる計45のセッションが行われ、1,000人を超える登録者を集めた。

既にイベント終了後かなり時間が経過しているためイベント情報は閲覧できないが、イベント登録者およびアーカイブ動画の視聴登録者は、12/25まで下記のURLより講演資料がダウンロード可能となっている。

ここでは「SNUG Japan 2024」で行われた幾つかの講演を取り上げ、その内容をレポートする。

■Synopsys Ravi Subramanian氏の基調講演

拡がりゆく「知」の時代。イノベーションの原動力とは。

Synopsys, Product Management & Markets Group GMのRavi Subramanian氏は、かつてMentor Graphicsに買収されたBerkeley Design AutomationのCEOを務めていた人物で業界25年以上のエグゼクティブ。システム設計という視点から半導体業界の現状と今後のイノベーションに向けたSynopsysのビジョンについて語った。

Ravi Subramanian氏は、2021年以降の10年間で半導体市場は倍の規模の成長するという予測データを示し、その背景にはAI、シリコンの多様化、Software-defined systemsと大きく3つの動きがあると指摘。イノベーションを加速する新しい設計パラダイムとして、これからはシリコンからシステムまでの設計ソリューションが重要になるとし、IP、EDA、マルチダイ・ソリューションにまたがるSynopsysの各製品群は今後より強固に統合され、AI技術によって更に進化していくとした。

Ravi Subramanian氏は、AIによる製品強化、SDV開発などに活用するデジタル・ツインの実現について時間を割いて説明。製品開発における人材不足はAIとサブシステム化するIPによって補うようになる。今後はシリコン開発とソフト開発のコラボレーションがキーとなる。といったコメントが印象的だった。なお講演の最後に同社の顧客であるTeslaのデモ動画が流された。動画によるとTeslaの次世代運転支援システムHW 4.0を実現しているAP4チップは、SynopsysのEDAソリューションにより一発完動に成功したという。

■九州工業大学 田向教授の基調講演

ホームサービス・ロボットの組込脳型人工知能を目指したレザバーチップ

九州工業大学 大学院 生命体工学研究科 田向 権(たむこう はかる)教授は、AIの回路実装と応用に関する研究者でAIをすべてのモノに実装することを目指し、エッジ指向型の脳型計算機システムの基礎研究ならびにその応用に向けたAIデータセット生成技術、大規模言語モデルの開発などを行っている。田向研究室の直近の実績としては、2024年7月にオランダで開催された世界最大のロボット競技会RoboCup@Homeリーグで優勝。同研究室の開発したロボットAI技術は、RoboCup世界大会で通算6度の優勝を誇るという。

今回の基調講演では田向教授らが取り組んでいる、脳のように省エネで高性能なAIチップ「レザバーチップ」の開発について語ってくれた。

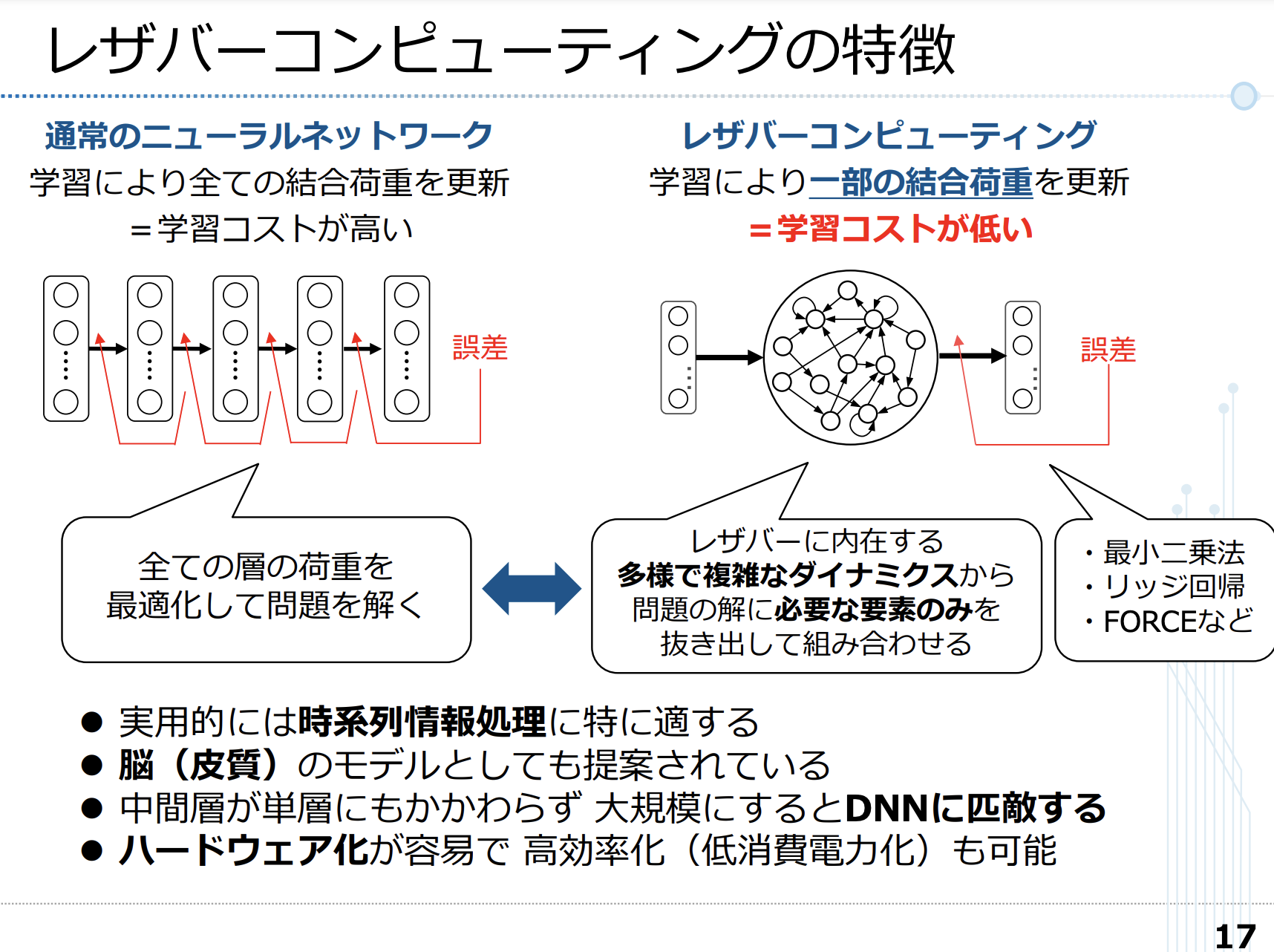

レザバー・コンピューティングの概念については説明を省略するが、田向教授によるとレザバー・コンピューティングは通常のニューラル・ネットワークよりもハード化が用意で低消費電力化と小面積での実装が可能。さらに学習コストが低いなど利点が多く、少ないパラメータ数でニューラル・ネットワークと同程度の精度が出せるという。

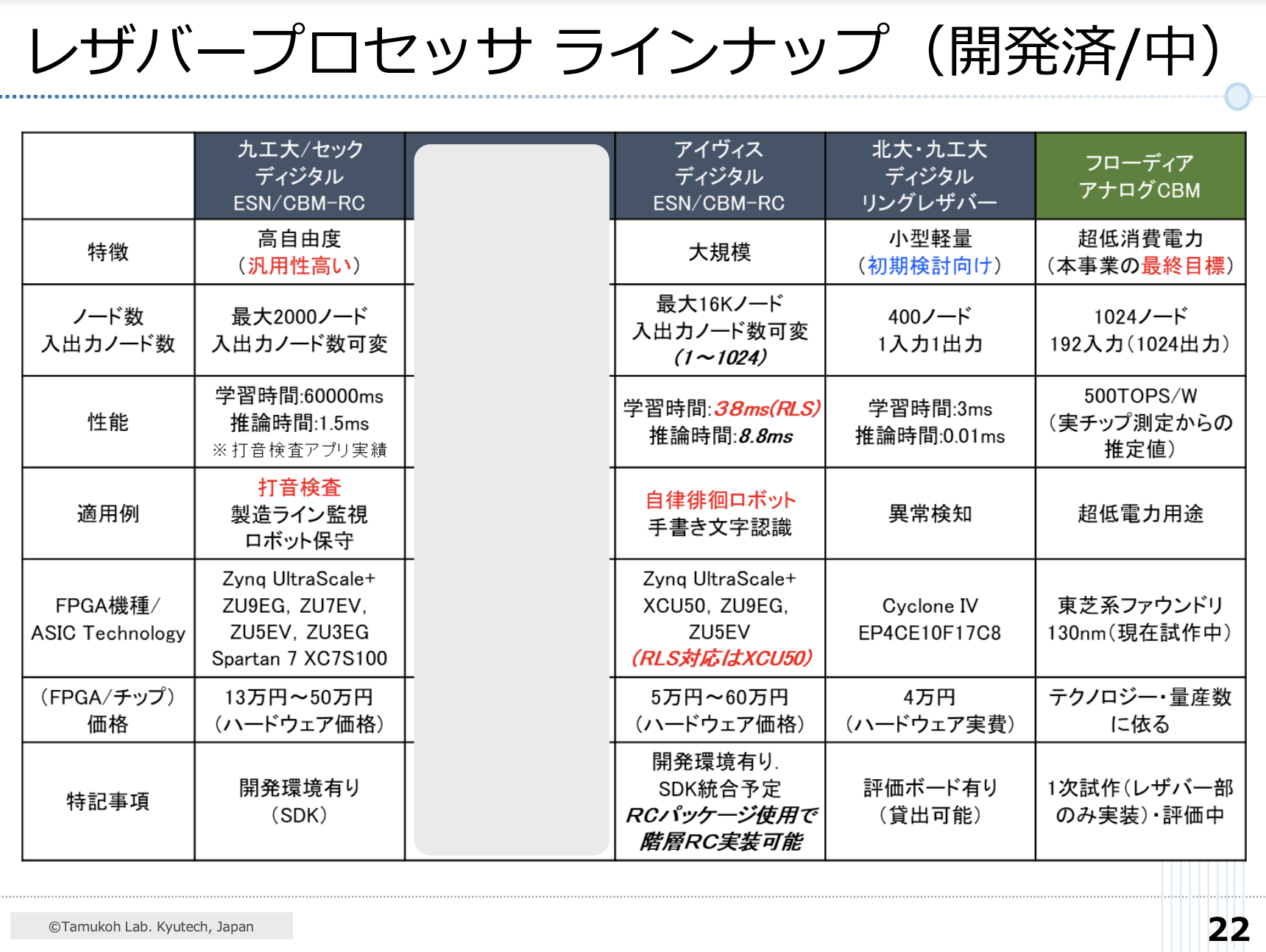

田向教授らは既にレザバー・コンピューティングのアナログ・チップ化とFPGA化に成功しており、RoboCupに出場したロボットの認識機能へ応用しているほか、開発したハードウェアをロボット開発者に提供すべく企業と共同でROS(Robot Operating System)パッケージ/SDKの提供も行っているとの話。更に次のステップとして、Synopsysの協力も得て世界初となるディジタル・レザバーチップ(ASIC)開発にも挑戦中だという。なおレザバーチップは田向教授以外にも複数のチームが開発しているということだった。

田向教授らの「エッジ指向型の脳型計算機システム」の研究は、エッジAI分野で大きな可能性を秘めている。期待を持って今後も引き続き注目していきたい。

■ホンダによるシステム検証の効率化事例

イタレーションサイクル短縮を目指したSilverによるシステム検証の効率化の取り組み

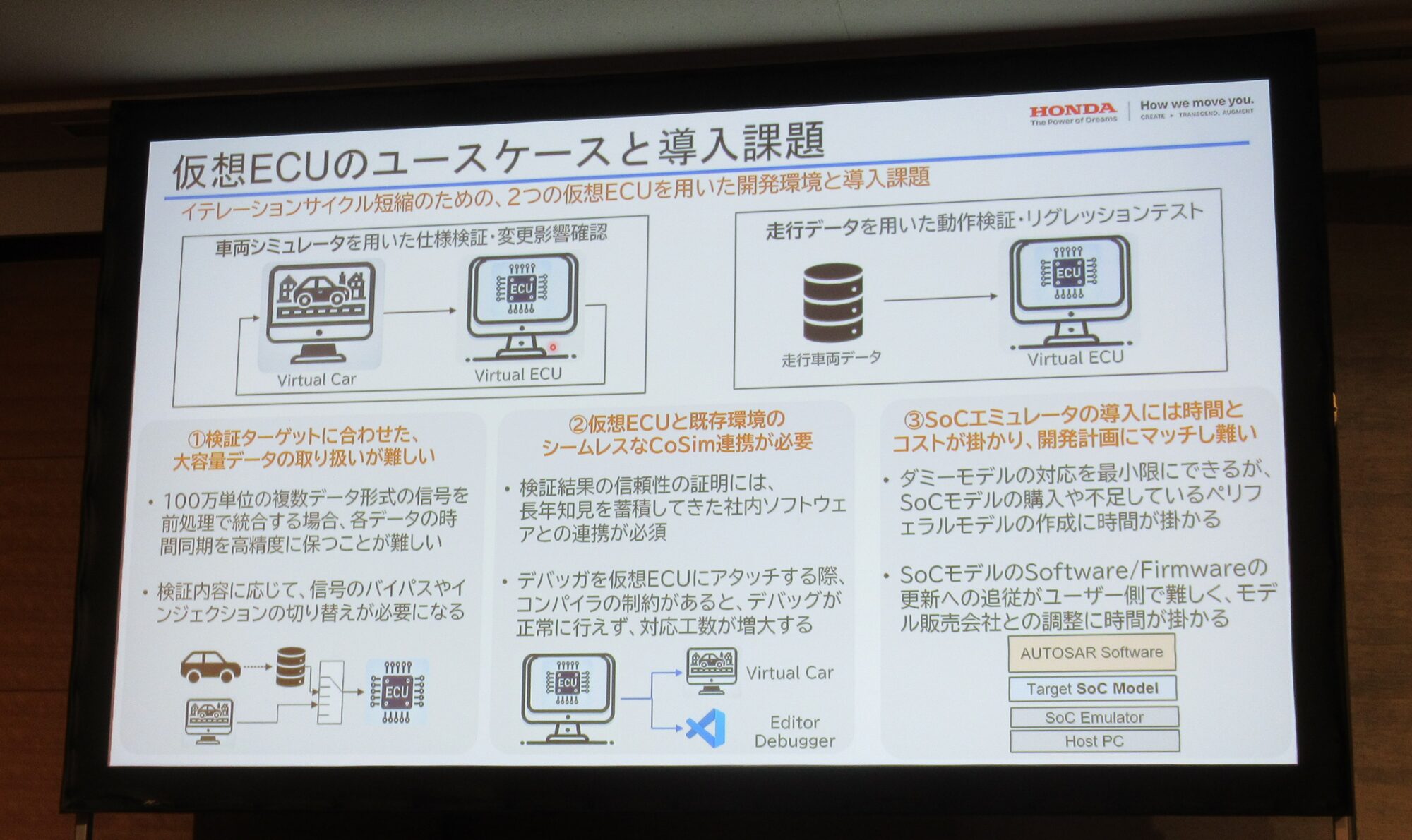

講演者の本田技研工業株式会社 電動事業開発本部 BEV開発センター ソフトウェアデファインドモビリティ開発統括部 先進安全・知能化ソリューション開発部 山辺 智晃(やまべ ともあき)氏は、ホンダに入社してから一貫してAD/ADAS開発に携わってきた人物。現在はSILSを使った仮想環境を使った開発プラットフォームの構築に取り組んでおり、AD/ADASの加速がミッションとなっている。講演では、イタレーション・サイクルにおけるバーチャル・テストの効率化事例を紹介してくれた。

山辺氏によると、現在の自動運転機能の開発はシミュレーション・シナリオが1,000万通りを超えるケースもあり、車載ソフト開発におけるV字フローの右側部分をいかに左側で仮想的にやるか、文字通りシフト・レフトが喫緊の課題となっている。そこでこれまで実施していた「MILS」や「SILS」を使った検証に代わり、より大きな範囲でソフトウェアの検証が可能なECUの仮想化に取り組んだ。

前車追従やレーンキープ機能のアプリケーション・ソフトの検証をターゲットにしたECUの仮想化においては、大きく下記3つの課題があり、Synopsysの「Silver」の導入によりこれら課題を克服した仮想ECU環境の構築を目指した。

・検証に用いるセンサー情報など100万単位で存在する外部データの取り扱いが難しい

・仮想ECUと既存環境のCo-Simが難しい

・SoCエミュレータの導入が難しい(時間とコストがかかる)

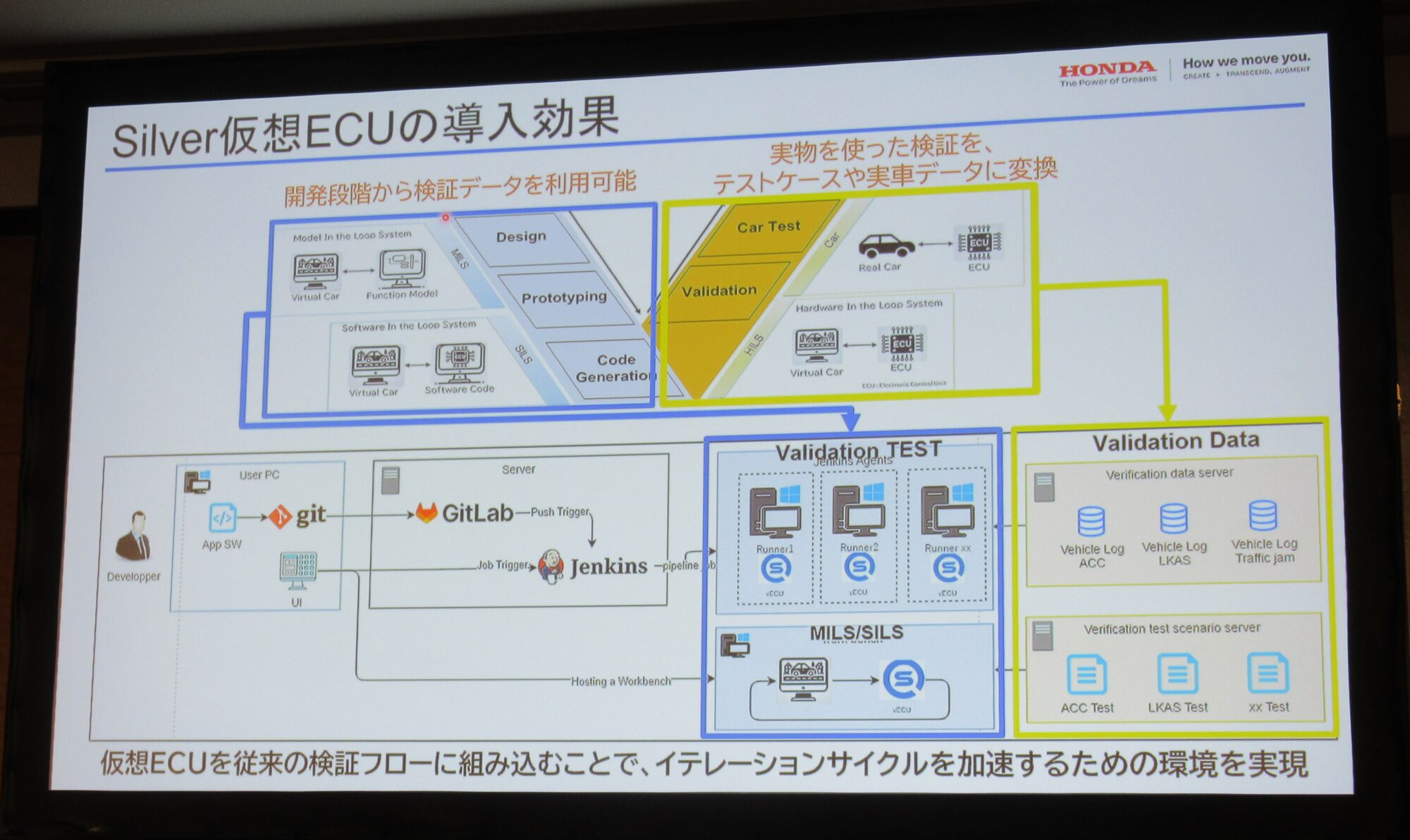

「Silver」を導入した結果、ホストコンパイルされたハードに依存しない仮想ECUにより、実際の車両データを用いた検証やVirtual Carを用いた検証が行えるようになった。それを踏まえて山辺氏は「Silver」の利点として下記3点を挙げた。

・100万単位の外部データをモジュール毎に管理して扱うことができる

・各種APIのサポートにより、既存環境と容易に接続することができる

・ペリフェラルなどモデルを作成することなく、自前のリソースのみでAUTOSAR領域の仮想化が可能

※AUTOSARに準拠していないサードパーティーIPのダミー・モデルも利用可能

また山辺氏は、V字フローの後半において実ECUを使った検証をValidation Dataとして変換・再利用することで、単一アプリケーションだけではなく様々なアプリケーションの検証に利用できるようになったと付け加えた。

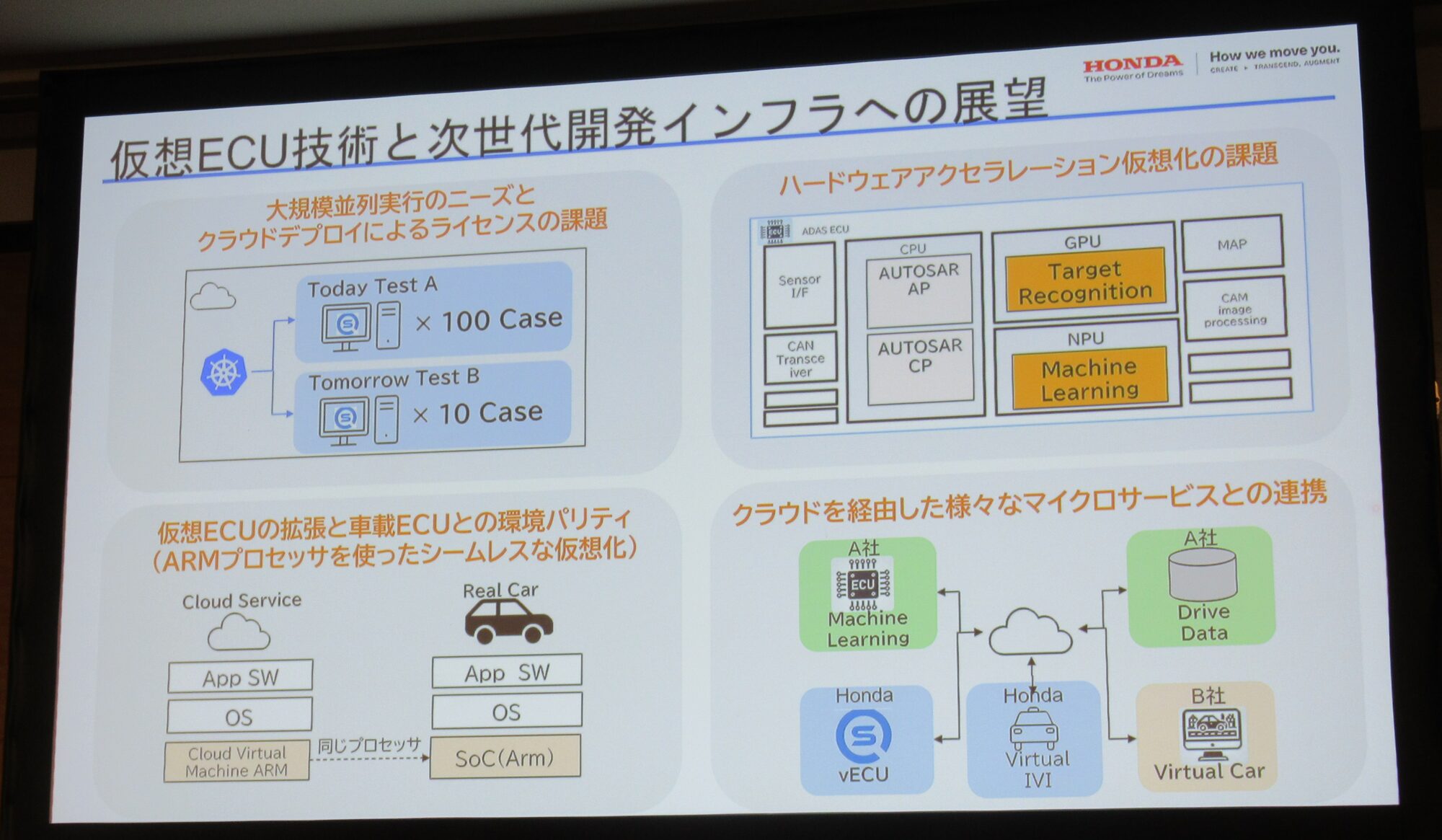

なおホンダでは仮想ECU技術の更なる活用として、クラウドでの大規模並列実行、GPU/NPUなどハードウェア・アクセラレーションの仮想化、ARMプロセッサを使ったシームレスな仮想化、クラウドを経由した他のサービスとの連携などを検討しているということだった。

■ソニーによるインプリメント・フローの改善事例

ソニーにおけるFusion Design Platformを用いたRTL-to-GDSII full flowの構築と設計適用事例

同講演はソニーセミコンダクタソリューションズ株式会社 モバイルシステム事業部 バックエンド設計部 ITS 5課 野田 直樹(のだ なおき)氏と同6課 加藤 豪(かとう ごう)氏の2名によるもの。はじめに加藤氏が設計フローの変更に至る背景を話し、その後に野田氏が新フローの事例を紹介してくれた。

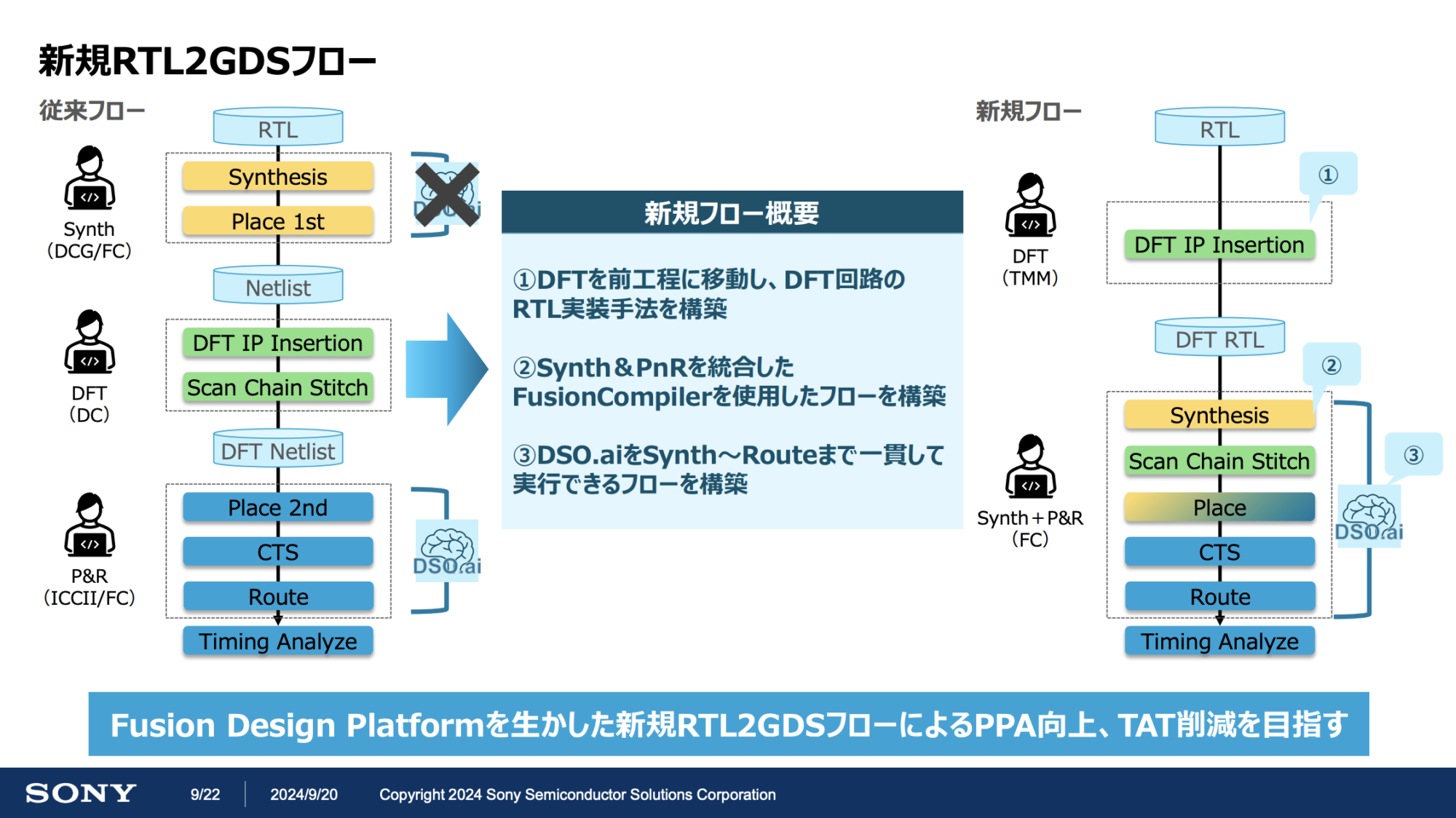

先に講演内容を要約すると、ソニーでは主力製品であるイメージセンサーのロジック回路の設計において、これまではDesign CompilerとIC Compilerを中心としたインプリメント・フローを活用していたが、ツールの進化に伴いSynopsysが打ち出した「Fusion Technology」を取り込みインプリメント・フローを改善。目標としていたTAT短縮とQR向上を実現し、すでに10製品以上の設計に適用しているという話。

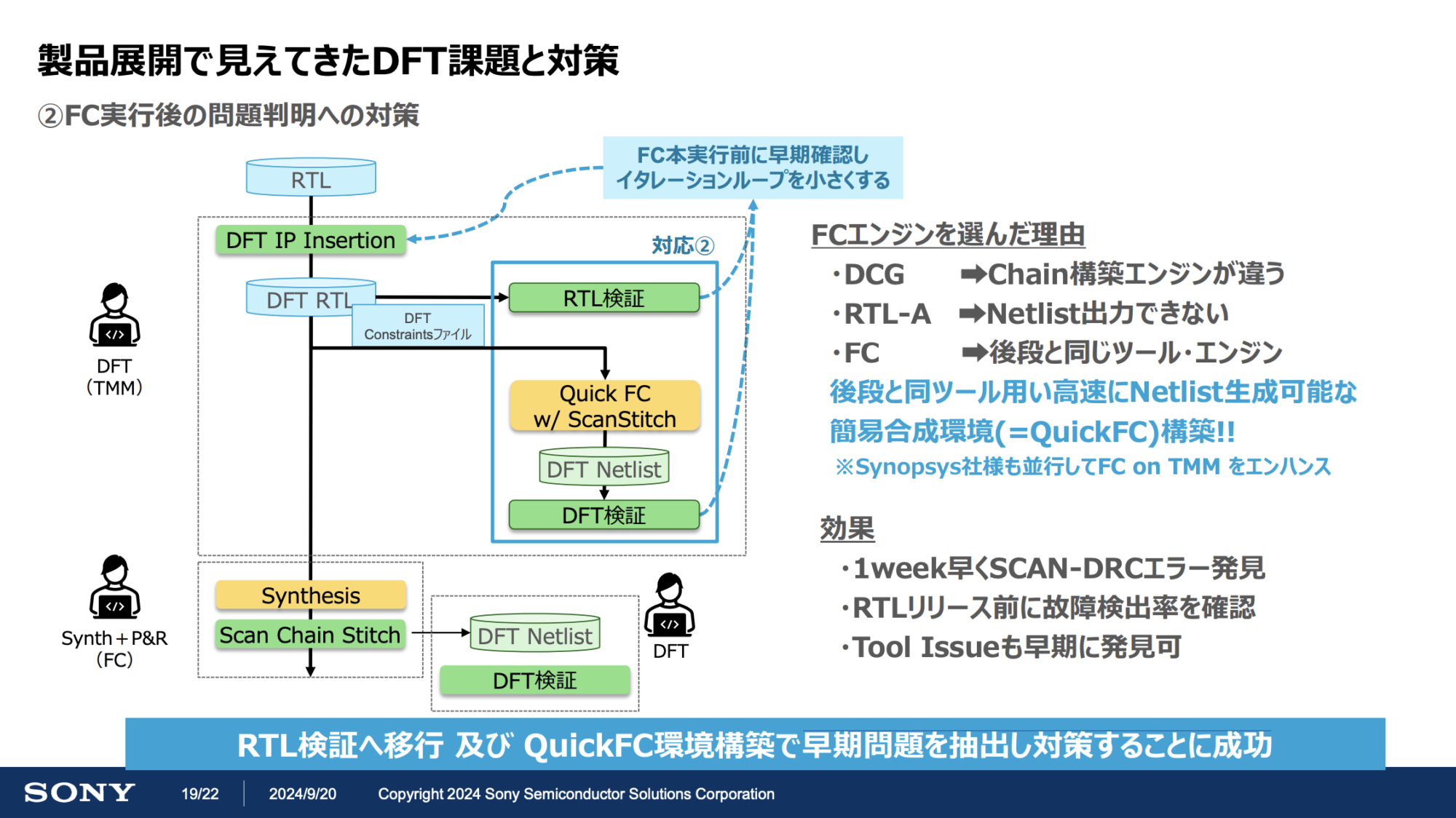

具体的なフロー変更の内容は下記スライドの通りで、これまで合成と配置配線の間に行っていたDFT挿入を「TestMAX Manager」を使いRTLで行い、「Fusion Compiler」を使って合成と配置配線を一気に行なう形にフローを変更した。加藤氏によると、これにより「テストと論理合成の融合」、「サインオフ工程とデザイン最適化工程の融合」が実現可能となるため、簡潔な新フローのもとツール間のイタレーションを減らすなどのTAT削減効果を期待できた。

もう一つ新フローで狙ったのはPPAの向上で、SynopsysのAI推論機能「DSO.ai」を合成から配線まで一貫して適用することでPPAの最適化を図った。加藤氏によると従来のフローでは合成と配置配線が分離していたため、「DSO.ai」の適用がうまくいかず逆に工数の増大を招いていたという。

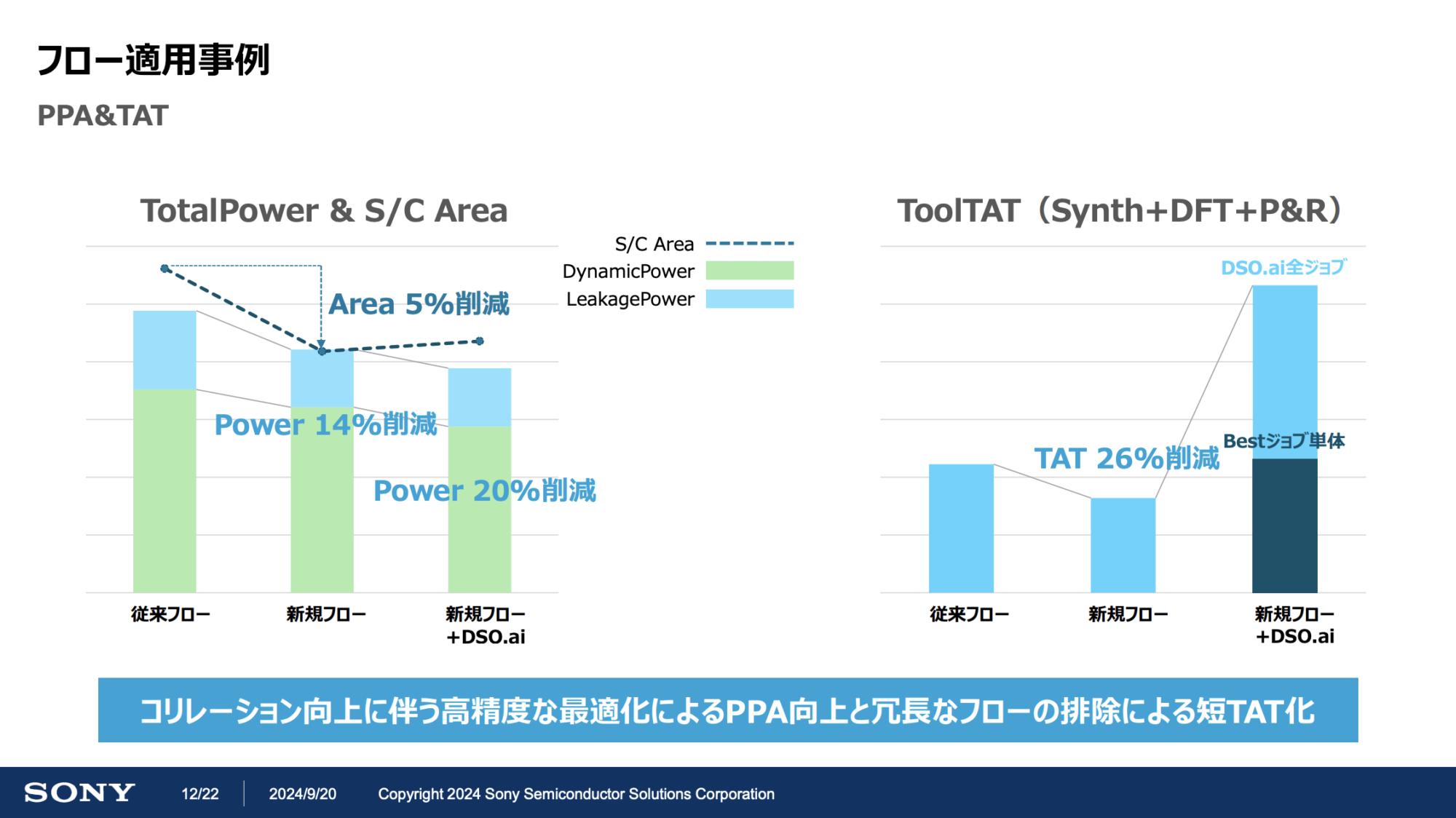

実際に「TestMAX Manager」と「Fusion Compiler」そして「DSO.ai」を用いた新フローを適用した結果が下記の図。回路規模1.8Mインスタンス、40nmプロセスのデザインをターゲットにした。

新フローによりTATは26%も削減することができた。更にエリアも5%削減、「DSO.ai」を用いることで全体工数は増えたがパワーは最大20%と大きく削減。またDFT回路の物理考慮によるPPAの向上も確認できた。

野田氏によると、改善された新フローによって既にこの2〜3年で10製品以上の設計が完了しているという話だが、フローの変更に伴い新たな課題も発生した。

一つは新規フローに関連するツール関連の問題の多発。これについてはSynopsysの協力を得てツールのエンハンスにより解消した。もう一つは、DFT回路のRTL実装不備で配置配線後に問題が発覚しRTLまで手戻りが発生してしまうという問題で、これについては一部の検証項目をRTL検証へ移行、併せて簡易Fusion Compiler環境を立上げ、Netlistを生成し事前にDFT検証を行うという形で早期問題を抽出し対策することに成功したとのこと。フロー変更により大きな成果を得たが、その裏での様々な苦労・工夫が垣間見える現場感あふれる話だった。

■富士通によるエミュレータ活用ノウハウの紹介

大規模プロセッサ「FUJITSU-MONAKA」のシステムレベル検証へのZeBu Server 5適用

講演者の富士通株式会社 富士通研究所 先端技術開発本部 プロセッサ開発統括部 松井 宣幸(まつい のりゆき)氏は、2006年から長きに渡りプロセッサ開発の全体検証を担当している人物。講演では富士通の最新プロセッサ「FUJITSU-MONAKA」のシステム・シミュレーションにおいて使用した「ZeBu Server 5」の活用ノウハウについて語ってくれた。

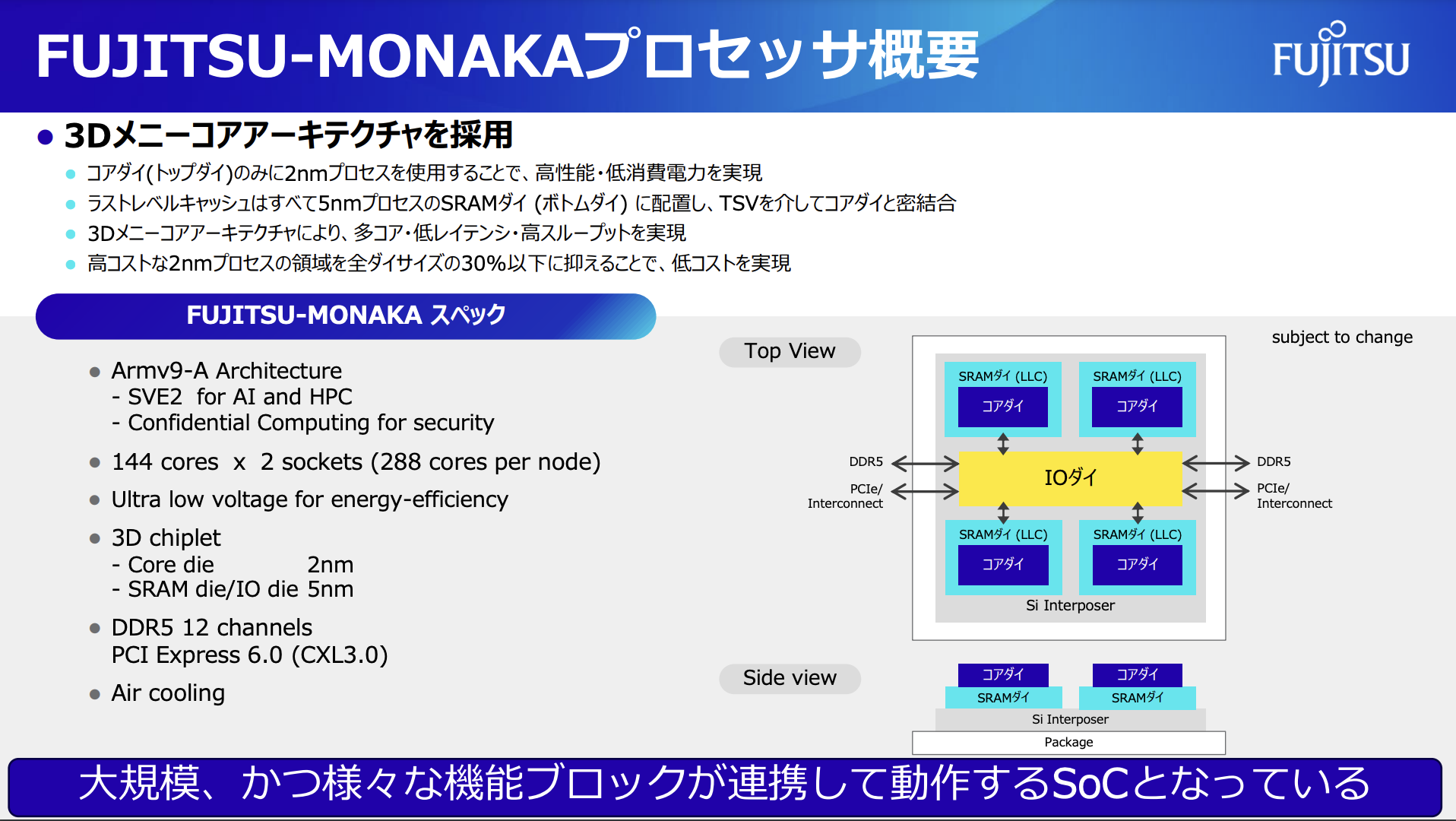

「FUJITSU-MONAKA」 は、スパコン富岳に搭載されている「A64FX」に次ぐ最新のHPC向けプロセッサで、富士通独自開発のArm V9コアを144個搭載。コアダイは2nmプロセス、SRAMダイとIOダイは5nmプロセスという形で異なる3つのダイを組み合わせた3Dメニーコア・アーキテクチャを採用している。数十億ゲートクラスの大規模プロセッサの開発において、リスピンを避けるためにはプレシリコンのシステム検証がとても重要であると松井氏。富士通では下記3つのシステム検証を行いチップの一発完動を目指している。

・実デザインを使用した機能検証

・性能、消費電力の妥当性確認

・OS /実アプリを使用したシステム動作確認

これらシステム検証を行う上でのノウハウとして松井氏は、エミュレータの運用ノウハウと検証の効率化ノウハウを紹介してくれた。

大規模エミュレータ運用ノウハウ

まず、必要なコンパイルリソースを最初から準備しておくことが重要と松井氏。「FUJITSU-MONAKA」の開発では特にFPGA P&Rステップのリソース確保を重視したとのこと。また、コンパイルの安定と時間短縮のためには、DUTの性質を考慮したコンパイル・パラメータの探索が重要で、その最適化にもノウハウが必要となるためSynopsysによるサポートが欠かせないものになっているという。

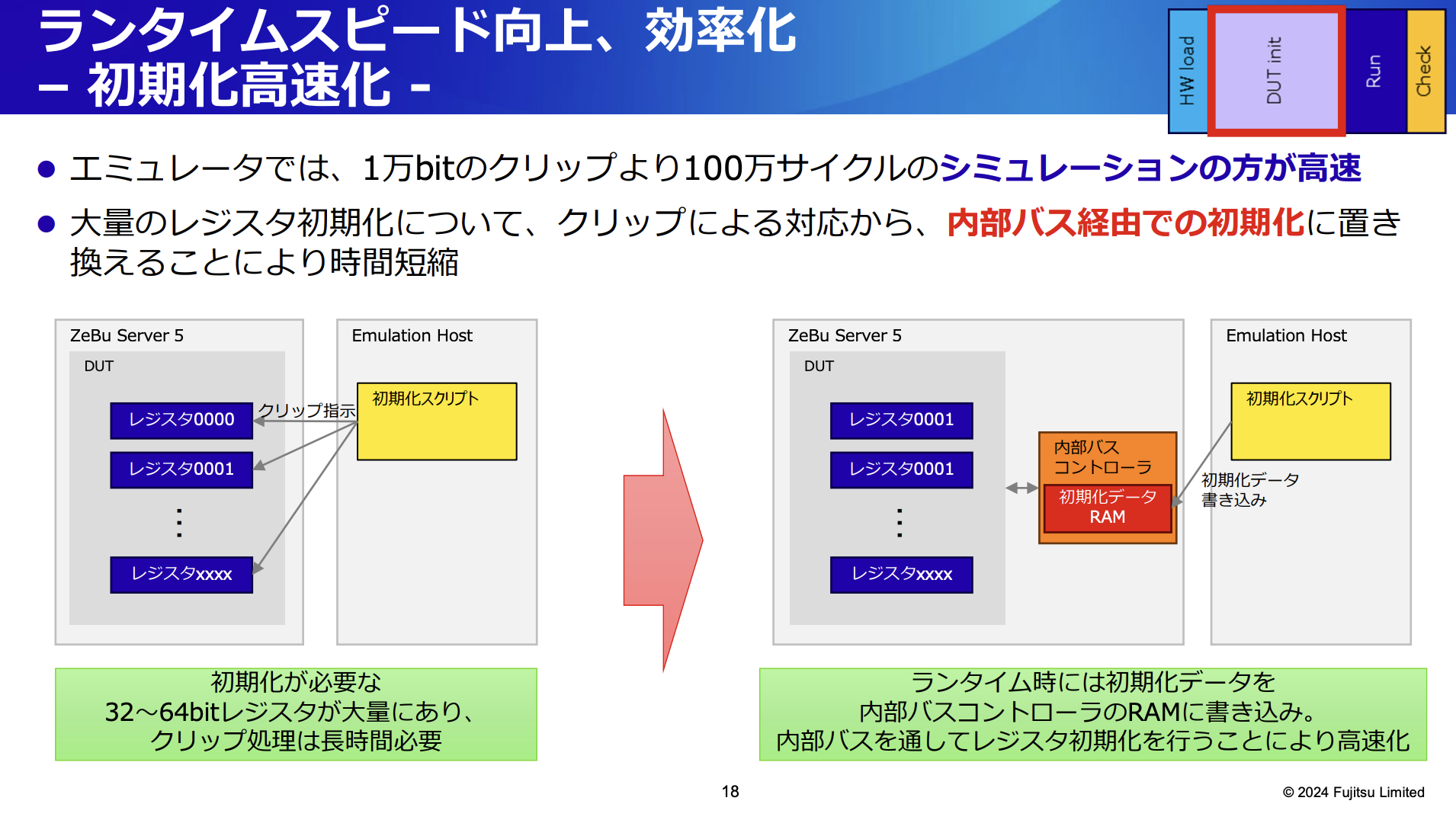

ランタイムスピードの向上については、各シミュレーション実行ステップに対して個別に効率化を図っていて、初期化の高速化(プロセッサは大量の初期化あり)は、クリップ処理を内部バス経由での初期化に置き換えることで実現。短いテストシナリオを実行する場合は、「セーブ&リストア機能」の活用が有効で初期化ステップを省略して2倍のスループットを実現したケースもあるということだ。

なお松井氏によると、「ZeBu Server 5」の動作周波数はRAMの使われ方で大きく変わるため、非同期RAMの同期化、RAMのビット幅、ポート数の最適化などの対処により高速化が可能。「FUJITSU-MONAKA」の開発では立ち上げモデルにおいてテストベンチ側の記述修正により、動作周波数を400KHzから1.3MHzへと3倍以上引き上げることに成功したという話だ。

検証の効率化ノウハウ

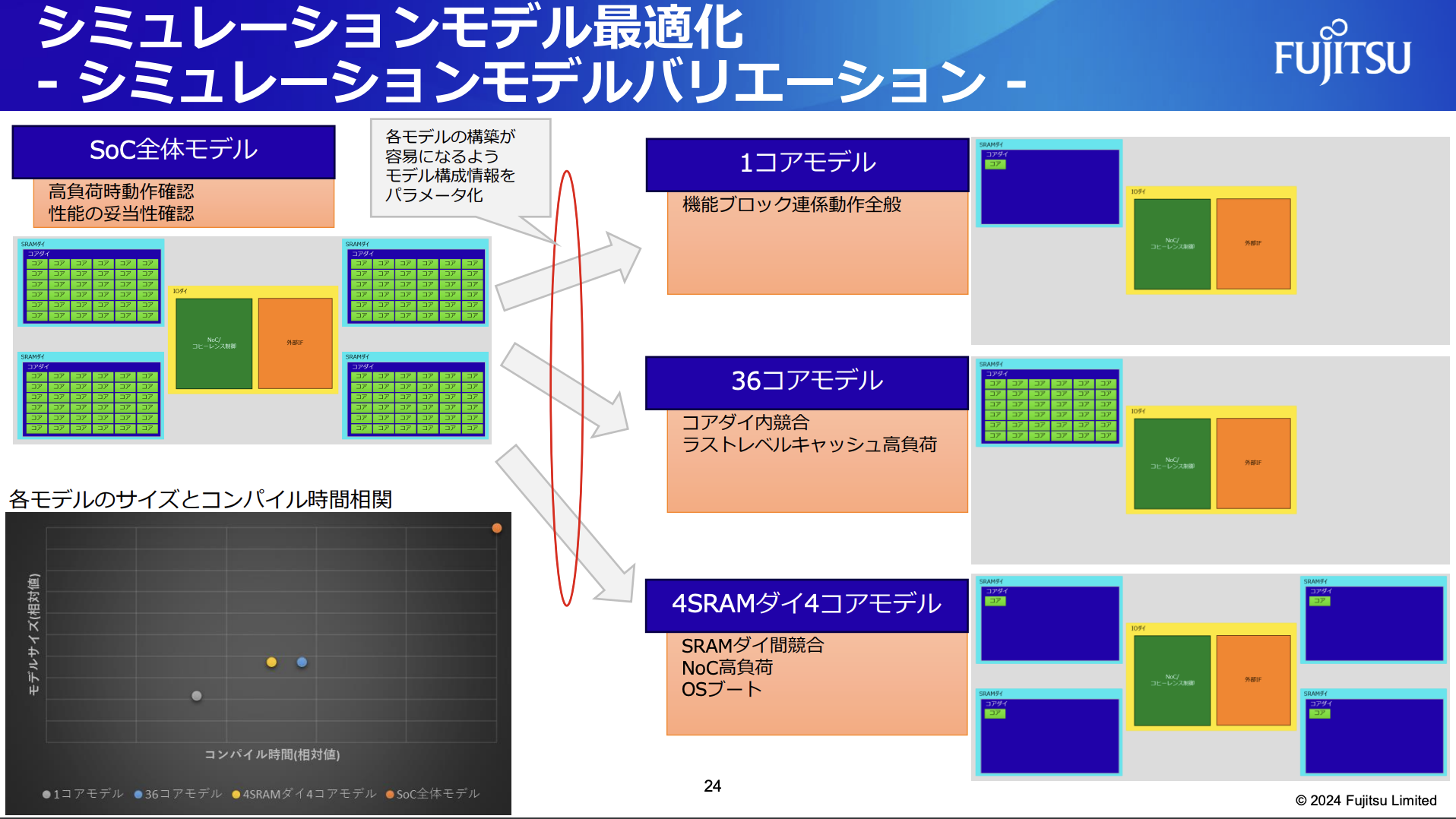

検証の効率化ノウハウとして松井氏がまず指摘したのは、検証項目に合わせたモデルの使い分け。例えば、IOの検証であれば144コアのうちIO制御を行う1コアだけあればいい(残りの143コアは不要)。小さなモデルを利用すれば、「ZeBu Server 5」をマルチユーザーで実行できエミュレータ・リソースの有効活用にも繋がるとした。

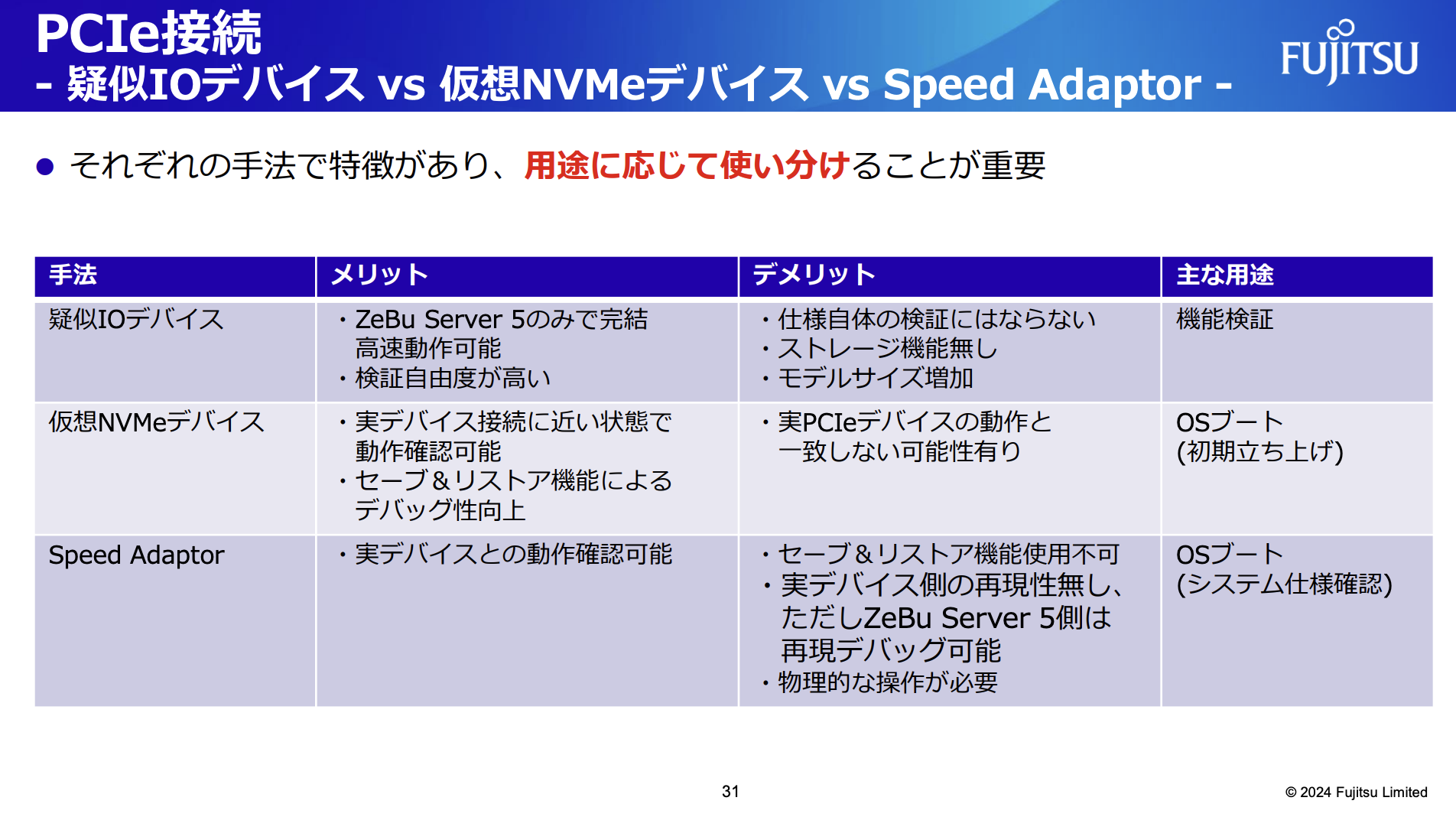

また、プロセッサの外部インタフェースについては、各インタフェースの性質に合わせた対向デバイス、接続方法を用意する必要があり、「FUJITSU-MONAKA」の開発においてはPCI Express用に下記図のような3種類のデバイスを用意しシステムの機能検証ならびに仕様検証を行なった。

松井氏によると、「ZeBu Server 5」のハードウェアは非常に安定していて、導入以降95%以上の稼働率で運用しているとのこと。故障が発生しても故障個所のみ切り離して運用を継続できるという。

なお「ZeBu Server 5」でプレシリコンのシステム・シミュレーションを行なった「FUJITSU-MONAKA」は、2027年に市場投入される予定。既に「FUJITSU-MONAKA」を中心としたAMDとの協業なども発表されており、次世代のAI/HPC向けのコンピューティング基盤として大きく期待されている。

※日本シノプシス合同会社

※九州工業大学 田向研究室

※本田技研工業株式会社

※ソニーセミコンダクタソリューションズ株式会社

※富士通株式会社

= EDA EXPRESS 菰田 浩 =

(2024.12.05

)