マルチコア向けSW開発、パワー解析、検証IP、UVMコード生成、イマドキなツールを集めるネクストリーム社

2017年9月1日、各種海外EDAツールを取り扱う株式会社ネクストリームは、新横浜のホテルで同社初となるプライベートセミナを開催した。ここでは同セミナーの様子をレポートする。

セミナーは富士通ネットワークプロダクト事業本部の谷口正樹氏(モバイルネットワーク事業部長兼次世代ソリューション統括部長)の基調講演でスタート。

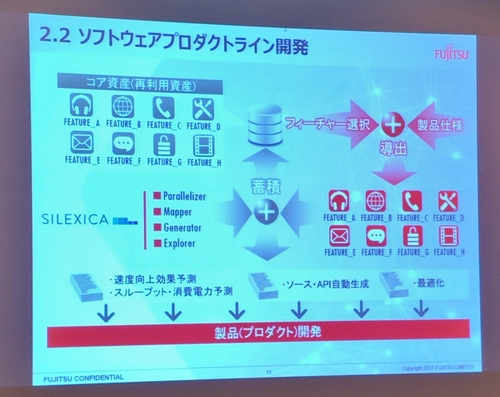

谷口氏の講演は次世代移動通信「5G」に関する話。谷口氏はコンピューティング処理の一部を無線基地局などのエッジで行う事で超低遅延を実現するMEC(Mobile Edge Computing)を取り上げ、MECは今後5Gと共に伸びて行き、5Gを利用する様々なユーザーに向けたパーソナルサービス/個別最適化ビジネスが発展するだろうと語った。また谷口氏は同社におけるソフトウェアプロダクトライン開発に関する取り組みについて紹介。同社ではネクストリームの提供するSW開発ツールの開発元Silexica社の協力を得て製品開発のプロセス改善を進めているという。

ネクストリームの講演としては、同社の取り扱う下記4製品が紹介され、合わせてユーザーによる講演も行われた。

・静的消費電力解析ツール:Intel Docea Power Analytic(iDPA)

・検証IP:SmartDV社各種検証IP

・UVMコード生成ツール:Vtool(Machina/Cogita)

・マルチコア向けSW開発ツール:SLX Tool Suite

Intelの提供している「iDPA」は動作シナリオからモデルを作り静的に消費電力を解析するWebベースのツールで、一般的に静的消費電力解析で利用されている「Excel」と比べて、扱えるデータ・サイズ、データ構成(データのつくり)、データの一貫性などの面で優れており、Excelでやりがちなリンクミスを防ぐデータ・チェック機能や、データへのアクセス権限を管理するセキュリティ機能など運用においても利用価値の高い機能が備えられている。既にIntel社内には同ツールのユーザーが相当数存在しているようだ。

SmartDVの検証IPは同社の200人以上のエンジニアによって開発されている全てオリジナルの製品。MIPI、ネットワーク、インターコネクト、ストレージ、メモリ、オートモーティブなど各種検証IPを幅広く提供しており、その種類は100種以上、主要な規格は一通り抑えておりUSB3.1やDDR5などの新製品のリリースも予定されている。同社の検証IPにはコンプライアンス・テスト・スイートと機能カバレッジ・モデルが無償で提供されるため、ユーザーにとっては比較的導入障壁が低い。また自社開発ならではの手厚く素早いサポートがユーザーから高い評価を得ているようだ。SmartDVは、通常のシミュレーション用の検証IPの他に「SimXL」という合成可能なエミュレータ/FPGA向けの検証IPも用意している。

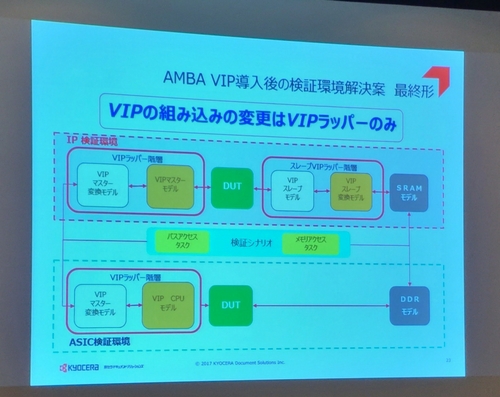

SmartDVの検証IPを導入した京セラドキュメントソリューションズ株式会社の清瀬氏によると、過去資産を活用したダイレクト検証が必須の同社の検証環境とランダム検証を前提として作られたSmartDV社の検証IPには少なからずギャップが有ったが、SmartDVはすぐに検証環境にVIPを組み込むための変換モデルを用意。最初に導入したAMBAの検証IPは課題を乗り越え運用に成功したとの事。SmartDVの検証IPの品質とサポート体制に満足した同社はDDRの検証IPも追加で導入したという。

UVMユーザーのためのツールを手掛けるVtoolは、UVMコードを自動生成する「Machina」とログ解析のための可視化ツール「Cogita」を提供している。「Machina」の一番のアピール・ポイントは、UVMの複雑さをツールが吸収してくれるという点で、UVMに不慣れな初心者でもGUIベースで用意にUVMを作成可能。本来UVMが備えている再利用性を活かす事ができるようになる。

VtoolのユーザーであるCMエンジニアリングの野村氏によると、「Machina」を利用すれば誰が作っても定型のテストベンチが作成できるため、同社では海外子会社でのオフショア開発でコーディング・ルールとして「Machina」を活用しているとの話。これによりコードの品質が上がりテストベンチの作成工数も1/3程度に削減できているという。また、「Cogita」はシミュレーションのログ解析で活用しており、エラー解析やボトルネックの特定などに役立っているという事だった。

Silexicaの提供するマルチコア向けソフトウェア開発ツール「SLX Tool Suite」は、欧州で受賞歴のある製品で簡単に言うとシングルコア向けのコードのマルチコア化を自動化してくれる。シングル・スレッドで記述されたC/C++コードに対して並列可能個所を解析し、ターゲットのマルチコア・リソースに対して最適な形で分割、マッピング、コード生成と一連のマルチコア化作業を手助けする様々な機能が「SLX Tool Suite」に備えられている。最新のバージョンでは、スレッド化されたコードにも対応したほか、新たなキャッシュ解析機能も追加、またFPGA/高位合成向けの解析機能(ハード化対象の解析)もサポートされた。Silexicaは将来的にプロセッサ単体ではなくシステム全体の解析を目指しているという話だ。

ユーザー事例を発表した株式会社リコーの木村氏は、エンベデッド・ビジョン・システムの開発で「SLX Tool Suite」を活用。OpenCVの組み込み化にあたり、その最適化を検討するためにOpenCVライブラリの動的解析に「SLX Tool S

uite」を使い、変数・関数の依存関係の確認を行った。その結果OpenCV内部の並列化可能箇所の推定に成功。コードの変更無しでパフォーマンスを向上できると判断した。木村氏は、OpenCVのアルゴリズムは複雑すぎて到底人の手で解析できるものではなく、「SLX Tool Suite」はOpenCVを動的解析できる世界で唯一のツールと評した。なお木村氏は高位合成を用いたOpenCVの更なるパフォーマンス向上に取り組んでいるという話で、その事例については同氏が実行委員長を務めるDesign Solution Forum 2017(10/13開催)にて発表する予定だという。

uite」を使い、変数・関数の依存関係の確認を行った。その結果OpenCV内部の並列化可能箇所の推定に成功。コードの変更無しでパフォーマンスを向上できると判断した。木村氏は、OpenCVのアルゴリズムは複雑すぎて到底人の手で解析できるものではなく、「SLX Tool Suite」はOpenCVを動的解析できる世界で唯一のツールと評した。なお木村氏は高位合成を用いたOpenCVの更なるパフォーマンス向上に取り組んでいるという話で、その事例については同氏が実行委員長を務めるDesign Solution Forum 2017(10/13開催)にて発表する予定だという。