Synopsysがシリコン実装前の歩留まり解析/最適化を実現する革新的な新製品「PrimeYield」を発表

2019年5月28日、SynopsysはSoCの歩留まり解析および最適化ツール「PrimeYield」の提供開始を発表した。

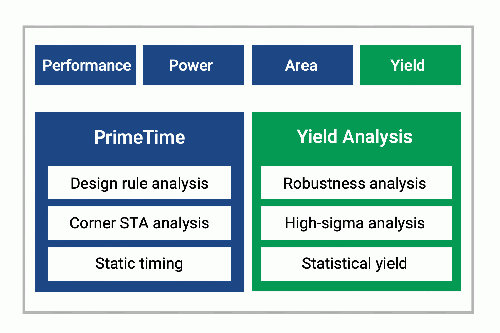

Synopsysによると新製品「PrimeYield」は、特許技術の高速な統計的手法とマシンラーニング技術によって、これまでは不可能とされていたシリコン実装前の完全な統計的歩留まり解析を実現するもので、Synopsysはをデザイン・サインオフを再定義するブレイクスルー・ソリューションであると主張する。

従来は、統計的シミュレーションを完全に実行するには数日ないし数週間という膨大な時間を要し、その適用範囲も僅か数十セルが限界とされていた。しかしSynopsysは、開発した特許技術「パラメトリック歩留まり解析技術」と「統計的相関性モデリング技術」により、統計的歩留まり解析および最適化の適用範囲を数億セルにまで拡大。合わせてマシンラーニング技術を用いる事で、シミュレーションの劇的な高速化を実現した。これにより、大規模なSoCに対してもリコン前の歩留まり解析を実行することが可能となった。Synopsysは「PrimeYield」の実現する歩留まり解析を前倒しは、設計品質の面でも製造コストの面でもインパクトが大きいとしている。

※画像はSynopsys社Web上のデータ

Synopsysの説明によると、「PrimeYield」は「フルチップ・パラメトリック歩留まり解析技術」により、モンテカルロ・スタティックタイミング解析よりも1,000倍高速な統計的歩留まり解析が可能。マシンラーニング技術により、歩留まりへの相関性と感受性が統計的に高いとされているクリティカルなセルを短時間で特定することができるという。

= EDA EXPRESS 菰田 浩 =

(2019.06.04

)