産総研と東京大学が共同で「AIチップ設計拠点」を設置、中小ベンチャー向けに設計環境を提供

2018年12月27日、産総研のAI chip Design Laboratory(以下、産総研AIDL)と東京大学 大規模集積システム設計教育研究センター(以下、VDEC)は、AIチップ開発の加速を目的とした「AIチップ設計拠点」を東京大学本郷キャンパス内に設置したことを発表した。

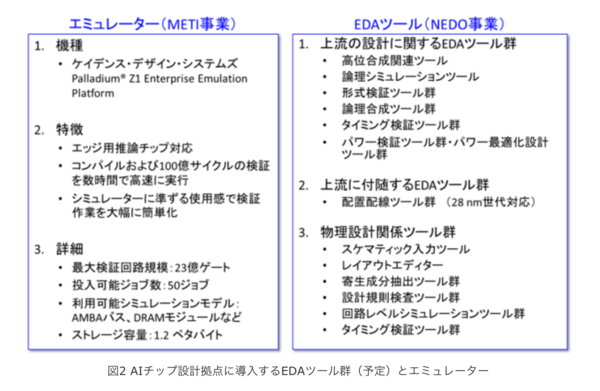

産総研AIDLと東大VDECが作った「AIチップ設計拠点」は、経産省およびNEDOの助成事業として実現されたもので、AIチップ開発に必要なEDAツール、エミュレーターなどを整備。設計フローやリファレンスデザインなども含めて中小・ベンチャー企業に環境を提供する。また「AIチップ設計拠点」では、蓄積される設計資産やノウハウも提供すると同時にAIチップ設計者の人材育成も行うという。

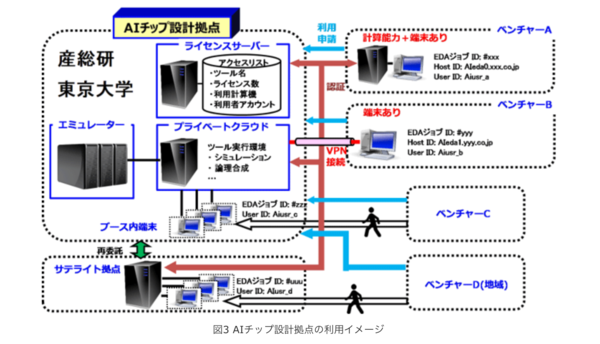

「AIチップ設計拠点」は、下記の3通りの形態で構築した設計環境を提供する計画で、高位合成ツールから論理合成、配置配線、物理検証など一連のEDAツール環境と合わせてCadenceのエミュレーター「Palladium Z1」も利用できる。

・ライセンスサーバー

・プライベートクラウド

・地域サテライト拠点内のブース

※画像は産総研発表資料のデータ

「AIチップ設計拠点」の予約ウェブサイト(URL: http://www.ai-chip-design-lab.org)は平成31年3月頃のオープン予定。4月以降に利用可能となる。

= EDA EXPRESS 菰田 浩 =

(2018.12.28

)