CadenceがSoC開発のデバッグ工数削減を睨んだ新製品「Indago Debug Platform」を発表

2015年4月30日、Cadenceは、デバッグ・ツールの新製品「Indago Debug Platform」を発表した。

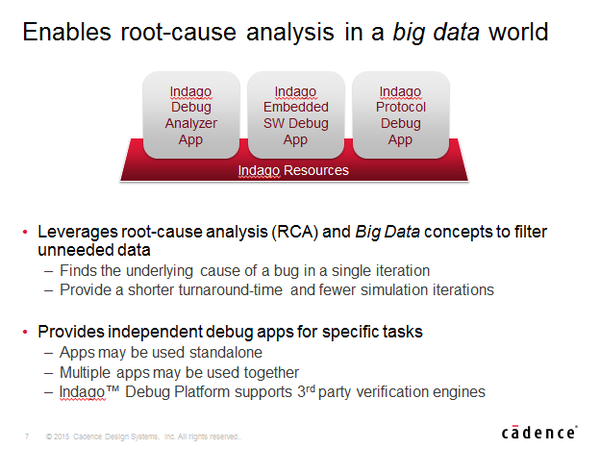

「Indago Debug Platform」は、Cadenceのフロントエンド設計ツール群「System Development Suite」の一部として提供されるデバッグ用のツール環境で、下記3種類の個別のツールによって構成されている。

・Indago Debug Analyzer

・Indago Embedded SW Debug

・Indago Protocol Debug

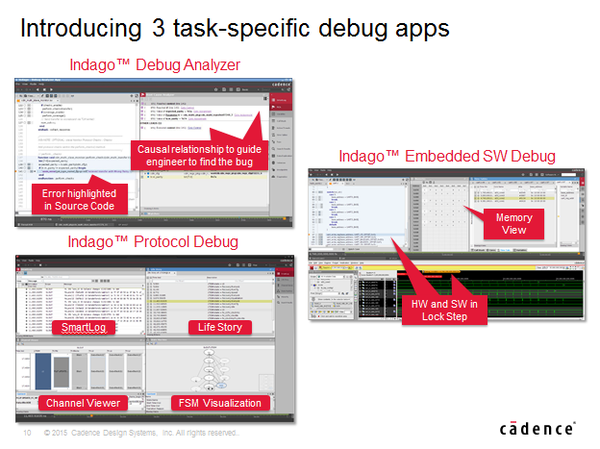

「Indago Debug Analyzer」は、デザイン本体のみならずテストベンチも含めた形でのデバッグを実現するもので、SystemC Verilog、e、SystemCなど各種言語で記述されたテストベンチをデバッグできるほか、UVMライブラリの変数を解析する仕組みなどUVMデバッグ用の仕組みも用意されている。テストベンチもデバッグ対象としてデザインとテストベンチを同期させてインタラクティブにデバッグ出来るというのがこのツールの特長と言える。

「Indago Embedded SW Debug」は、SWも含めたデバッグSoCレベルのデバッグを実現するもので、SoC上で動くHWとSWをリンクさせて同期させながらステップ・バイ・ステップでデバッグする事ができる。同ツールでSW本体のデバッグも可能だが、HWのデバッグにおいてSWも考慮するというのが想定されている利用法である。

「Indago Protocol Debug」は、AMBAなどオンチップ・バスに主眼を置いたプラットフォーム・ベース検証のためのデバッグ・ツールで、デザイン内の各機能ブロック間やデザインとテストベンチ間、検証IP間などでオンチップバスを介して行われるデータのやり取りを可視化する事ができる。

これら3つのツールは、それぞれ個別に購入でき他社の検証ツールでも利用する事が可能となっているが、検証エンジン、検証IPへの対応において当然ながらCadence製品向けに最適化されている。

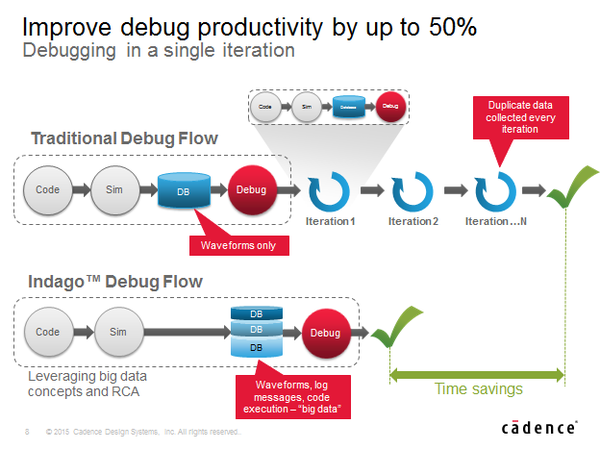

Cadenceはこれらツールをまとめた総称として「Indago Debug Platform」と呼んでいるが、「Indago Debug Platform」の狙いは言うまでもなくデバッグ工数の削減で、今日のSoC開発では限界となりつつある旧来手法の力任せのRTLデバッグの刷新を目指している。そのためにCadenceは「Indago Debug Platform」に「RCA:Root cause analysis」の技術を導入しバグの原因解析手法を提供しているが、その代表的なアプローチとして「ビッグデータの活用」というコンセプトがある。

Cadenceの言うビッグデータとは、デバッグに役立てる各種データの総称で波形データに限らずシミュレーターやフォーマル検証ツールなど各種検証ツールやSWデバッガの吐き出すログなどの情報を集めビッグデータとして活用するために整理、分類する仕組み「SmartLog」を用意している。またシミュレーションを再実行せずに時間を戻すリバース・デバッグ機能も用意しており、これら機能を活用することで無駄なイタレーションを減らしデバッグ効率を高める事が可能になるという。

※画像は全てCadence提供のデータ

Cadenceによると「Indago Debug Platform」を用いる事でデバッグ工数を最大50%削減できるという事だが、IPや機能ブロックなどデザイン内のデバッグだけではなく、UVMなど先進的なテストベンチのデバッグ、HWとSWを組み合わせた境界領域のデバッグなど、SoC開発で行われる各種デバッグを単一のツール・プラットフォームで一気通貫に実現できる点が「Indago Debug Platform」の最大の魅力と言えるだろう。

「Indago Debug Platform」は今年6月から正式リリースの予定で、現在先行ユーザーに限定的に提供されている。ツールの一部機能は既に日本国内のユーザーにも利用されているという話で、7月17日に予定されているCadenceのプライベート・イベント「CDNLive Japan」ではユーザーの事例を聞くことができるかもしれない。

※日本ケイデンス・デザイン・システムズ社

= EDA EXPRESS 菰田 浩 =

(2015.05.15

)