Xilinxが16nm FPGAの新ファミリ「UltraScale+」を発表

2015年2月24日、XilinxはTSMC 16nm FinFET+プロセスで製造される新FPGAファミリ「UltraScale+」を発表した。

プレスリリース文

今回発表された

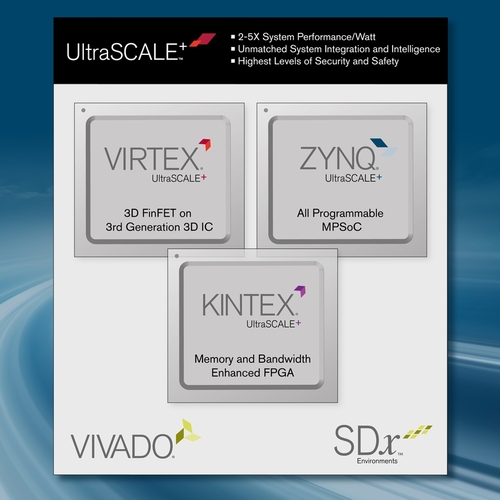

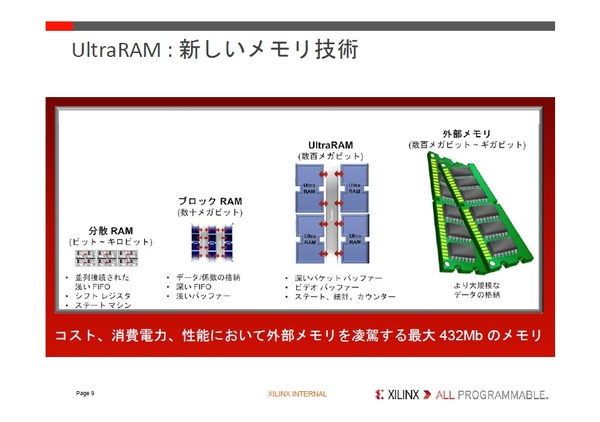

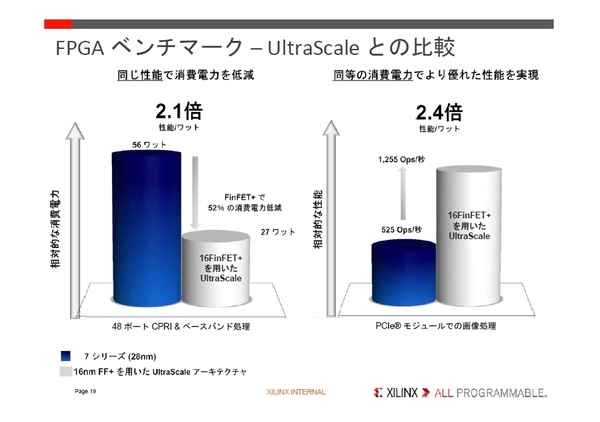

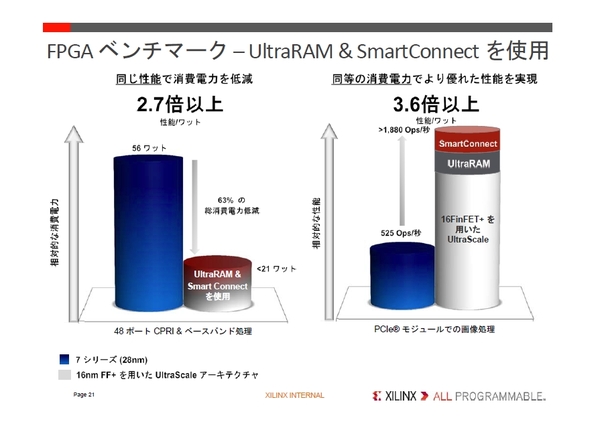

新FPGAファミリ「UltraScale+」を構成するのは、ハイエンドFPGA「Virtex UltraScale+」シリーズ、ミッドレンジFPGA「Kintex UltraScale+」シリーズ、そしてARM搭載FPGA「Zynq UltraScale+」の3系統で、新しいVirtexはシリコン・インターポーザを用いた2.5次元パッケージ技術とFinFET技術を組み合わせて実現。Xilinxはこれを「3D-on-3D」と称している。新ファミリ「UltraScale+」は既存のUltraScaleアーキテクチャをベースに新たなメモリ技術「Ultra RAM」とインターコネクト最適化技術「SmartConnect」によって性能向上が図られており、既存の28nm製品と比較して1ワット当りの性能が2-5倍向上されている。

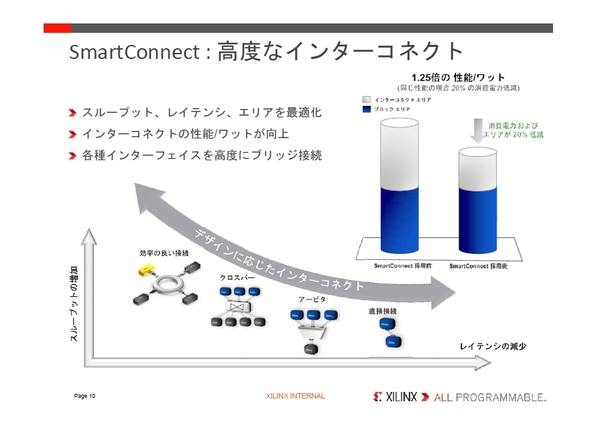

「SmartConnect」は開発環境「Vivado」に実装された新機能で、デザインの要求性能に応じてインターコネクト・トポロジを自動的に最適化することができる。これによりパフォーマンス、消費電力、インターコネクトのロジック面積を20-30%改善する。

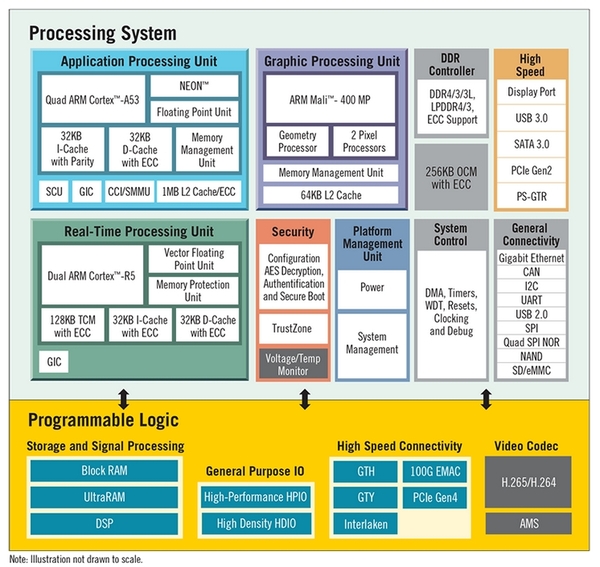

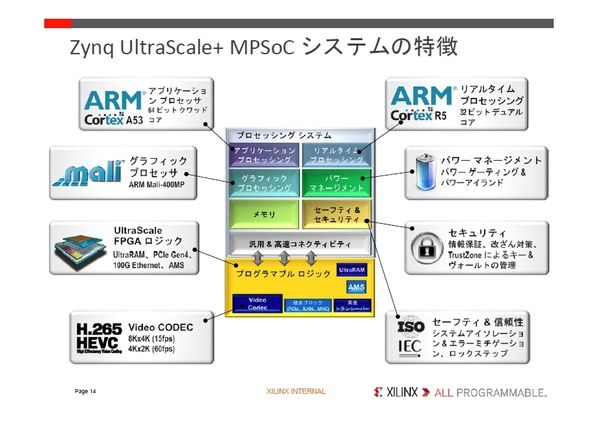

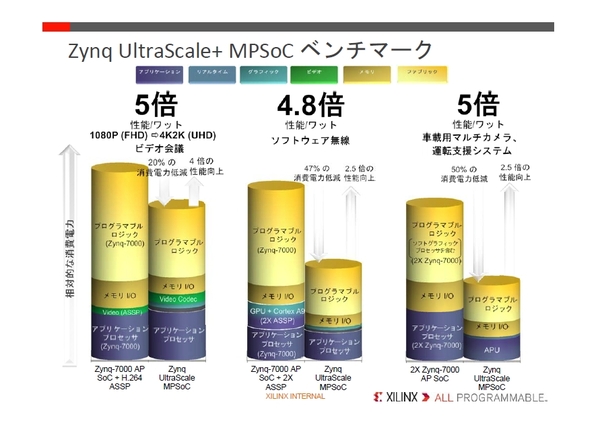

新しい「Zynq UltraScale+」には、最大1.3GHzで動作するARMのクワッドコア Cortex-A53、最大600MHzで動作するARMのデュアルコア Cortex-R5、そして最大466MHzで動作するARMのGPU Mali-400MP2が搭載され、既存のZynqと比較して1ワット当たりのシステム性能が最大5倍になった。

また、「Zynq UltraScale+」では、パワー・マネジメント機能が追加され、ARM TrustZoneによるセキュリティ機能が強化されたほか、リアルタイム・プロセッシングを行うCortex-R5に対して機能安全向けの対応も施された。またH.265/264ビデオ・コーデックのハードIPも用意された。このハードIPは「Kintex UltraScale+」にも搭載される。

Xilinxによる新ファミリ「UltraScale+」のベンチマーク結果は以下の通り。

新ファミリ「UltraScale+」は今年Q4から出荷開始の予定で、「UltraScale+」対応の開発環境は既に一部の顧客に提供が開始されている。

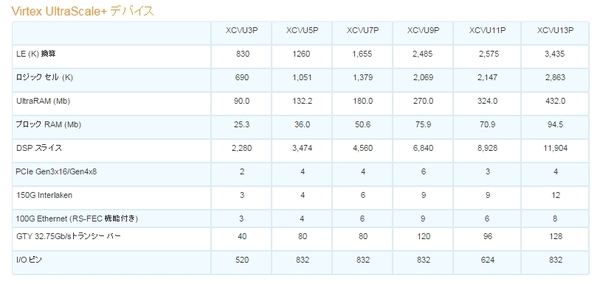

Virtexシリーズのデバイス構成は以下の通りで最上位品はUltraRAM 432Mb、ブロックRAM 94.5Mb、DSPスライス×11,904、150G Interlaken×12、32.75Gb/s トランシーバー×128と驚異的な仕様となっている。

= EDA EXPRESS 菰田 浩 =

(2015.02.24

)