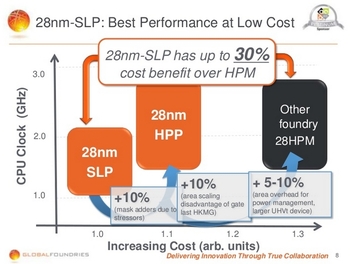

GLOBALFOUNDRIESとCadenceが28nm-SLPプロセスでARM Cortex-A17ベース・チップを製造

2014年12月18日、GlobalfoundriesとCadenceは、両社の協業によるARM Cortex-A17ベース・テスト・チップの成功事例を発表した。

発表によると両社は今回GlobalfoundriesのHigh-k Metal Gate 28nm Super Low Powerプロセスを使用してARM Cortex-A17ベースのクアッド・コア・テスト・チップを製造。同チップはCadenceのEDAツールのみでテープアウトされ、CadenceのSTA「Tempus」の予測通りとなる標準動作条件で2.0GHzの性能を達成した。

両社はこの成功を受けて最新のARM Cortex-A17 processor RTL、ARM POP IPを用いて2つ目のテスト・チップを製造。その結果、最大周波数2.0GHzのサインオフ目標を達成しつつ最初のテストチップよりもシングル・コアのチップ面積を23%縮小することに成功した。

※画像はGLOBALFOUNDRIESの公開データ

テスト・チップの設計に使用されたのは、下記Cadenceツールで2個目のテスト・チップ設計では、これらツールに加えパワー・インテグリティ解析ツール「Voltus」とローパワー設計考慮の等価性検証ツール「Encounter Conformal Low Power」も使用されたという。

-Encounter® Digital Implementation System

-Encounter RTL Compiler

-Quantus™ QRC Extraction Solution

-Tempus Timing Signoff Solution

-Encounter Conformal® Equivalence Checker

-Physical Verification System

-Litho Physical Analyzer

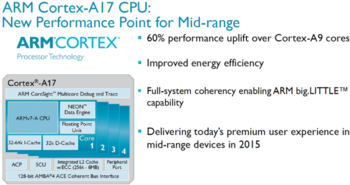

ARMの「Cortex-A17」は今年発表されたばかりのミッドレンジ向けCPUで「Cortex-A9」の置き換えソリューションとされている。未だ市場には「Cortex-A17」を搭載した製品は登場しておらず、公にアナウンスされたテスト・チップの実装例は恐らく今回が業界初。Cadenceはここ数年、ARMのリリースする新CPUコアをいち早く各半導体ファンドリの先端プロセスで実現する事に注力しており、TSMC 20/16nm、Samsung14nm、IBM14nmなど様々なプロセスにおいて先行する形でテスト・チップのテープアウト実績を残している。

※画像はARMの公開データ

= EDA EXPRESS 菰田 浩 =

(2014.12.25

)