Atrenta Technology Forumで聞いたAtrenta製品の最新アップデート

2014年9月12日、新横浜のホテルでAtrentaのプライベート・セミナー「Atrenta Technology Forum 2014」が開催された。

同セミナーではAtrenta製品のユーザーとして、京セラドキュメントソリューションズ、富士通九州ネットワークテクノロジ、パナソニックデバイスシステムテクノ、スパンション・イノベイツの4社が事例講演を行った。

ここでは各社の事例と共に発表されたAtrenta製品の最新アップデートについてレポートする。

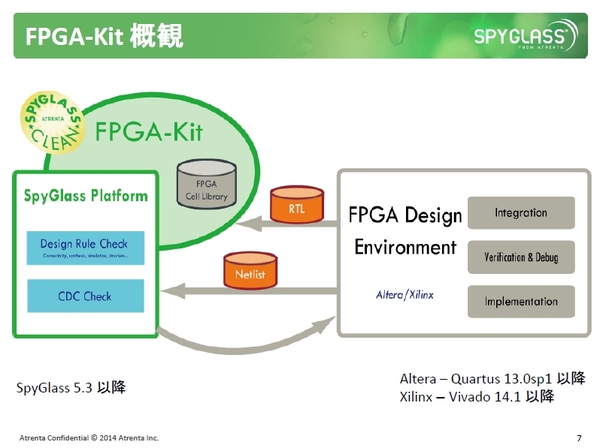

Atrenta製品として今回のセミナーでまず最初に紹介されたのは、新製品「SpyGlass FPGA-Kit」である。同製品は高度化するFPGA設計のニーズに応えるRTLの品質チェックのためのツールで、その実体はSpyGlassプラットフォームでFPGAデザインを検証するためのスクリプトウェアとAlteraおよびXilinxのセル・ライブラリとなる。

「SpyGlass FPGA-Kit」はFPGAデザイン(RTL)のルールチェックとCDCチェックに利用できるが、特徴的なのはAtrentaの強みの一つであるCDCチェック機能で、同梱されるFPGAライブラリにより簡単な設定でFPGAデザインのCDC検証環境をセットアップする事が可能。FPGAライブラリを含むサブブロック毎に同期化回路構造をチェックできる。また、CDCチェック機能としては、デザインの深い階層のリコンバージェンス・チェック、非同期リセットなどリセット構造のチェックも可能だ。

RTLシミュレーションだけでは実機動作が不安な複雑なFPGAデザインに対して、「SpyGlass FPGA-Kit」は一つの有効なソリューションと言えよう。

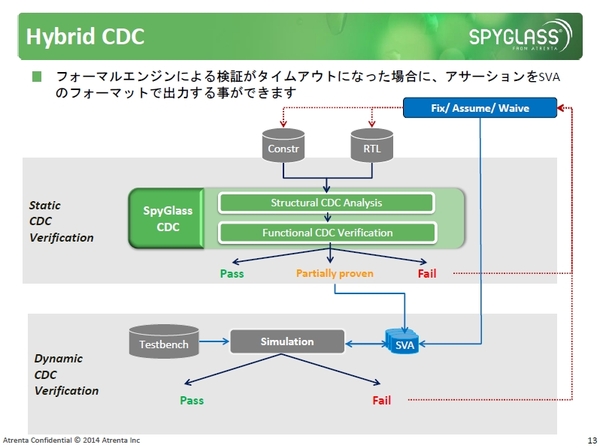

続いて「SpyGlass Platform」について。「SpyGlass Platform」のベース機能であるLintについては新たにSystemVerilog用のルールが追加されたほか、既存のSTARC準拠ルールの幾つかがSystemVerilogに対応した。また、デザイン中の同期FIFOを認識し、オーバーフロー/アンダーフローをチェックできる新たなルールも追加された。更にフォーマル検証のタイムアウト対策としてSVAを出力する機能も用意された。

CDC機能に関しては、同一ソースレジスタからの信号の同期化後の合流を検出する新ルールやLint同様にフォーマル検証のタイムアウト時にSVAを出力する機能が追加されたほか、擬似エラーのフィルタリング機能が改善された。

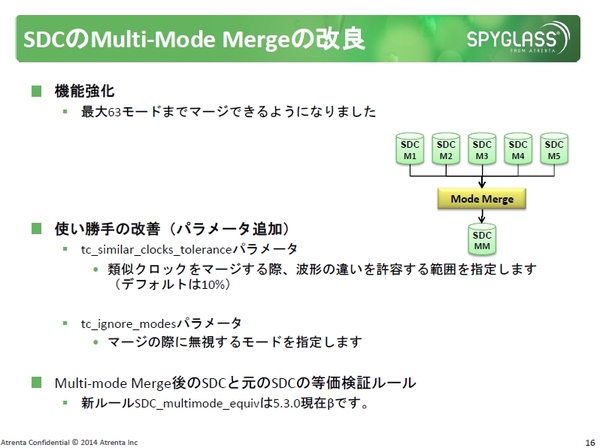

SDC機能に関しては、幾つかの新ルールに加え複数SDCモードのマージ機能が強化された。これまでは2モードしかマージ出来なかったが、新バージョンβ版では最大63モードまでマージ可能となった。

またマルチサイクルパスやフォルスパスをチェックする「SpyGlass TXV」のパフォーマンスが強化され、同一時間内により多くの制約を検証できるようになった。「SpyGlass TXV」は非常に好評でこの1年間だけで既に多数の国内企業が導入しているという。

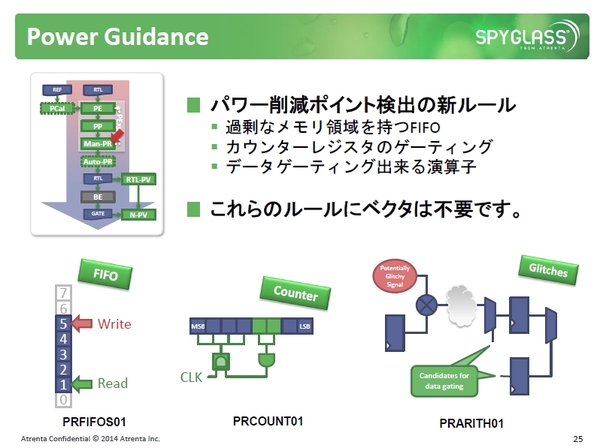

パワー解析を行う「SpyGlass Power」に関しては、パワー・リダクションのための新ルールが追加され、パワー削減のポイントを検出できるようになった。

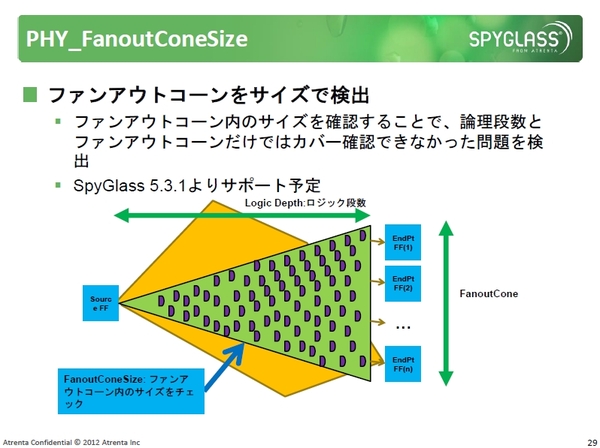

RTLでフィジカル解析を行う「SpyGlass Physical Base」に関しては、配線の混雑性を解析する機能が強化されたほか、ファウンアウト・コーンをサイズで検出する新機能が追加された。(次期バージョンからサポート予定)

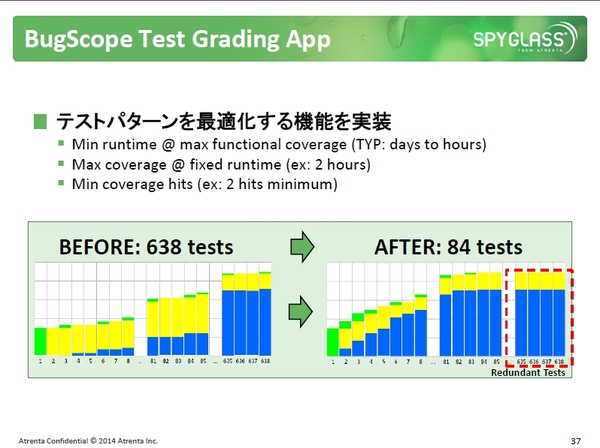

その他、プロパティ自動生成ツール「BugScope」では、テストパターンを最適化する機能が実装され、より機能検証の効率化が図れるようになった。

他にも各ツールの細部に渡り様々なアップデートが報告されていたが、大きなトピックスとしては上記の通り。

= EDA EXPRESS 菰田 浩 =

(2014.10.02

)