富士ゼロックス、Calyptoの高位合成ツールCatapultでアルゴリズムとRTLの協調設計を実現

2014年8月29日、高位合成ツールをはじめフォーマル検証ツール、ローパワー設計ツールを手掛けるCalypto Design Systemsは、新横浜のホテルでプライベート・セミナー「Calypto Users Forum 2014」を開催。セミナー会場には推定100名近くの来場者が集まり、例年以上も盛り上がりを見せていた。

ここでは同セミナーで発表された、富士ゼロックスの設計事例について紹介する。

講演タイトル:

「画像処理アルゴリズムのハードウェア化設計へのCatapultoの適用事例」

講演者:

富士ゼロックス株式会社 コントローラ開発本部 コントローラプラットフォーム第五開発部 三角 晃

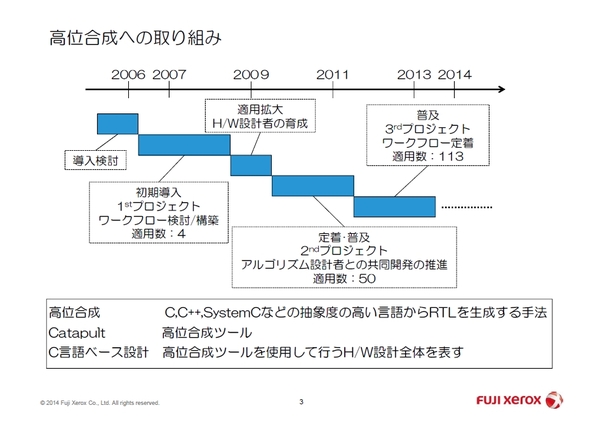

講演者の三角氏によると、富士ゼロックスでは2007年からCalyptoの高位合成ツール「Catapult」(※当時はMentor Graphics社が販売)を導入し複写機向けのコントローラ開発に適用。時間をかけて社内への普及を進め、過去約7年間で150以上の回路モジュールに適用(その大半は過去3年以内)。最近は画像処理部は全て「Catapult」で設計するプロジェクトもあるという話。

※画像は富士ゼロックス提供のデータ

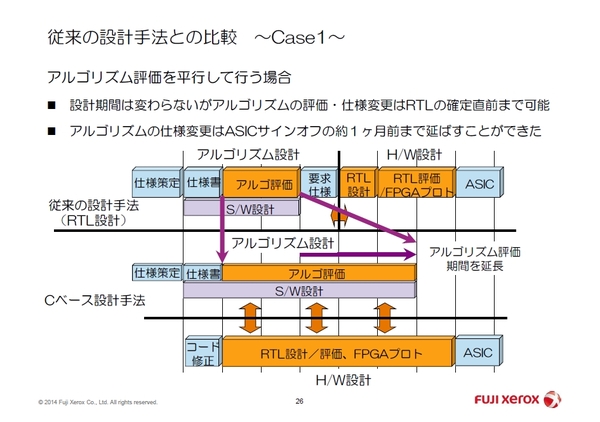

同社における高位合成へのモチベーションは明確で、開発の効率化とアルゴリズム設計側からの要求の2つ。後者は何かと言うと、アルゴリズムの評価期間を出来るだけ長く取りたいという要求だ。実際の導入にあたっては「Catapult」の使用による回路要求仕様の最適化や設計資産のCモデル化(プロジェクト間でRTLではなくCモデルを再利用)などにも期待した。

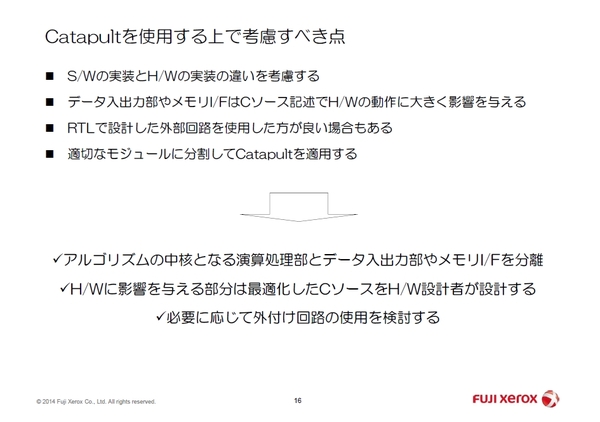

既に「Catapult」を導入しコントローラ開発で定着させている同社だが、三角氏によると「Catapult」の普及に向けてはそれなりに苦労したという事で、その経験に基づいた「Catapult」利用上の注意点(考慮すべき点)として、インタフェース部などハードに影響する部分はハード設計者がCソースをしっかり最適化する。もしくはRTL回路の外付けを検討すること。そして合成は関数単位など適切なモジュールに分割して実施すること。などを挙げた。

※画像は富士ゼロックス提供のデータ

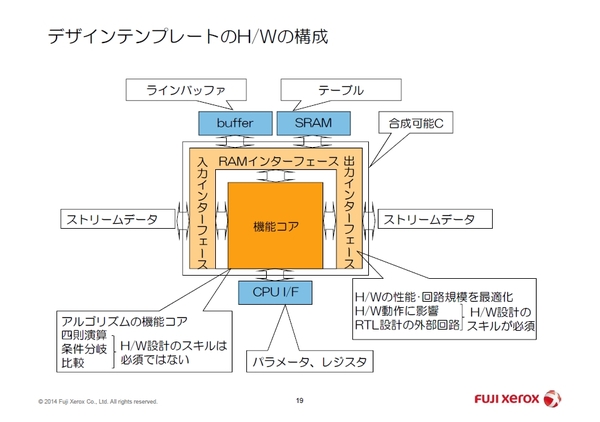

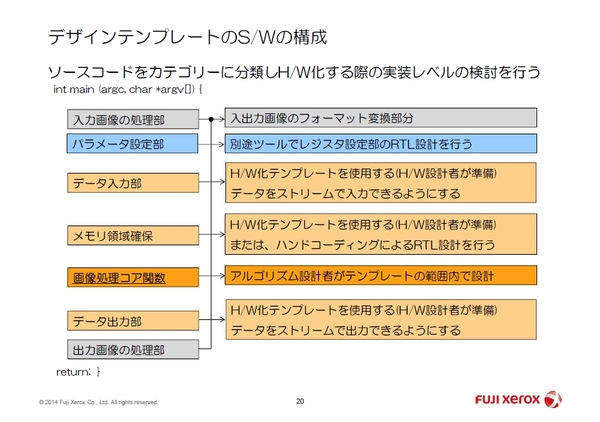

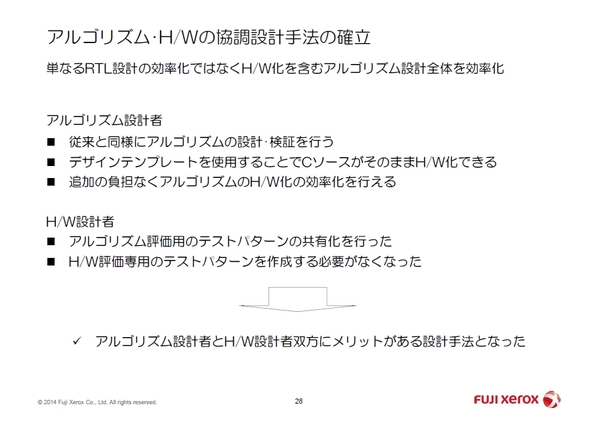

更に三角氏は「Catapult」の運用ノウハウとして「デザインテンプレートの作成」について紹介。三角氏によると同社では高位合成の対象とする画像処理部を機能別に4つのタイプに分類し、各タイプ毎にデザインテンプレートを用意。それを用いることで設計の効率化と同時にアルゴリズム設計者とハードウェア設計者の作業分担/ワークフローを明確化しており、合わせてCアルゴリズムの修正を行う際のルールを設定する事でハード化への影響を抑えているという話だった。

テンプレートを用いた作業分担としては、アルゴリズム設計者はアルゴリズムの機能コアの設計にフォーカスし、それ以外はハード設計者が担当。メモリ・インタフェース部に関してはCコードで実装せずにハード設計者がRTLをコーディングというのがポイントのようだった。

※画像は富士ゼロックス提供のデータ

このようにして実際に「Catapult」を適用した結果、従来シーケンシャルに進めていたアルゴリズム設計とRTL設計が同時並行的に進める事が可能となり、あるケースではASICサインオフの約1ヶ月前までアルゴリズムの仕様変更が可能に。またアルゴリズムが確定しているケースでもRTL設計期間の短縮によりASIC設計を前倒しでき、全体的な設計期間の短縮を実現できたという事。三角氏はこれら成果と合わせ幾つかの具体的なメリットを示した上で、「Catapult」によりアルゴリズム設計者とハードウェア設計者双方にメリットがある協調設計手法を確立出来たと語った。

※画像は富士ゼロックス提供のデータ

尚、三角氏によると「Catapult」は既にアルゴリズム設計者にとっても無くてはならないツールとなっており、「Catapult」を利用する事によってハード化による回路規模やコストを意識するなど、アルゴリズム設計者の意識が良い意味で変化しているという。

= EDA EXPRESS 菰田 浩 =

(2014.09.11

)