NEWS

MicrochipがFPGA開発フローに高位合成ツールを用意、C++からの実装を可能に

2021年9月2日、Microchipは提供するFPGA「PolarFire FPGA」向けの設計ツール「SmartHLS」のリリースを発表した。

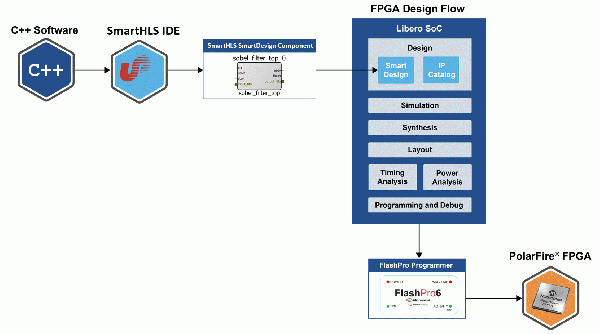

「SmartHLS」はC++コードからRTLを自動生成する高位合成ツールで、「PolarFire FPGA」およびRISC-Vプロセッサを搭載する「PolarFire SoC」の開発に利用できる。

Microchipによると「SmartHLS」はオープンソースのEclipseベースのツールで、複数のハードウェア命令を同時に実行して複雑なハードウェア並列処理を単純化するマルチスレッドAPIで他のHLSツールよりも迅速な開発が可能。Microchipの提供する「VectorBlox™ニューラル ネットワーク ソフトウェア開発キット」を使うと、FPGA ベースのハードウェア・アクセラレータを効率的に開発できるという。

「SmartHLS」は「PolarFire FPGA」向けの設計スイート「Libero SoC」の一部であるが、独立したツールとしても利用可能。Microchipのウェブサイトで入手できる。

|ページの先頭へ|