NEWS

Xilinxが機械学習最適化機能でQoRを向上できるFPGA設計環境「Vivado ML Editon」をリリース

2021年6月23日、Xilinxは同社の提供するFPGA設計環境「Vivado」に機械学習による最適化機能を実装した「Vivado® ML Edition」のリリースを発表した。

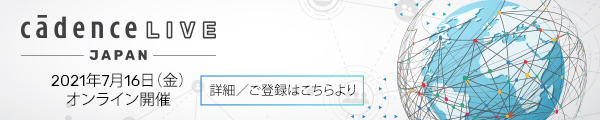

Xilinxによると「Vivado ML Edition」には、「Intelligent Design Runs (IDR)」と呼ぶ機械学習ベースの自動タイミング収束機能が用意されており、機械学習を用いて配線における混雑予測や遅延予測を行い、最適な戦略を導き出しタイミングを収束させることが可能。これによりタイミング収束のためのイタレーション作業が不要となり、現行の「Vivado HLx Edition」と比較してQoR(結果の品質)を最大50%、平均10%向上できる。同機能はプッシュボタン式に実行可能で複雑なデザインにおいて特に効果を発揮するという。

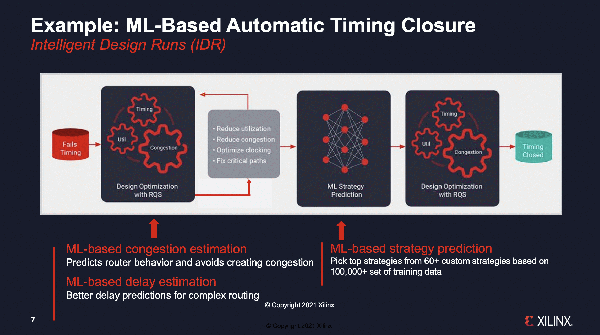

また、抽象化シェルというコンセプトの導入により、システム内の複数のモジュールを定義し、インクリメンタルかつ並列にコンパイル可能に。これにより、従来のフルシステムのコンパイルと比較してコンパイル時間を平均5分の1、最大17分の1に短縮できる。抽象化シェルはモジュールを除くデザインの詳細を隠蔽するため、IPの保護にも役立つ。

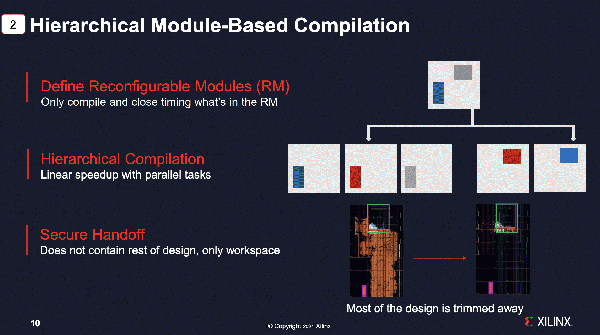

更に「Block Design Containers」と呼ぶIPのインテグレーター機能により、モジュラーベースのグラフィカルなデザインが可能で、デザインの再利用やチームによる協調設計が容易になるほか、「Dynamic Function eXchange」と呼ぶ機能を使うことで、OTAで数ミリ秒でデザイン・モジュールを読み込み、実行する機能を動的に切り替えるということができるという。

「Vivado ML Edition」は、無償の「Standard Edition」と有償の「Enterprise Edition」があり、無償版はサポートするデバイスが限定される。有償版はノードロック・ライセンスが2,995ドル、フローティング・ライセンスが3,595ドルとなっている。

※画像は全てXilinx社Web上のデータ

|ページの先頭へ|