NEWS

Cadenceが1024ビットおよび128ビットSIMDの新型Tensilica DSPコア2品種を発表

2021年4月22日、Cadenceは、エンベデッドビジョンおよびAI向けDSPの新製品2品種を発表した。

今回Cadenceが発表したのは、Tensilica Vision DSP製品ファミリーとしてラインナップされる「Tensilica Vision Q8 DSP」および「Tensilica Vision P1 DSP」の2品種。

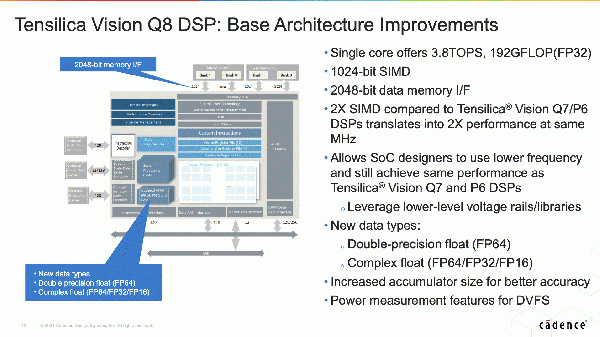

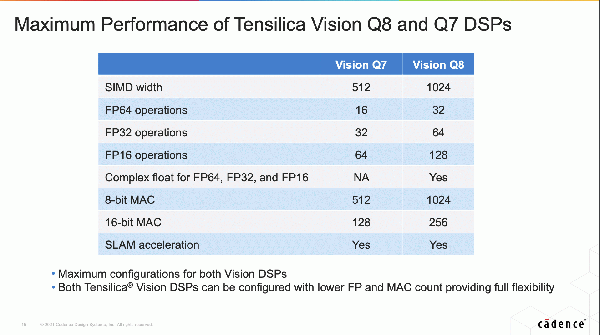

「Tensilica Vision Q8 DSP」は、既存の「Tensilica Vision Q7 DSP(512ビットSIMD)」の倍の1024ビットSIMDアーキテクチャの第7世代のハイエンドDSPコアで、Tensilica Vision DSP製品ファミリーのフラッグシップ製品という位置付け。

「Vision Q8」は、「Vision Q7」の2倍にあたる最大3.8TOPSのパフォーマンスと2倍のメモリー帯域幅を実現しており、システムデザインの簡素化によりシングルコアでの消費電力を最大20%低減する一方、MAC数が追加されたことなどによりAIパフォーマンスは最大4倍に引き上げられた。

「Tensilica Vision Q8 DSP」は1つのチップに最大4コア構成で利用可能で、パフォーマンスを要求するハイエンドモバイル、マルチカメラ車載アプリケーションなどを主なターゲットとする。

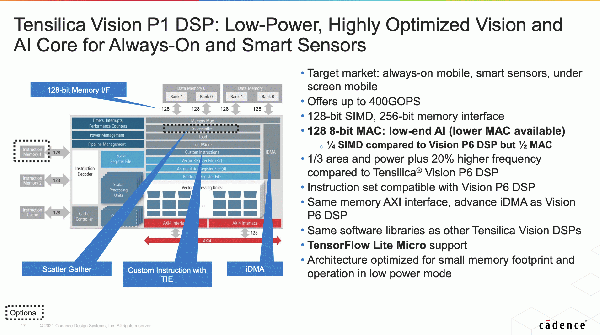

ハイパフォーマンスDSPコアとして開発された「Tensilica Vision Q8 DSP」に対し、「Tensilica Vision P1 DSP」は128ビットSIMDアーキテクチャで電力効率重視の小型ローパワーDSPコアという位置付けで、スマートフォンのAI処理などで実績のある既存の「Vision P6 DSP」と比較すると、面積と消費電力は3分の1、パフォーマンスは約半分程度となっており、スマートセンサー、AR/VRグラス、IoT/スマートホーム機器など、AI処理を行う常時接続アプリケーションを主なターゲットとしている。

※画像はCadence提供のデータ

新製品の「Vision Q8 DSP」および「Vision P1 DSP」はいずれも既存のDSP同様、N-waySIMDプログラミングモデルを採用しており、異なるSIMD幅を持つ既存のTensilica Vision DSPからソフトウェアを容易に移行可能。すなわちコアの選択により、同じソフトウェアでパフォーマンスをスケーラブルに変更できる。

また、いずれのDSPコアもニューラルネットワーク向けの「Xtensa ® Neural Network Compiler (XNNC) 」、「Android Neural Networks API (ANN API) 」、1700種以上のOpenCVベースのVision Library関数、OpenCL、Halideコンパイラーに対応。さらに機能安全規格 ISO26262、ASIL Bランダムハードウェア故障およびASIL Dシステマティック故障の認証を取得しており、車載向けアプリケーションにも利用できる。

「Tensilica Vision Q8 DSP」は既に出荷が開始されており、「Tensilica Vision P1 DSP」は2021年のQ2に一般リリースの予定。

CadenceのTensilicaシリーズ製品は、DSPとしては世界トップシェアを誇り300以上の顧客を持ち累計出荷数は70億以上。CadenceはプロセッサIPのライセンス売上としてArmに次ぐ世界2位の座をキープしている。

|ページの先頭へ|