NEWS

TSMC 5nmプロセスのデザインサービスを開始した台湾Alchip、PFNのスパコン省電力世界一獲得にも貢献

2020年8月13日、台湾のファブレスASICベンダーのアルチップ・テクノロジーズは、TSMC 5nmプロセスをターゲットとしたASIC設計のデザイン・サービスを開始したことを発表した。

Alchipによると、最先端のTSMC 5nmプロセス向けのデザインサービスの開始は同社が業界初。最初のテストチップのテープアウトを今年12月に予定しているという。

Alchipのデザインサービスは、一般的なデザインの請け負いに加え、チップのパッケージからテストまでトータル的にサポートしており、TSMCとのパートナーシップや独自の設計技術、IPソリューションが大きな強み。それらの総合力によって顧客のニーズに応じた高品質な最先端プロセス製品を短TATで実現している。

Alchipは5nmデザインにおいても、DDR5、GDDR6、HBM2E、HBM3、D2D、PCIe5、Tier 1プロバイダーの112G serdes IPなど、「クラス最高の」高性能コンピューティングIPポートフォリオを利用するとしており、合わせて同社の高度なパッケージング機能が5nmチップの生産の強力な武器になると強調している。

Alchipのこれまでの実績を振り返ると、TSMC先端プロセスへの対応力や高性能チップの開発実績が目立つが、先頃発表されたプレスリリースによると、同社はスパコン省電力ランキング「Green500」で世界1位を獲得した、Preferred Networksのスパコン「MN-3」に搭載されるディープラーニング・プロセッサ「MN-Core」の設計に深く関わっていたという話。

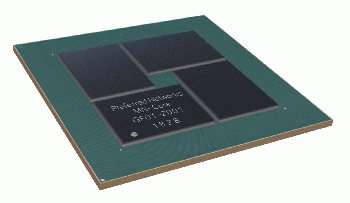

発表によるとAlchipは、4ダイ構成の巨大なプロセッサ「MN-Core」の設計に独自のクロック設計技術を用いる事で、バラつき回避と電力削減に大きく貢献。4つのダイ間のインターフェース接続には同社独自のD2D接続技術を用い、その巨大なチップのパッケージやテストにおいても独自のノウハウを駆使したということだ。(※画像はMN-Core, PFN社web上のデータ)

日本にもオフィスを構え複数の日本企業を顧客に持つAlchipは、古くはTSMC 90nmプロセスが最先端だった時代に、東京大学を中心に進められたスーパーコンピュータ開発プロジェクト「GRAPE-DR」に参画し、同スパコン搭載チップの物理設計とチップ製造を成功させている。

※関連ニュース:

|ページの先頭へ|