NEWS

ソシオネクストと東工大が世界最小のクロック回路を5nmCMOSプロセスでデジタル回路として実現

2020年2月10日、ソシオネクストと東京工業大学 岡田健一教授らの研究グループは、5nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功したことを発表した。

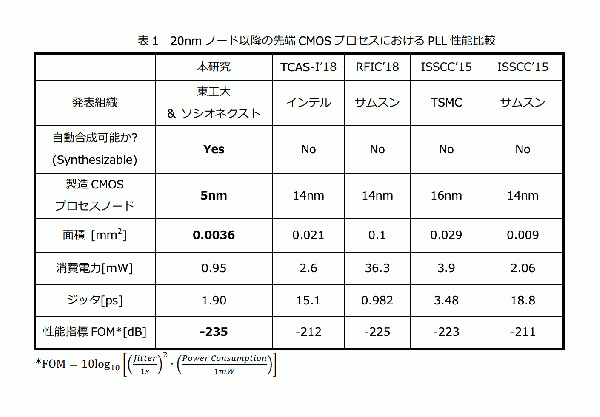

発表によると今回開発されたクロック回路はデジタル回路として構成されるもので、通常のデジタル回路と同様にデジタル回路の設計ツールで自動配置配線が可能。実際に5nm FinFET CMOSプロセスで作られた回路は世界最小の0.0036mm2 という回路面積で、優れたジッタ特性と電力性能を実現。(※下記画像参照)また、同クロック回路は細かい周波数調整が可能な分数分周型PLLで構成されており、スペクトル拡散クロックの生成により低電磁妨害特性を実現しているという。

※画像はプレスリリースのデータ

従来のPLLではアナログ回路構成で実現されていたデジタル制御発振器(DCO)と時間差デジタル変換器(TDC)を、デジタル回路構成によって実現できたことが今回のクロック回路開発の成果で、デジタル時間変換器(DTC)とTDCを組み合わせデジタル補正を用いることでそれを実現した。

PLL全体をデジタル回路として実現できるということは、プロセス技術の微細化に合わせて回路面積を縮小でき、低消費電力化も可能となるだけでなく設計も容易になる。今回の成果をうけてソシオネクストは、クロック回路のデジタル化により将来のSoCの全自動設計への道が拓かれたとしている。

なお、今回の研究は、株式会社テラピクセル・テクノロジーズの協力により実現したとのこと。

|ページの先頭へ|