NEWS

単なるIPベンダではなくチップ開発のゲームチェンジャーを目指すSiFive

2019年6月11日、オープンソースの命令セット・アーキテクチャ「RISC-V」ベースのプロセッサ・コアを手掛ける米SiFive社は、日本で初となるプライベートセミナー「SiFive Tech Symposium 2019 in Japan」を開催し100名近い参加者を集めた。

ここではセミナーの様子をダイジェストでお伝えする。

同セミナーのアジェンダは以下のSiFive社Webページを参照。朝から夕方までほぼ20分刻みで計16のセッションが行われた。

まずセミナーの冒頭に挨拶に立ったのはSiFive VP of Sales APACのHuzefa Cutlerywala氏。同氏はSiFiveに買収されたOpenSilicon社の元メンバー。

最初のセッションはSHコンサルティング社の河崎俊平氏によるもので、RISC-V FoundationおよびSiFive社のファウンダーであるKrste Asanovic氏の代理という形でRISC-Vの概要について説明した。

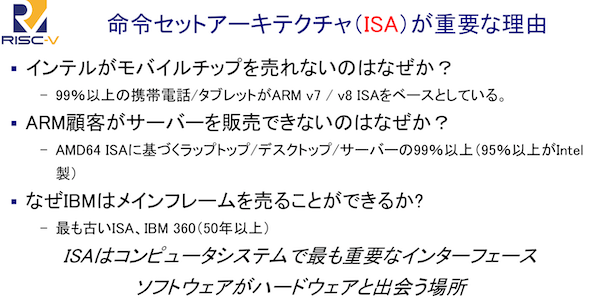

メッセージとしてはRISC-Vの存在意義とRISC-V Foundationの活動状況の大きく二つで、コンピュータ・システムにおけるISAの重要性を説きつつ、そのあるべき姿として企業の手の内にとどまらないオープンソースである事が望ましいと主張。RISC-Vはそれを実現する運用性の高い優れたISAであり、RISC-Vによって生み出される新たなビジネスモデルがRISC-Vへの移行を加速しているとした。

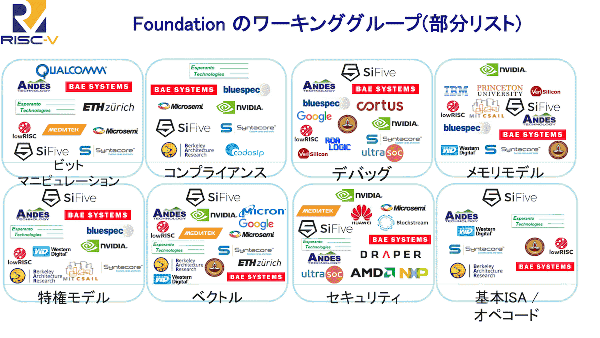

RISC-V Foundationの近況としては、メンバー企業が世界27ヶ国140社(学術機関などの団体も含めると230以上)に増え、最近元OpenPower Foundation会長のCalista Redmond氏が新たにCEOに就任した。組織内の8つのワーキング・グループも活発に活動しており、Linux Foundationとも積極的に連携を図っているとの事。ISA仕様については、非特権モードの基本および初期拡張機能、特権モード仕様が正式に承認され、現在Instruction set manualが公開されている。また、今年1月にRISC-V史上最も大きな拡張としてベクトル仕様0.7ドラフト版がリリースされたという。なお、河崎氏によると今年もRISC-V Day Tokyo 2019が9月30日に開催される予定だという。

2つ行われた基調講演の一つは「Leading Semiconductor Design Revolution」というタイトルでSiFiveのHuzefa Cutlerywala氏が講演した。内容はSiFiveのチップ設計ソリューションの概要。

冒頭に紹介されたSiFiveの実績データによると、SiFiveの顧客はワールドワイドで100社以上でテープアウト実績は既に300以上という話。

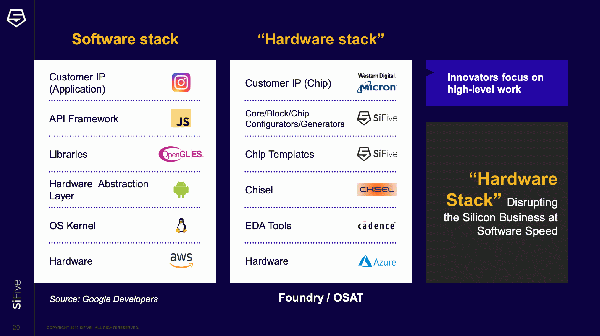

SiFiveのチップ設計ソリューションのベースとなっているのは、ソフトウェア開発のように「ハードウェア・スタック」を活用する事でチップ設計を容易化および高速化するという考え方で、自社のソリューションを「ハードウェア・スタック」の一つのレイヤーに位置付けている。

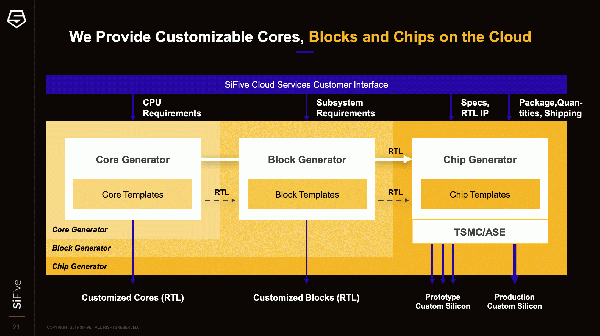

SiFiveはチップ設計のためのテンプレートを3種類用意する。ユーザーはクラウド環境場でこれらテンプレートを用いてチップ設計が可能。Chipテンプレートとしては、AI Accelarator、Smart NIC、IoT Hubなどが用意されている。

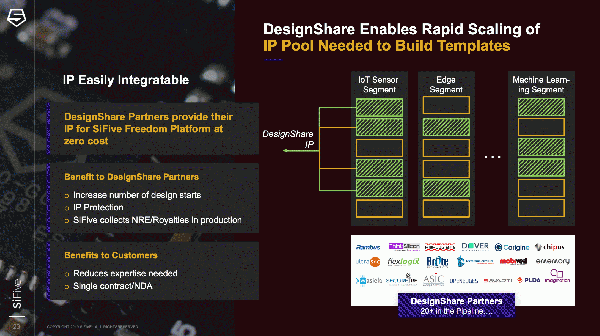

テンプレートを用いたチップ設計は、SiFiveが展開するエコシステム「DesignShare」に加盟する20社以上のIPベンダのIPを利用できる。IP利用にあたって発生するロイヤリティはチップを製造する場合のみ。プロトタイピングの段階ではIPの費用は発生しない。IP利用に関する契約なども不要で全てSiFiveが窓口となりワンストップ対応してくれる。

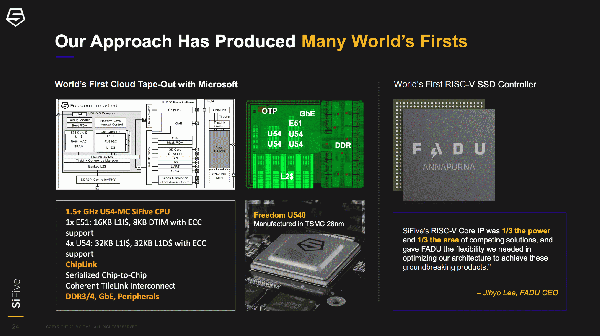

SiFiveのクラウドベースのテンプレートで最初にデザインをテープアウトしたのはMicrosoftで開発期間は僅か4週間だったという。Huzefa Cutlerywala氏はSiFiveのソリューションを利用すれば、通常18ヶ月を要するチップ設計を3-6ヶ月で完了できると説明した。

今回の「SiFive Tech Symposium」には、SiFiveのパートナーとしてQuickLogic、DTS Insight、IAR Systems、Rambusの4社が出展。それぞれ自社のRISC-V関連ソリューションについて講演した。

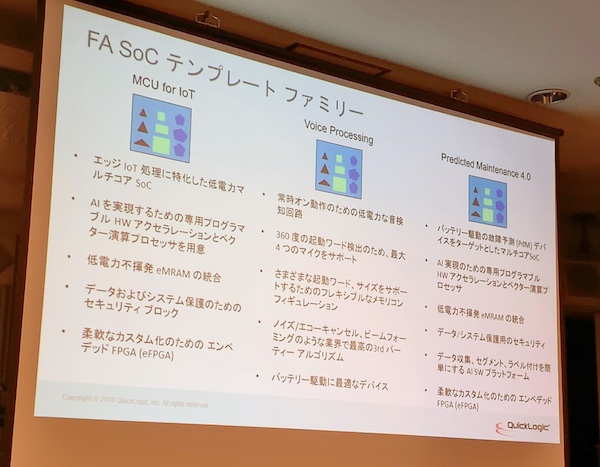

QuickLogicはSiFiveのエコシステム「Design Share」のメンバーで、SiFiveとのパートナーシップによりSiFiveのテンプレートを拡張した独自のSoCテンプレート「Freedom Aware ファミリ」を提供している。MCU for IoT、Voice Processing、Predicted Maintenance 4.0(故障予測)と3種類用意されるSoCテンプレートを利用する事で、各アプリケーション向けのローパワーSoCを非常に短期間(僅か数ヶ月)で開発可能となる。またQuickLogicは「Freedom Aware ファミリ」と組み合わせて利用できるエッジAIソフトウェア・ツールキット「SensiML」も提供。これを活用すればAI知識を必要とせず数日/数週間でインテリジェントなIoTセンシング・デバイスが開発できるという。

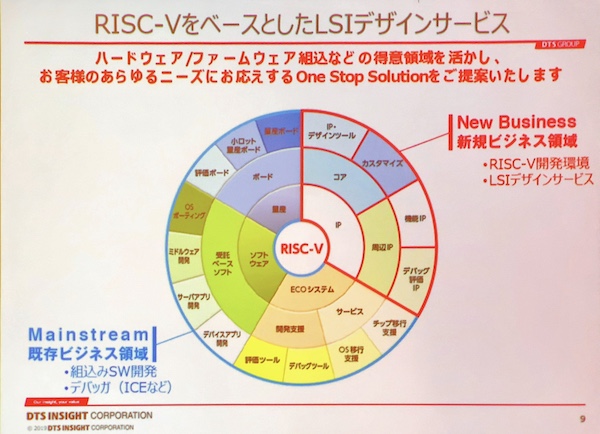

DTS Insightは、新規ビジネスとしてRISC-VをベースとしたLSIデザインサービスを立ち上げる。合わせてRISC-Vベースプロセッサの開発環境も提供していくという話だ。

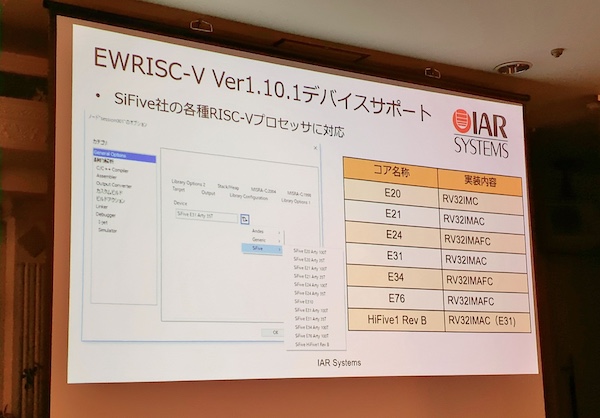

IAR Systemsは、RISC-V向けの統合開発環境「IAR Embedded Workbench for RISC-V」について紹介。基本的に同社の旗艦製品「IAR Embedded Workbench」と同じ操作性で利用可能で、現在はRV32 32ビットRISC-Vコアおよび拡張命令をサポート。今後、64ビットおよびRV32Eをサポートする予定。「IAR Embedded Workbench for RISC-V」には静的コード解析機能のライセンスが付属。機能安全認証にも対応済みだという。

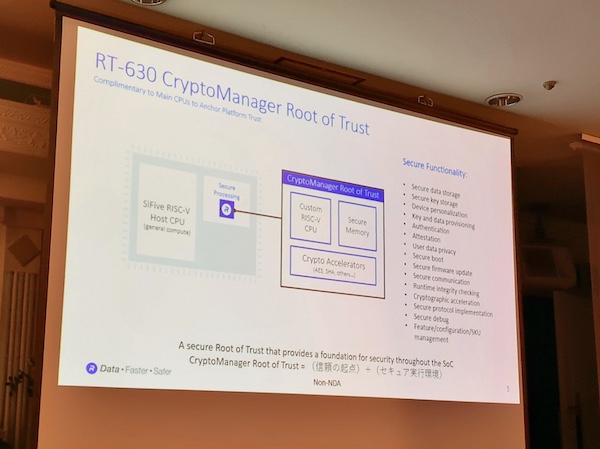

Rambusは、提供しているSoC向けのセキュア・コア「CryptoManager Root of Trust」について紹介。同セキュア・コアはRISC-VベースのカスタムCPUを用いて構築されたコアで、RISC-Vを用いる事でCPUの内部に手を入れた高度なセキュリティ対策が可能になったという。顧客にはセキュア・コアと合わせてセキュア・アプリケーションのリファレンス・コードも提供されるという話。なお、RambusはSiFiveのエコシステム「Design Share」のメンバーで、セキュア・コア以外にも、サイドチャネル攻撃対策ソリューションやチップへの暗号鍵の書き込みや鍵の管理などのセキュリティ関連ソリューションを提供しているという話だ。

その他にSiFiveからは、SoC向けのIPソリューション、コアのラインナップとその詳細、開発およびデバッグ環境、SSDコントローラ向けソリューション、組込み業界でのビジネス概況、といった話が紹介された。

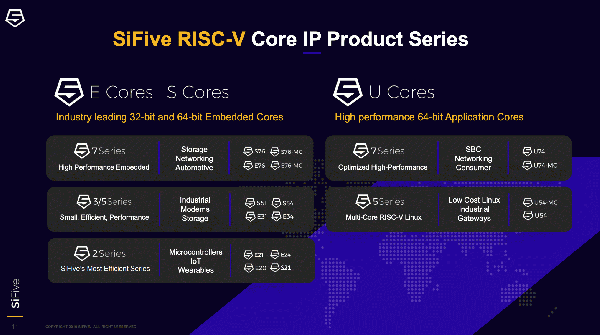

SiFiveの提供するRISC-Vベースのコアは現在16種類。2シリーズは小型ローパワーのコア、3/5シリーズは最も採用数が多いミッドレンジのコア、7シリーズはハイパフォーマンス・コア。Eコアは32ビット組込コア、Sコアは64ビット組込みコア、Uコアは64ビットのアプリケーション・プロセッサという位置付けとなる。

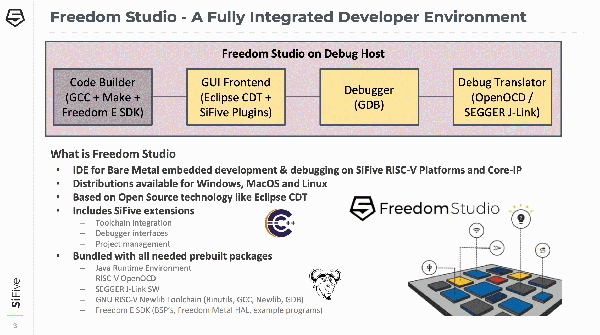

SIFiveの提供する開発環境「Freedom Studio」、SiFiveはその他にもFreedom Toolsと呼ぶオープンソースのツールおよびスクリプトや、各種開発キットやソフトウェア・コンポーネントをGithubで公開している。

SiFiveの顧客の成功事例としてよく語られるのがSSDコントローラへの適用事例。年間10億以上のコアをRISC-Vに置き換えたというWestern DigitalもSiFiveの顧客の一人。SiFiveは膨大なチップの出荷実績はその万全な設計・製造体制(エコシステム)を裏付けるものだとしている。

今回初めて日本で本格的なセミナーイベントを開催したSiFiveだが、その企業としての規模はワールドワイドに急激に拡大しており、既に世界に15の拠点を持ち、約1年前に数十名だった従業員数は現在400名以上に。今年は世界75の都市で計350以上のイベントを計画しているという話で、RISC-V普及の立役者としてその勢いは更に加速しているようだ。

|ページの先頭へ|