NEWS

Cadenceが数十億ゲートのデザインにも対応可能な新型のプロトタイピングシステム「Cadence Protium X1」を発表

2019年5月28日、Cadenceは、FPGAベース・プロトタイピング・システムの新製品「Cadence Protium X1」を発表した。

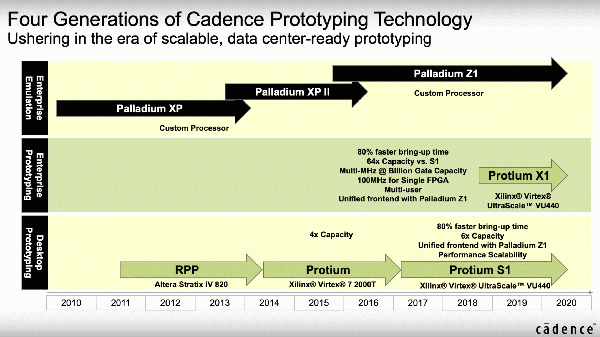

発表によると「Cadence Protium X1」は、FPGAベース・プロトタイピング・システムとして同社4世代目の製品で、既存の最上位製品「Protium S1」とは異なる新たなアーキテクチャーにより新規開発されたもの。ベースとなるFPGAは、「Protium S1」と同じXilinxの20nm FPGA「Virtex Ultra Scale VU440」を使用している。

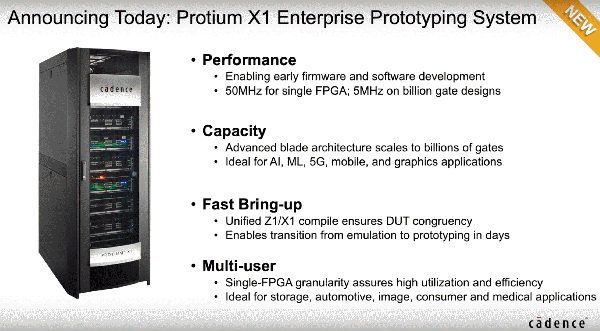

「Protium X1」はデータセンターへの設置を前提に最適化されたシステムで、FPGAボードを搭載したブレードを最大8台搭載できる筐体(ラック)が用意されている。ブレード1台当たりのデザイン容量は1億5000万ゲートで1ラック当たり12億ゲート。ラックは最大32台接続可能で最大1,536個のFPGAを利用できる。この豊富なFPGAリソースにより数十億ゲートの大規模デザインにも対応可能で、ブレード1台当たり最大6名のマルチユーザーで利用することも可能。また、新たなデザイン分割機能、インターコネクト技術などにより性能も大きく向上されており、「Protium X1」は数十億ゲートのデザインでも最大5MHz、シングルFPGAであれば100Mhzの実行速度を提供できるという。(「Protium S1」では4億ゲートを超えるデザインではパフォーマンスが低下していた)

※画像はCadence Youtube動画のキャプチャ画像

なお、「Protium X1」はエミュレーション・システム「Palladium Z1」と共通のフロントエンドを使用しており、従来製品同様、容易な適用、早期立ち上げを実現。Cadenceは、エミュレーションからプロトタイピングへ数日で移行できるとしている。機能面では、数千万クロックサイクル/数千の信号をリアルタイムにキャプチャーする「ハイパフォーマンス・データキャプチャー・カード」が新たに用意されたほか、再コンパイルすることなくすべての信号に動的アクセスが可能となる新機能「Prototyping Full Visibility」が追加されている。

「Protium X1」は既に出荷中で、NVIDIAがGPUのソフトウェア開発で「Protium X1」を使用したというプレスリリースが出ている。

|ページの先頭へ|