NEWS

Mentor Forum 2017 高位合成ツール業界No1を自負する「Catapult」の最新事例

2017年9月29日、メンター・グラフィックス・ジャパンは、品川本社でセミナー「Mentor Forum 2017」を開催。同社Calypto事業部の製品である「SLEC」、「PowerPro」、「Catapult」の最新情報を披露した。

ここでは同セミナーで紹介された高位合成ツール「Catapult」の最新事例についてレポートする。

「Catapult」の事例として最初に紹介されたのは同社の海外顧客による事例で、Google、Qualcomm、NVIDIA、STMicroelectronicsなどIT/半導体業界のビッグネームが並んだ。

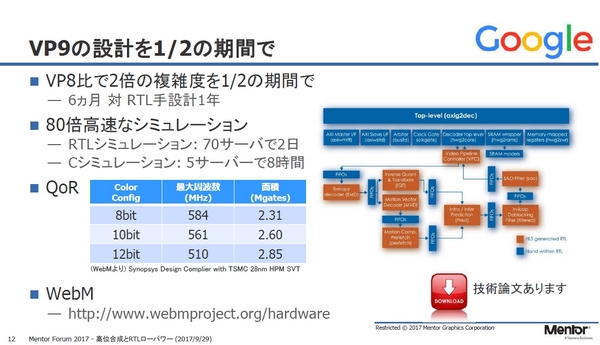

まずGoogle。同社は数年前から「Catapult」のユーザーで独自のビデオコーデック「VP9」のIP開発で「Catapult」を活用した実績を持つ。MentorのCalypto事業部、シニアAEマネージャーの山本氏によると、Googleは既に「VP9」の後継となるビデオコーデック「AV1」の開発においても「Catapult」を使用しているという。

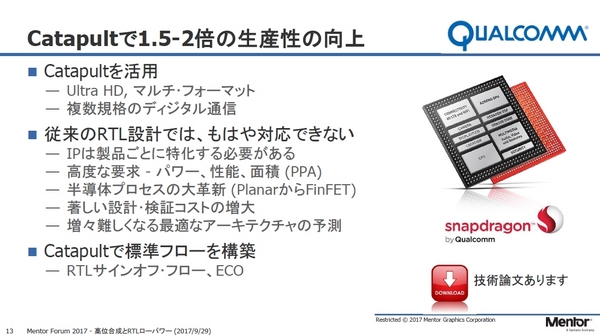

Qualcommは社内の標準設計フローに「Catapult」を組込んでおり、同社のSoC「Snapdragon」における画像処理、ベースバンド処理の回路設計に「Catapult」を活用している。従来手法ではもはや設計に対応できないとして「Catapult」の社内横展開を進めているという話。

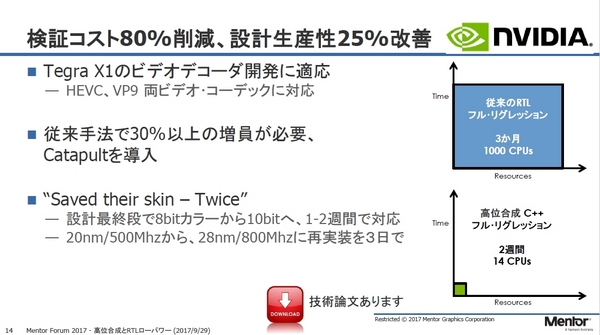

NVIDIAは急な仕様変更において2度に渡り「Catapult」に助けられ、その実績から一気に「Catapult」の活用に踏み込んだ。ここ最近は、自動運転用のSoC「Xavier」や車載向けの機械学習/画像認識テストチップの開発など、自動車分野の製品開発にも「Catapult」を使用しているとの事。

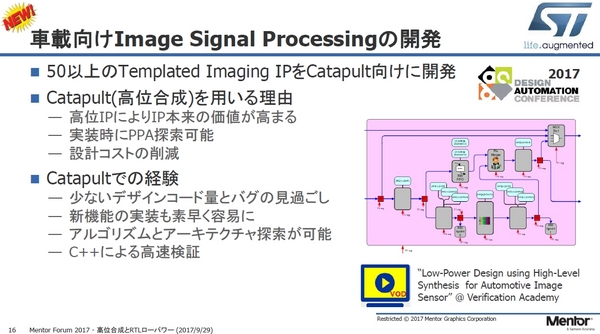

STMicroelectronicsは、H.265の開発で「Catapult」を使い開発期間をH.264の開発よりも1年短縮する事に成功した。今年のDACで発表した最新の事例は車載向けISPの開発で、C++で「Catapult」用のテンプレート(イメージングIP)を50以上作成し、それをベースにISPを開発することで効率的なトレードオフや設計コストの削減を実現したという。

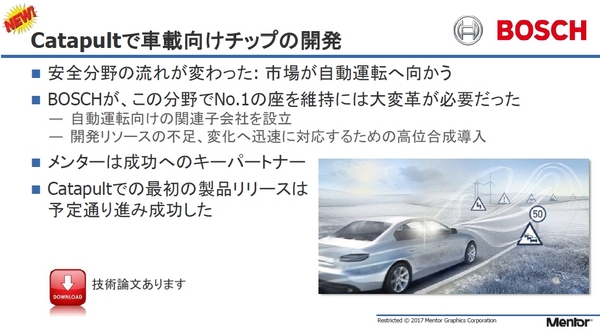

一番興味深かったのはBOSCHの事例。同社は自動運転向けの画像認識IPの開発に「Catapult」を利用。1年以内という短期開発を実現するために「Catapult」の導入を決断した。(※同事例の詳細は公開されている技術文献を参照)同デザインは、短期間だけでなくローパワーも求められていた為、BOSCHは「PowerPro」も活用し最終的に初めに合成したRTLよりも30%のパワー削減に成功した。DFTカバレッジ99%という車載ならではの厳しい制限も「Catapult」の機能を駆使してクリアし、1年とされていた開発を7ヶ月で完了する事ができた。

なお、Mentorの山本氏によると、ワールドワイドの高位合成ツールの市場シェアは2015年以降「Catapult」が首位。ユーザー数、売上ともに順調に伸びているという。

日本国内のユーザー事例として紹介されたのは、富士通九州ネットワークテクノロジーズ株式会社とコニカミノルタ株式会社の2社。それぞれ山下氏、河邉氏がユーザーとして事例を発表した。

※画像左:山下氏、画像右:河邉氏

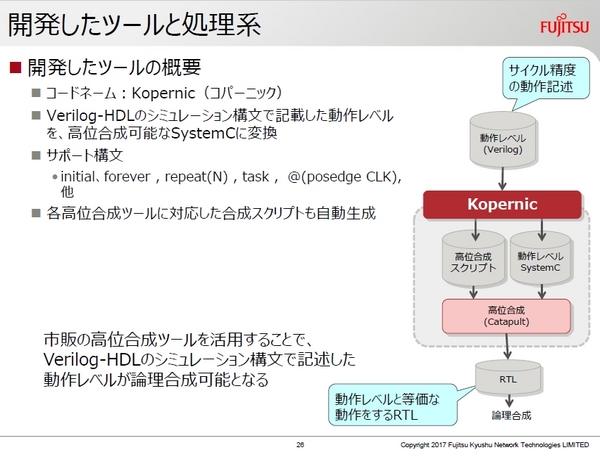

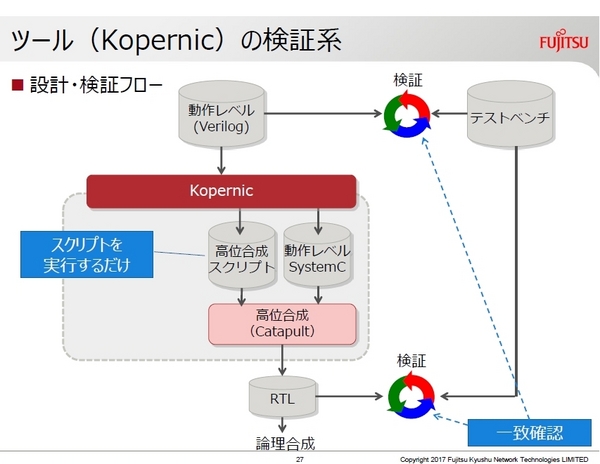

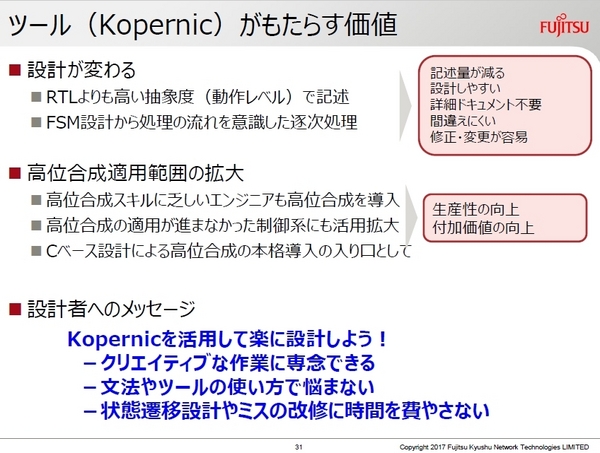

富士通九州ネットワークテクノロジーズの山下氏は2009年、2013年と「Catapult」の事例を発表している古くからの「Catapult」ユーザー。長年高位合成を活用している立場ならではの視点で、高位合成の適用領域を制御回路の設計にも拡大すべく、Verilog HDLのシミュレーション構文で記述した動作レベル記述を高位合成可能なSystemC記述に変換する独自ツール「Kopernic」を開発した。HDLのシミュレーション構文から高位合成を用いて制御回路を設計できれば開発効率を向上できると考えた為である。(※ツール「Kopernic」の処理系および検証フローは下記スライド参照。)

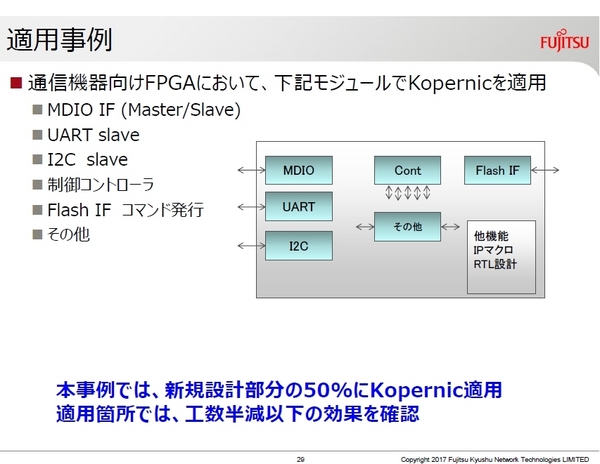

山下氏は「Kopernic」を適用しやすい回路として、コントローラ、プロトコル処理、シーケンス処理などを挙げ、実際に通信機器向けFPGAの複数モジュールの設計に「Kopernic」と「Catapult」を適用。その結果工数を半分以下に削減することができた。

当然ながら「Kopernic」の適用はVerilog HDLのサポート範囲を超える事は出来ない(高位合成ツールの機能をフル活用出来ない)が、山下氏は「Kopernic」と高位合成ツールを上手く組み合わせる事でRTLよりも抽象度の高いVerilog HDL設計が実現できると主張。「Kopernic」は高位合成の適用範囲を拡大すると同時に設計を楽にすることができると語った。なお、山下氏によると、「Kopernic」は、Xilinxの「Vivado-HLS」、Cadenceの「CtoSilicon」にも対応おり、要望があれば他社への提供も検討可能だという。

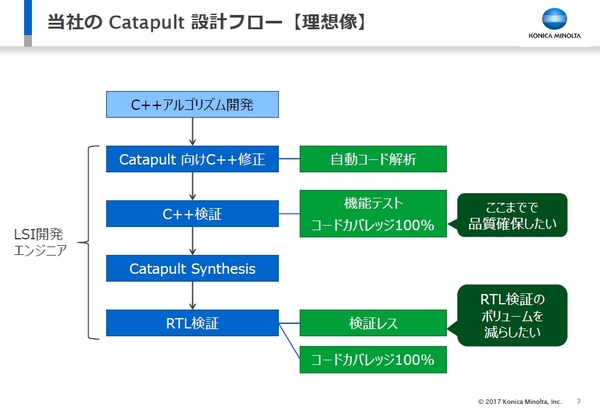

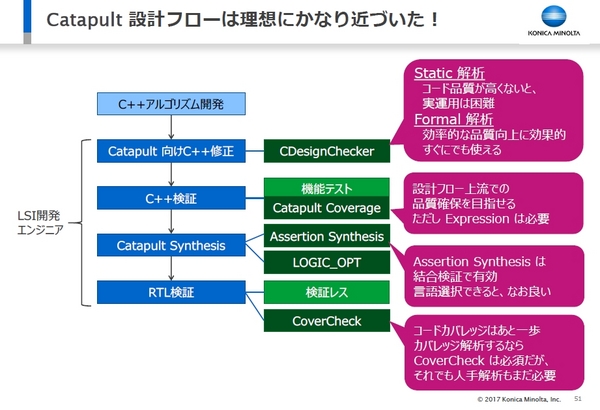

コニカミノルタの河邉氏は「Catapult」のユーザーとして、「Catapult」の設計フローを補完する検証ツール「Catapult Design Checker(CDesignChecker)」および「Catapult Coverage(CCOV)」の評価結果について語ってくれた。

河邉氏によると同社のモチベーションは「Catapult」を用いた設計フローの効率的な品質向上で、具体的な要求としては「Catapult」向けC++コードの自動解析、それから高位合成前後の検証(C++およびRTL)におけるコードカバレッジ100%の達成がある。そこで今回これらの要求に対応するMentorの各ツールを評価してみた。

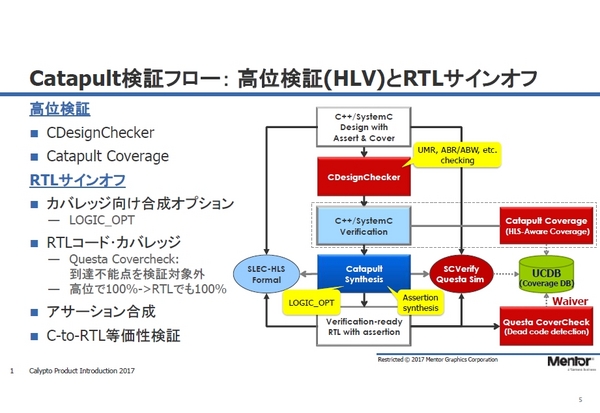

「CDesignChecker」はC++/SystemCコードの解析ツールで、スタティック解析およびフォーマル解析の2つの解析で合成前、シミュレーション前に各種コーディング・エラーを簡単に解析できる。河邉氏が実際に「CDesignChecker」を使用したところ、フォーマル解析で実用レベルの解析結果を得ることができた。(スタティック解析ではエラー検出数が多過ぎて解析困難だった)河邉氏によると、仕様に合わせた入力制約を指定する事で擬似エラーの証明も簡単であるという。

「Catapult Coverage(CCOV)」は間もなく正式リリースされるC++カバレッジ機能で、RTLシミュレーションと同じようにカバレッジ結果をカバレッジ・データベース「UCDB」に保存し、検証環境「Questa」で確認できる。合成制約も考慮してカバレッジを取得できるのは「Catapult Coverage(CCOV)」ならではの機能という事だ。河邉氏は同機能については「GCOV」より優れているとしながらも幾つかの課題を指摘。中でも「Expression」のコードカバレッジについては、RTL設計者からすると欲しいところとコメントした。(現状未対応)

RTLカバレッジについては、未到達箇所の原因を解析する「Questa CoverCheck」と、カバレッジ向上のための合成最適化オプション「LOCIC_OPT」を評価した結果を紹介。「Questa CoverCheck」についてはRTLカバレッジを取る上で必須とし、「LOCIC_OPT」については元々高いカバレッジを得られているので効果は限定的だったと語った。

最終的な河邉氏の評価は、目的としているC++のレベルでの品質確保において「Catapult」の各種オプション機能はある程度有効であるというもので、「Caltapult」の設計フローはかなり理想にかなり近づいたと締め括った。

|ページの先頭へ|