NEWS

Cadenceが高性能ビジョン/イメージング向けの強力な低消費電力DSPコアを市場投入

2015年10月7日、Cadenceは同社最新のDSPコア「Tensilica Vision P5 DSP」のリリースを発表した。

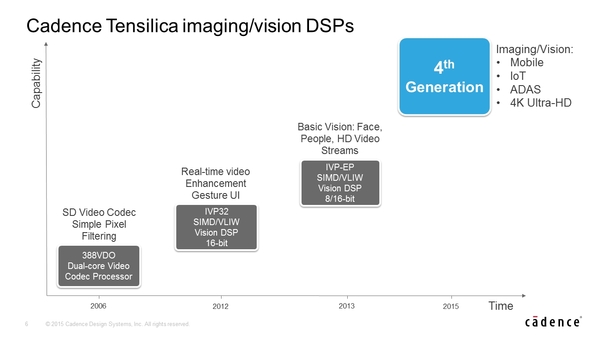

Cadenceによると新製品「Tensilica Vision P5 DSP」は、既存のDSPコア「IVP-EP」と後方互換の後継製品でTensilicaのイメージ/ビデオ向けDSPとしては4世代目にあたる製品。その名の通り各種ビジョン・アプリケーションをターゲットとしている。

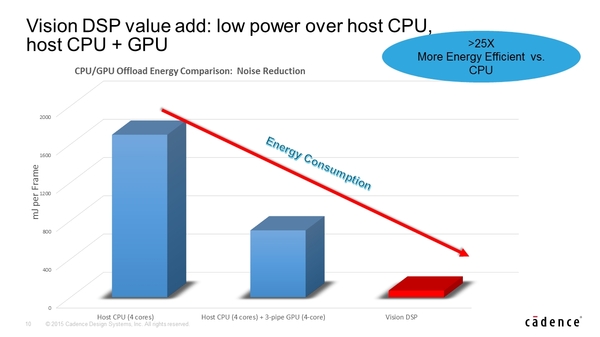

従来品と大きく違うのはそのパフォーマンスと消費電力で、「Tensilica Vision P5 DSP」は既存の「IVP-EP」よりもパフォーマンスが最大13倍にまで向上されており、16nm FinFETプロセスでの実装では動作周波数が最大1.1GHzに達する。消費電力も従来製品比で平均1/5と大きく電力効率が高められており、これら機能強化により、モバイル機器に加えてADASやドローン、セキュリティ・カメラなどの先進のビジョン・タスクにも対応可能となる。また、従来ハード処理していた部分やGPUで処理していた部分をDSPで置き換える事も可能となる。当然ながらDSPを利用すればプログラマブルに、そして低消費電力で処理できる。

「Tensilica Vision P5 DSP」の優れたパフォーマンスには幾つかの仕掛けがある。

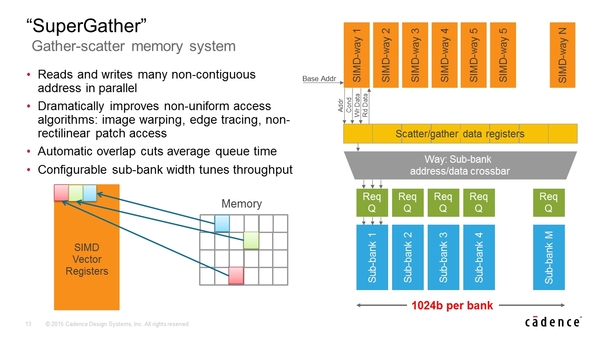

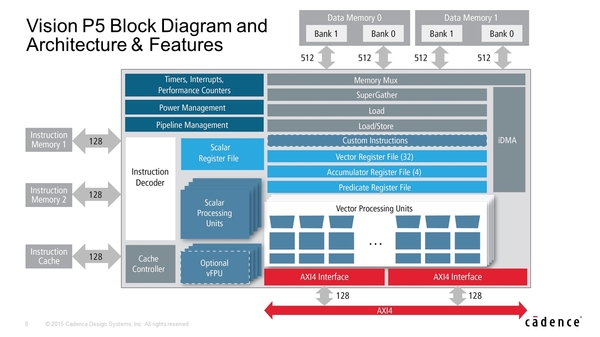

まず、16way単精度の32-bit Vector Floating-Point Unitがオプションで用意された。これはTensilicaの他のコアで培われた技術で、これによりGPUコードのポーティングも容易になった。また、「SuperGather」技術と呼ばれるメモリアクセス向上技術が取り入れられ、業界最大の1024-bitのメモリ帯域幅を更に活かせるようになった。更にISPへの接続も視野にAXI4バスのインタフェースが2チャンネルとなった。片方はHost用としての利用を想定している。その他、DSPコア全体としては命令セットの強化も進められ、更に400以上の命令が追加されている。

電力効率の向上は「Tensilica Vision P5 DSP」の大きなメリットだが、Cadenceの実例によると、ノイズ・リダクションをCortex-A9のクアッドコアCPUで実行する場合と、それにGPU(3-Pipe,4Core)と「Tensilica Vision P5 DSP」を追加した場合とでは、電力効率において25倍もの性能差が生じるとの事。一部先行顧客は「Tensilica Vision P5 DSP」の電力効率を活かし、サーバー向けの利用に取り組んでいるという話だ。

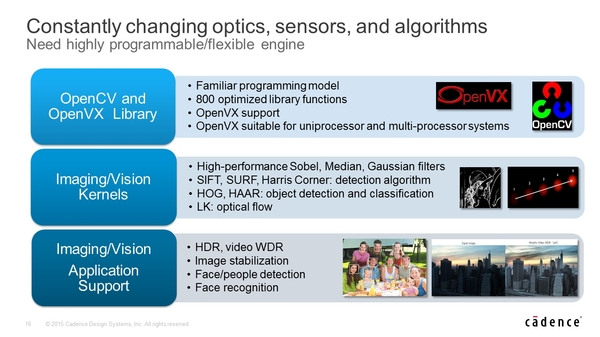

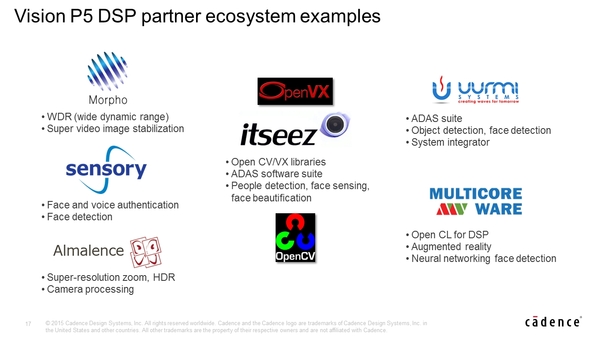

なお、Cadenceはソフトウェア面の対応として、「Tensilica Vision P5 DSP」の命令セットに最適化したOpenCV/OpenVXのライブラリ約800種を無償提供するほか、イメージ/ビジョン向けのより粒度の細かいカーネル・ライブラリも用意。また人体検出や顔認識などの内製アプリケーションも用意されている。その他各種サードパーティーによるアプリケーションのポーティングも既に進められているという。

※画像は全てCadence提供のデータ

「Tensilica Vision P5 DSP」は既に出荷が開始されており、間もなくESが出てくる先行顧客もいるという話だ。

|ページの先頭へ|