NEWS

Mentorのローパワー検証ツールがUPF Successive Refinement Methodologyをサポート

2015年9月10日、Mentor Graphicsは、同社のローパワー検証ツールがUPF Successive Refinement Methodologyをサポートした事を発表した。

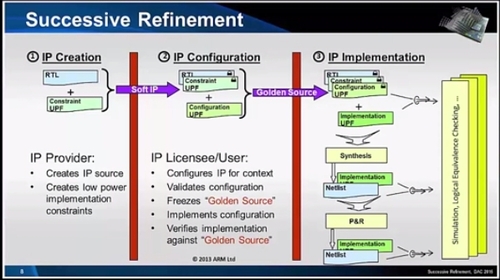

UPF Successive Refinement Methodologyとは、パワー仕様記述フォーマットUPFを用いたローパワー設計のためのメソドロジで、ローパワー設計におけるUPFの利用価値をこれまで以上に高めるもの。同メソドロジはIEEE1801 UPF仕様の主査であるARMのエンジニアが提唱したもので、Mentorと共にその実現に向けて取り組んできたとの事。

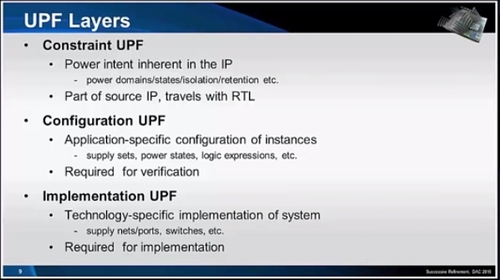

その思想には、IPベンダの提供するUPFをIPユーザーがターゲット・アプリケーションやターゲット・デバイスに応じて詳細化して利用するという考えが込められており、UPFをIP/ブロック用の制約UPF、検証用のコンフィギュレーションUPF、実装用UPFの3種類に分けて設計工程に合わせて作りこみながら利用する。これによりUPF利用者の立場とターゲットに応じたより価値の高いローパワー検証をより効率的に実践できるようになる。

※画像はMentor社Web公開ビデオからの抜粋

Mentorは今回このUPF Successive Refinement Methodologyを「Questa® Power Aware Simulation」および「Visualizer Debug Environment」にてサポート。同メソドロジを用いたローパワー検証フローの加速と自動化を実現するとしている。

UPF Successive Refinement Methodologyの詳細については、Mentorが下記URLにてDAC2015での解説ビデオを無償公開している。

http://www.mentor.com/products/fv/resources/overview/successive-refinement-a-methodology-for-incremental-specification-of-power-intent-using-upf-2a5e8c03-f46c-4d78-b108-d143cb3a0073

|ページの先頭へ|