NEWS

Cadenceが設計生産性を最大10倍向上できる新型論理合成ツール「Genus」を投入

2015年6月3日、Cadenceは新製品の論理合成ツール「Genus」のリリースを発表した。

「Genus」は、Cadenceの既存製品「RTL Compiler」の後継となる論理合成ツールで、28nm以降の先端大規模チップの設計を主たるターゲットとしている。Cacdenceは「Genus」を利用する事で「RTL Compiler」と比較して設計生産性を最大10倍に向上できるとする。

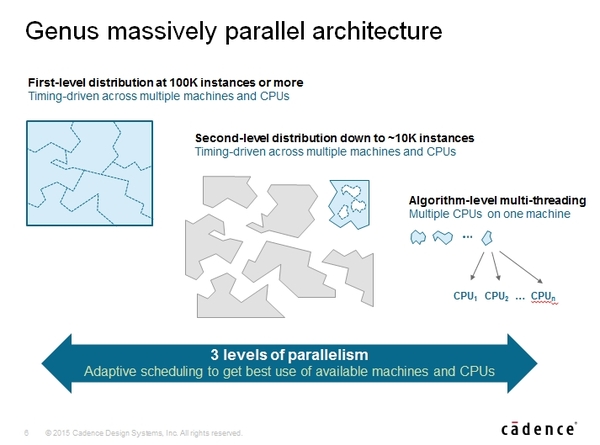

「RTL Compiler」に対して「Genus」がどう進化したかと言うと、まず合成の処理時間が最大5倍高速になった。これは新しい大規模分散型並列処理アーキテクチャーの採用によるもので、分散効率が高められただけでなく、デザインをより細かく広範囲に分散処理する事が可能となった。聞くところによると論理回路レベルで分散処理を行うことも可能なようだ。

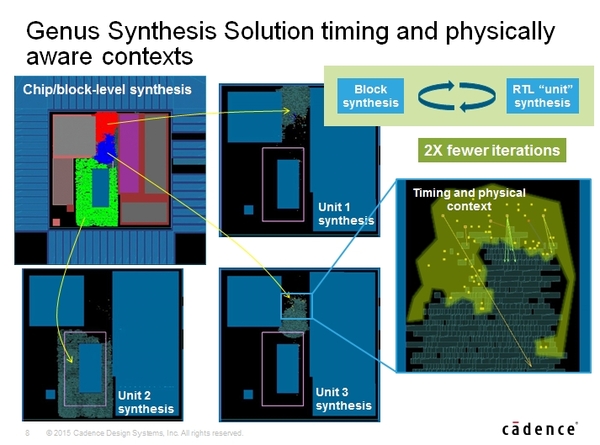

また処理速度に加えて、「Genus」では階層設計における上位レベル(チップレベル)の合成と下位レベル(ユニットレベル)の合成との間のイタレーションを半分以下にできるようになった。言い換えればイタレーションの生産性は2倍向上という事で、5倍の速度向上と合わせて最大10倍の生産性向上という計算だ。

イタレーション削減の秘訣はフィジカル情報を考慮したコンテキスト生成機能で、上位レベルの合成を行う際にコマンド一つで下位レベルの配線およびタイミングに関する情報を読み取る事が可能となった。この機能によって上位レベルにおける合わせ込みが非常に楽になるという。

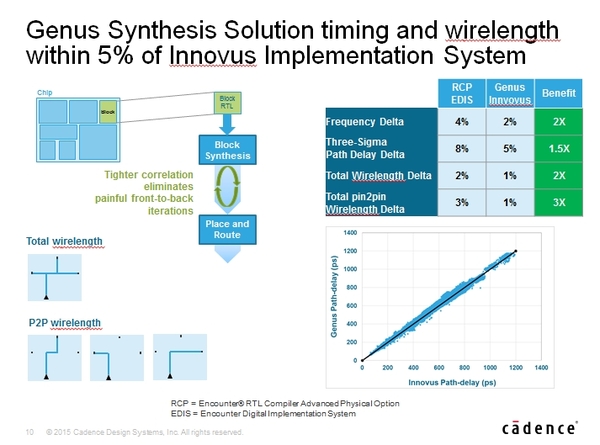

更に「Genus」は下流の新型配置配線ツール「Innovus」との高い相関性が確保されており、合成と配置配線のイタレーション工数も大きく削減出来るようになった。元々「RTL Compiler」は配置配線ツール「Encounter」との相関性の高さがウリの一つであったが、「Genus」と「Innovus」はそれを上回るタイミングおよび配線長の高い相関性を実現しており、その誤差は5%以内に収まるという事だ。理由は寄生抽出、遅延計算、配線経路の見積エンジンを「Genus」と「Innovus」は全て共有しているため。この精度の高さはインプリメント工数の多くを占めるイタレーション工数の削減に大きく効くと同時に配置の改善にも役立つものだ。

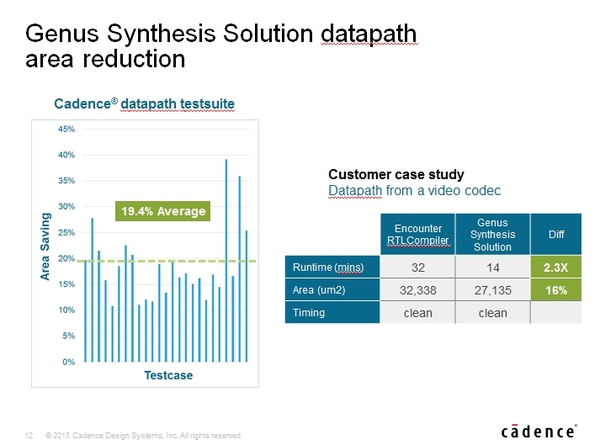

もう一つ、今回の新製品「Genus」の特筆すべき能力はPPA最適化機能だ。新たなアルゴリズムをベースとした最適化エンジンでは、各々データパスの局所的な最適化だけではなくデザイン全体を見たベストなトレードオフ(最適化)を行うことが可能で、ワードレベルの演算子まで踏み込んだ形でRTLを最適化できる。その結果、データパス・エリアを平均20%も削減する事が可能という事で、このエリア削減効果はパワー削減の面でも大きい。

なお、「Genus」のGUIは配置配線ツール「Innovus」、タイミング解析ツール「Tempus」と共通化されており、これら3ツールはコマンド体系やレポート・スタイル等も統一されている。どれか一つのツールを覚えれば自然と他のツールも扱い易く、ツールのよる処理結果の比較などもし易い。

「Genus」は既に出荷が開始されており、プレスリリースにはTexas Instruments社がユーザーとしてコメントを寄せているほか、別のプレスリリースにてImagination Technologies社の「Genus」を利用した成功事例が発表されている。両社共に「Genus」を使うことでTATを5分の1以下に短縮できたとしている。

|ページの先頭へ|