NEWS

TSMC 16nm FinFET/16nm FinFET+プロセスが始動-中国HiSiliconが16nm SoCを開発

2014年9月30日にサンノゼでTSMCのプライベート・イベント「TSMC 2014 Open Innovation Platform® Ecosystem Forum」が開催される。

同イベントではここ数年TSMCの最新プロセスのリファレンス・フローが発表されるのが恒例となっているが、今年は16nm FinFET+プロセスのリファレンス・フローが発表される予定で、それに先行してEDA大手各社が自社ツールの認証について一斉にアナウンスを開始した。

Cadenceは具体的なツール名を挙げていないが、これまでの経緯からするとインプリメンテーション環境「Encounter」の他にタイミング検証ツール「Tempus」、カスタム設計環境「Virtuoso」などが16nm FinFET+プロセスのリファレンス・フローに認証されている見通し。同イベントでは16nm FinFET+プロセスをターゲットとした「DDR4 Subsystem」のインプリ事例の講演なども行うようだ。

Mentorは今年3月に買収したBerkeley Design Automationの「Analog FastSPICE (AFS™) Platform」、「AFS Mega」、そして「Eldo」の3種類のSPICE製品が16nm FinFET+プロセスのリファレンス・フローに認証されたことを発表。配置配線ツール「Olympus-SoC™」と物理検証ツール「Calibre」も既に16nm FinFET+プロセスの認証に向けて拡張済としている。

Synopsysは具体的な製品名を挙げていないが、「Galaxy™ Design Platform」が16nm FinFET+で利用可能になったとしており、同プラットフォームに含まれる各種デジタル/カスタム設計ツールがリファレンス・フローに認証されている事を暗に示している。

尚、CadenceとSynopsysの両社は次世代のTSMC 10nm FinFETプロセスに向けた設計ソリューションについても言及しており、特にSynopsysは10nm FinFETプロセスに関するTSMCとのコラボレーションを強調。既に「Galaxy™ Design Platform」が10nm FinFETプロセスで利用可能としている。

実際のチップ開発事例としては、中国Huaweiの半導体部門子会社であるHiSiliconがTSMC 16nm FinFETプロセスを用いた業界初となるARMベースのネットワーク・プロセッサを設計したことを発表。

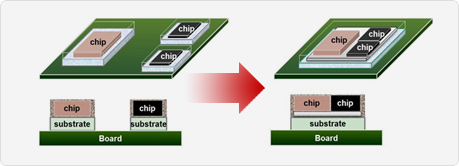

Hisiliconが作ったネットワーク・プロセッサは、ARM Cortex-A57を32個搭載するもので、TSMCのヘテロジニアスCoWoS 3D ICパッケージ・プロセスを用いて16nm ロジック・チップと28nm I/Oチップを統合する形で実現されているとの事。同ネットワーク・プロセッサは、28nm HPM製品と比較して同じパワーで40%の速度向上、同じ速度で60%パワー削減を実現しているという。

※TSMC

|ページの先頭へ|