NEWS

CadenceがVirtex-7ベースの新型プロトタイピング・システム「Protium」を発表

2014年7月18日、Cadenceは新型のラピッド・プロトタイピング・システム「Protium」を発表した。

発表当日みなとみらいで開催されたCadenceのプライベート・セミナー「CDNLive Japan 2014」にて、新製品「Protium」について話を聞いた。

CadenceがFPGAベースのプロトタイピング・システムを初めて発表したのは約2年前、「Cadence Rapid Prototyping Platform(RPP)」と命名されたその製品は某ボード・メーカーの製品を利用したもので、AlteraのFPGA「Stratix-4」をベースとしたものだった。

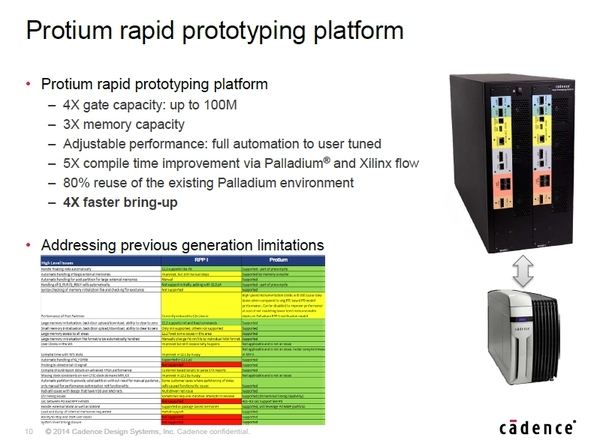

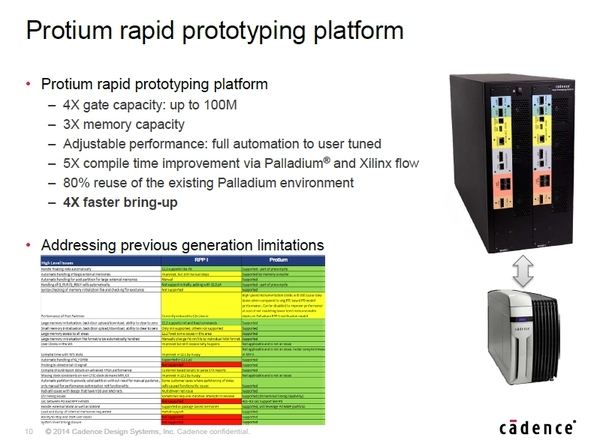

今回発表された「Protium」は、Xilinxの28nmFPGA「Virtex-7 2000T」をベースとしたもので、Cadenceのエミュレータ「Palladium」とのフロー互換など製品としてのコンセプトは前身の「RPP」と同じだが、その中身は全く異なる製品と言える。

まずFPGAが「Virtex-7 2000T」に置き換えられた事でそのデザイン容量は「RPP」の4倍に当たる最大1億ゲートへと拡張された。「Protium」のベース・ボードは、「Virtex-7 2000T」を2個搭載するものと4個搭載するものの2種類があり、最大8個のFPGAで1億ゲートに対応という計算だ。更にオン・ボード・メモリは「RPP」の3倍の最大64GBとなった。

「Protium」の最大の特徴は、プロトタイピング・システムとしてのセット・アップ時間の短さで、デザインのコンパイル時間が改善され従来比5倍の速さでRTLを合成できるようになった。具体的には7000万ゲート規模のデザインを約1時間でコンパイル可能で、Cadenceは競合製品と比較してセット・アップ時間を70%短縮できるとしている。

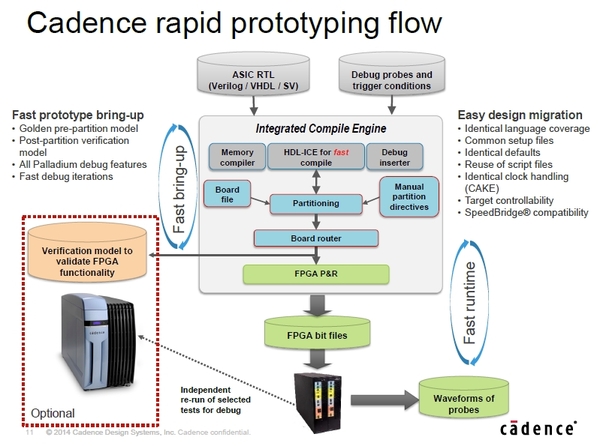

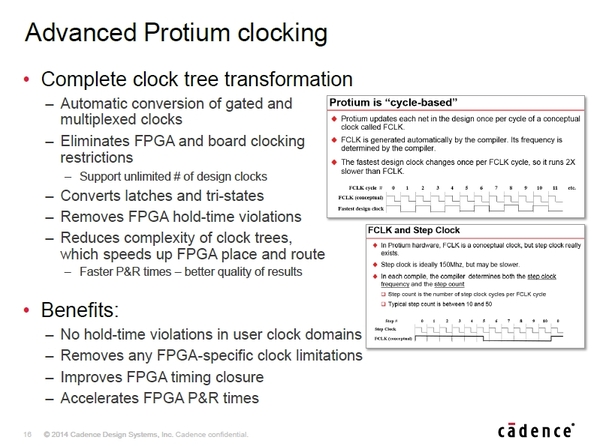

コンパイルの高速化はエミュレータ「Palladium」の環境を再利用する事で実現されているという事だが、コンパイラ内部の各種処理でも様々な工夫が施されており、それらがセット・アップ時間の短縮に大きく貢献している。例えばFPGA実装向けにクロック・ツリーの自動再構成機能があり、非同期のユーザー・クロックのふるまいを継承しながらデザインを一つのクロック・サイクル・ベースにする事が可能。一本の高速クロックで全てのクロックを同期するこの手法により、ホールド・タイムの違反やクロック数の制限を無くす事ができ、タイミング収束や配置配線処理も加速可能となる。また、コンパイラにはスタティック・タイミング解析機能も備えられており、これもセット・アップ時間の短縮に貢献する。

更にFPGAの配置配線前にデザインを検証するためのソリューションとして、「Palladium」向けの検証モデルを生成する機能がオプションで用意されており、これによりデザインをFPGAに実装する前に数時間でデバッグできる。

更にFPGAの配置配線前にデザインを検証するためのソリューションとして、「Palladium」向けの検証モデルを生成する機能がオプションで用意されており、これによりデザインをFPGAに実装する前に数時間でデバッグできる。

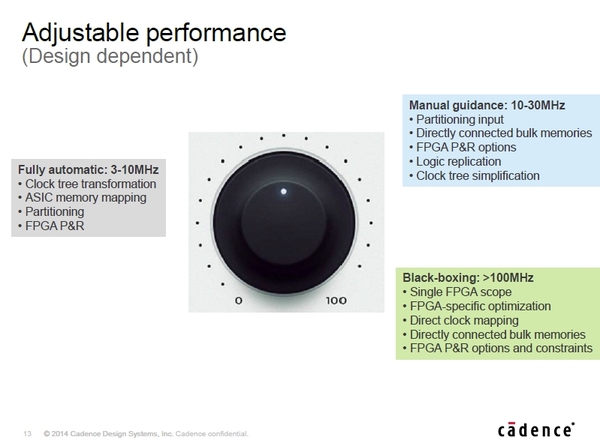

尚、プロトタイピング・システムのセット・アップをツールに任せて全自動で行うと最も短時間で数日から数週間で環境を構築できるが、その場合のパフォーマンスは3M-10MHz程度。デザインの分割など人手を駆使して様々な最適化を図れば10-30Mhzのパフォーマンスを実現可能との事。デザインの一部のブロックを単一のFPGAにカプセル化して実装する「Black-Boxing」という手法では100Mhz近い優れた性能を実現することも可能で、PCI-ExpressやUSBなどのアプリケーションが「Black-Boxing」に適しているとの話だった。

ソフトウェア開発のニーズとFPGAの進化により、FPGAベースのプロトタイピング・システムの市場には様々な製品が乱立しており激しいシェア争いを繰り広げているが、今回「Protium」によって「Virtex-7 2000T」ベースという意味でようやくCadenceは他社製品と同一の土俵に立った事になる。業界最新のプロトタイピング・システムとしての「Protium」のポテンシャルとFPGAベースのプロトタイピング・システムはエミュレータとの併用が多いという事を考えると、後発のCadenceにもまだまだチャンスはあると言えるだろう。

※ケイデンス・デザイン・システムズ社

※ケイデンス・デザイン・システムズ社

|ページの先頭へ|