NEWS

【51DAC】GoogleがVP9のデコーダ開発にCalyptoの高位合成を採用、合成用ソース他一式をパートナーに無償配布

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

Calyptoのブースでは、同社製品の3本柱であるPower最適化ツール「PowerPro」、高位合成ツール「Catapult」、シーケンシャル等価性検証ツール「SLEC」を展示。「Catapult」に関してはブース内でGoogleとCienaによる事例のプレゼンが行われていた。

ここでは話題となっていたGoogleによる高位合成ツール「Catapult」の適用事例を中心にCalyptoの展示内容をを紹介する。

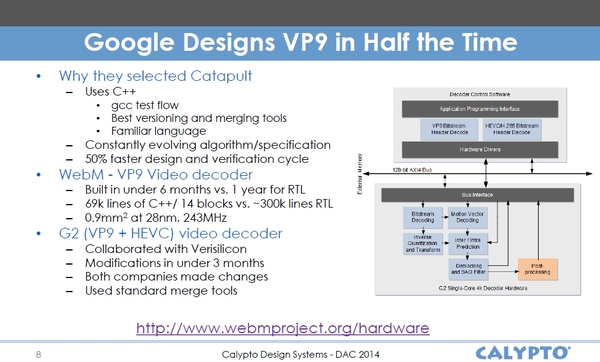

Googleと高位合成、一見結びつかない話と思いつつその詳細をCalyptoのマーケティングVP Mark Milligan氏に聞いたところ、Googleは誰もが無料で利用できるオープン・ソースでロイヤリティ・フリーなビデオ・フォーマット「WebM」を推進する「WebM」プロジェクトを主導しており、自ら開発したそのコーデック技術「VP9」のデコーダ開発においてCalyptoの高位合成ツール「Catapult」を採用した。

「Catapult」の採用理由としては、その合成品質やC++入力に対応している点などが挙げられるが、面白いのは「WebM」プロジェクトの一貫として「VP9」を普及させるために、そのデコーダ回路のRTLと合わせて「Catapult」向けの合成用のC++ソースコードと合成スクリプトを無償でパートナーに公開したという点。実際にGoogleのパートナー各社はこれを利用し10種以上のチップをテープアウトしているという話だ。

ちなみにその先陣を切ったのはVeriSilicon社で、同社はHEVC(H.265)とVP9双方に対応した「Hantro G2ビデオデコーダーIP」を約1年前に開発。同IPの開発はGoogleから無償提供されたCatapult向けのC++記述と合成スクリプト、そして自社のIPを元に進められ、わずか3か月で設計を済ませたという。

Googleが採用したツールという事で「Catapult」の評価は高まると思われるが、それ以上にGoogleのパートナー各社が「Catapult」を利用するとなるとCalyptoにとってビジネス的なメリットも大きいだろう。

ブース内で行われていたもう一つのCiena社の事例は詳細は聞けなかったが、同社のネットワーク向けのコヒーレント光プロセッサー「WaveLogic 3」のDSPブロックを「Catapult」で設計したという事例で、ビット・レート100Gbit/s以上という目標を達成。設計及び検証期間の短縮にも繋がったという。

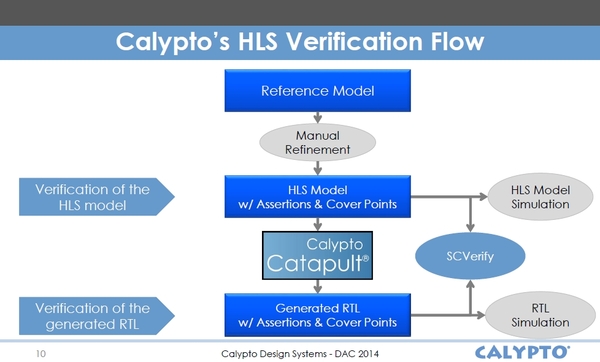

尚、 「Catapult」のアップデートとしては、新たにアサーションやカバー・ポイントをデザインと共に合成されるRTLに挿入する機能が備えられた。これにより、合成モデル (C++、SystemC)をシミュレーションで検証する際に、アサーションによる検証や、カバレッジを取るだけではなく、それらをRTLでの検証にも活用できるようになり、特に他のブロックと結合した際の検証で検証効率を上げることが出来るようになった。

「Catapulut」にはシミュレーション・ベースの検証環境「SCVerify」が備えられており、合成モデル(C++)とそのテストベンチから、自動的に合成されたRTLの検証環境を構築し、シミュレーションを実行することが可能である。

もう一つの同社の主力製品「PowerPro」に関しては、新機能として「Physical-aware power analysis」という解析機能が追加された。これは文字通りフィジカル・ベースのPower解析を行うもので、RTLの合成結果をバック・アノテーションしてPower解析を実行。これによりパワー解析精度を向上できるという。ちなみにRTLでのパワー・リダクションに関して「PowerPro」はここ7-8年他社製品に負けたことがないと聞いたが、新機能「Physical-aware power analysis」を用いれば更に質の高いローパワー化が期待できるだろう。

※画像は全てCalypto提供のデータ

|ページの先頭へ|