NEWS

【SCJ2014】富士通マイクロソリューションズ、フリーツールを活用してSystemC開発を効率化

2014年6月20日、新横浜のホテルで今年で第9回目の開催となるシステム記述言語SystemCにフォーカスしたセミナー「SystemC Japan 2014」が開催された。今年は昨年を上回る延べ250人の参加者が集まり、高位合成の話題を中心に様々な発表が行われた。

ここでは富士通マイクロソリューションズの鈴木晃一氏による講演、「気軽に試せるSystemC開発-ソフトウェアツールを活用しよう-」について紹介する。

鈴木氏はハード設計関連の各種セミナー、イベントで様々な講演経験のあるハードウェア設計者で、SystemCを用いた設計に関して豊富な実績を持つ人物。今回の講演ではそんな鈴木氏が自ら体験したフリー(無償)のソフトウェアツールによるSystemC設計の効率化手法を紹介してくれた。

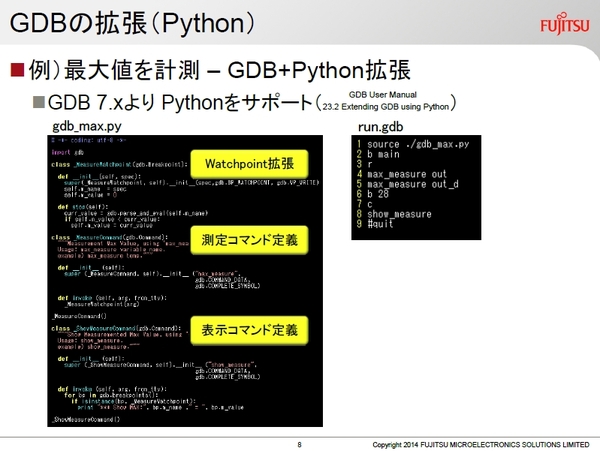

鈴木氏が最初に紹介した手法は、設計フェーズにおいてGNUのデバッガ「GDB」を活用するというもので、アルゴリズムをハード化する際に必要となる量子化作業(ビット幅の確定)の効率化を狙うもの。GDBのコマンドや測定用のソースを使うことで、例えば整数の最大値の計測など、prinf文やstd::coutで値を計測したりテキストにダンブするよりも効率的に計測できると鈴木氏。ただ、普通にGDBを使うだけではデータ型毎に関数を用意しなければならないなど応用が効かないため、鈴木氏はスクリプト言語「Python」を使ってGDBの拡張を試みた。

鈴木氏が行ったGDBの拡張は、ウォッチポイントの拡張、GDB測定用コマンドの追加、表示コマンドの追加などで、GDBにPythonのコードを読み込ませる事でこれらを実現した。Pythonを利用すれば様々な拡張が可能で非常に便利だという。

次に紹介してくれたのは設計フェーズにおいてSystemCコードの複雑度を測定するという手法。この手法ではCおよびC++言語のフリー(無償)のコード解析ツール「CCCC」を利用した。

鈴木氏によると同ツールを利用するとコード中の基本パス数を表す「MVG値」を測定することが可能で、その値が大きければ大きいほど複雑なコードと判断できるとの事。鈴木氏はこの「CCCC」をSystemCコードにも利用できないかと考え、一般的なソフトウェア開発でのMVG値の基準値に対して、実際の開発で記述した高位合成向けのSystemCコードの測定結果がどうなるか関数ごとに計測した。

その結果、MVG値が非常に高く「コードを理解不能」と判断される計測結果が多数あった。鈴木氏が着目したのはその計測結果と高位合成結果の相関性で、MVG値の高いブロックは高位合成が不可能であったのに対し、MVG値の低いブロックは合成品質はともかく高位合成可能だった。そのことから鈴木氏はSystemC開発においても「CCCC」を適用する事でそのコードの複雑度が数値から判断できるだけでなく、高位合成に入力できるかどうかの判断も可能かもしれないと語った。

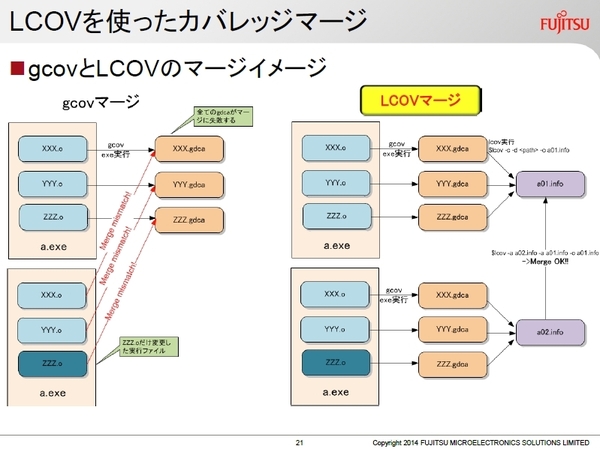

続いて紹介したのは検証フェーズのコード・カバレッジ計測に対して「LCOV」を使うという手法。「LCOV」はGNUのコンパイラgccに付属するコード・カバレッジ計測ツール「gcov」のグラフィカル・フロント・エンド環境で計測結果をHTMLで出力するなど非常に結果が見やすいと鈴木氏。更に「LCOV」の「tracefile」を使えば「gcov」ではうまく出来ないコード・カバレッジ結果のマージにも対処できるとの事だった。

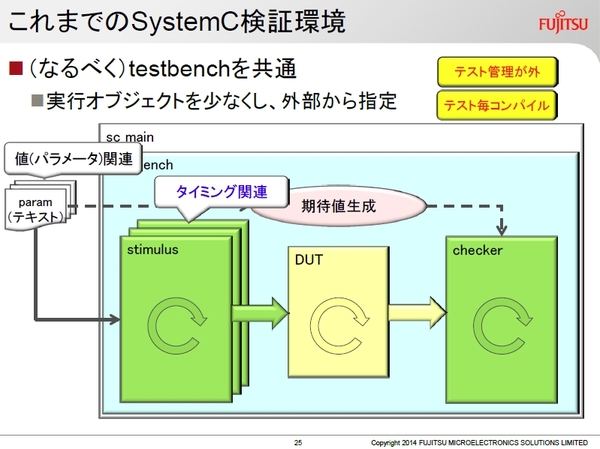

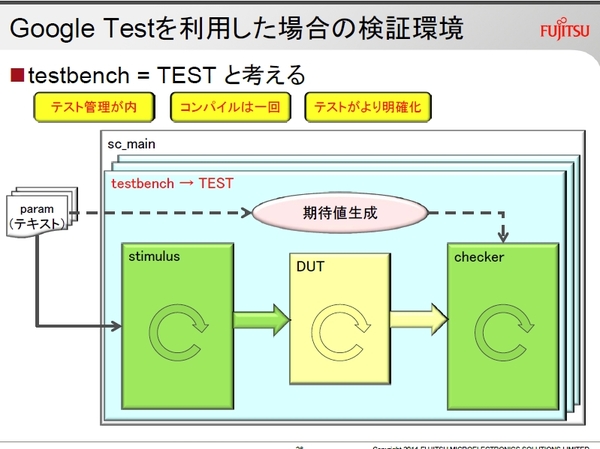

鈴木氏が最後に紹介したのは検証フェーズでのSystemC検証環境構築に関するもので、C++向けのテストフレームワークを活用するというもの。世の中に幾つか存在している無償のフレームワークの中から「Google Test」を用いた手法を紹介してくれた。

鈴木氏によると「Google Test」を用いたテストフレームワークでは、検証メソドロジUVMにおけるUVM testのようにTestbench=TESTという考えで一つの実行オブジェクトで複数のテストを行うことが可能。テスト毎にコンパイルする必要が無く複数のテストを単一のオブジェクトの中で管理することができ、検証項目に合わせてTestbenchやcheckerを作成できるためテストの明確化にも繋がるとの事だ。

但しSystemCの環境では連続してテスト実行できないため、鈴木氏は連続実行するためにグローバル関数「sc_get_curr_simcontext」のメンバー関数「reset」を利用して連続テストを実現。但し「sc_get_curr_simcontext」はSystemCのLRMに載っていないので使用はご注意下さいとの話だった。

※画像は全て鈴木氏の講演データ

以上、鈴木氏が紹介してくれた各手法は、講演のタイトル通り「SystemC環境で気軽に試せる」という点に主眼が置かれており、無償のツールがベースとなっているためSystemCビギナーのHDL設計者にとっては有益な情報と思える内容だった。また、ソフトウェア開発のようにある程度無償のツール環境だけで様々な試行が可能な点もSystemCの良さの一つと実感する講演であった。

ちなみに鈴木氏の所属する富士通マイクロソリューションズでは、90年代後半からSystemCの取り組みを開始。その豊富な経験をもとに各種SystemC開発関連のサービスを提供しているという事だ。

|ページの先頭へ|