NEWS

【SCJ2014】三菱電機、アルゴリズム開発者がHEVC符号化を高位合成だけで回路実装できた訳

2014年6月20日、新横浜のホテルで今年で第9回目の開催となるシステム記述言語SystemCにフォーカスしたセミナー「SystemC Japan 2014」が開催された。今年は昨年を上回る延べ250人の参加者が集まり、高位合成の話題を中心に様々な発表が行われた。

ここでは三菱電機の山本亮氏による講演、「HEVC方式によるSHVリアルタイムエンコーダ開発への高位合成適用事例」について紹介する。

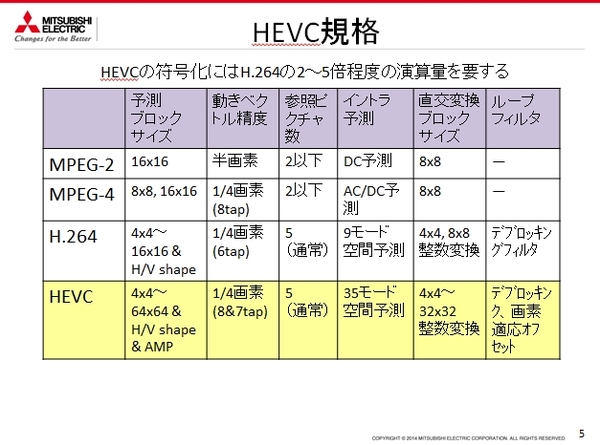

SHVはNHK技研が開発した8Kにあたる次世代のスーパーハイビジョン国際規格で、2013年にNHKと三菱電機が世界初となるHEVC符号化方式を開発している。今回の山本氏の講演は同HEVC方式のSHVエンコーダをRTLを書いたことのないアルゴリズム開発者が中心となって高位合成で開発したというのが大きなポイントとなる。

山本氏によると高位合成を使ったモチベーションは、出来るだけ少人数かつ短期間でチップを開発したいという開発の効率化にあり、その背景には映像規格もののチップとして出来るだけ早く市場に投入したい(シェアを獲得したい)という要求や映像系専門のLSI設計者の減少、海外との競争で高まる開発コストの削減要求などがある。

また実際の開発現場では、アルゴリズム開発者とRTL設計者の両者によるキャッチボールで開発を進めていたが、どちらかが開発全体をカバー出来れば開発を効率化できると考え、アルゴリズム開発者が高位合成を使ってRTLを設計するという開発体制に辿り着いた。アルゴリズムの習得とRTL設計の習得を考えた場合、アルゴリズム開発者によるSystemCの習得(高位合成の習得)が最も早く開発がスムーズという判断だ。実際にアルゴリズム開発者は半日程度の学習でSystemCをほぼ習得できたという。

しかし、はたしてアルゴリズム開発者だけで回路設計が可能か?

回路品質などの課題を考えた結果、対策として回路全体のアーキテクチャを仕切れるハード設計者を置く事に決定。設計上大事なところはハード設計者が仕切る形とし、高位合成の利用については山本氏がサポートする形を取った。

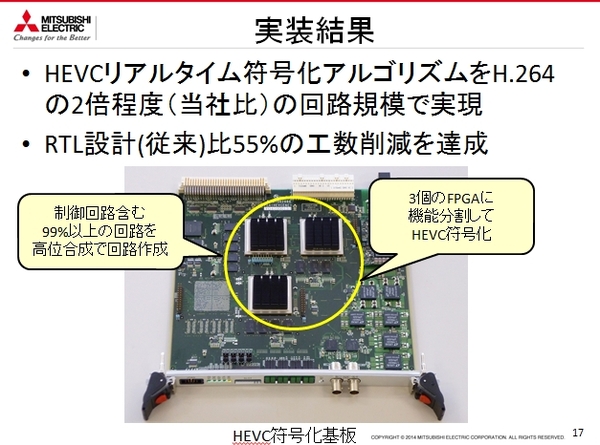

実際のエンコーダの設計では、制御回路も含めて全ての設計をSystemCで実施。これは部分的にHDLを使うなどしてアルゴリズム開発者に負担をかけないためで、既存のRTL資産や外部から調達したIPを除いて回路全体の99%以上をNECの高位合成ツール「CyberWorkBench」を使ってSystemCで設計。見積上のRTL設計による工数と比較して55%の工数削減を達成し、HEVC符号化アルゴリズムをH.264の2倍程度の回路規模で実現する事に成功した。

山本氏によると、この成功の裏には上述した開発体制の他に幾つかのポイントがあった。

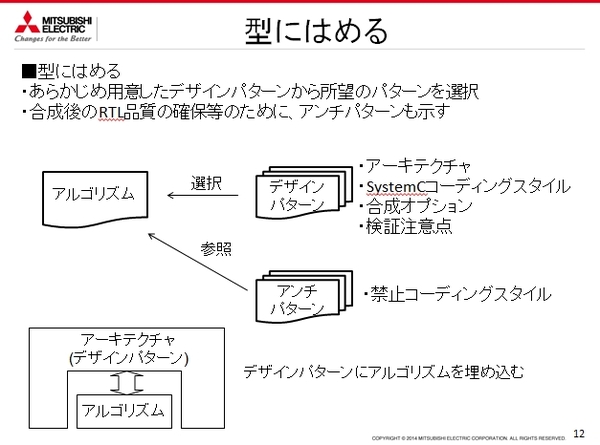

まず、設計にあたっては山本氏が幾つかのデザイン・パターンを用意した。デザイン・パターンにはターゲットとする回路アーキテクチャに応じたSystemCのコーディング・スタイル、使用する合成オプション、検証上の注意すべき点などがまとめられており、アルゴリズム開発者は手掛ける回路に適したデザイン・パターンを選択して設計を進めた。山本氏はこの手法を「型にはめる」設計と表現したが、デザイン・パターンにアルゴリズムを埋め込むという形がこの手法の目指すところで、上手く型にはめるためにツールの特性を考慮したアンチ・パターン(禁止するコーディング・スタイル)も合わせて用意した。

また、回路設計の知識が無いアルゴリズム開発者に対して、演算器の大きさや回路規模が小さくなるコーディング方法など回路規模に関する基本を指南。設計はブロック単位で論理合成結果を確認しながら進め、統合時の性能未達などを事前に回避した。

更にSystemCの実装テクニックとして高位合成用のテンプレートを用意し、パラメータによって複数の回路を合成する方針を取ることで似て非なる回路の設計効率を改善。このテンプレートによるパラメータ化手法は今後の製品展開を見据えた資産流用という意識もあっての対策だったという。

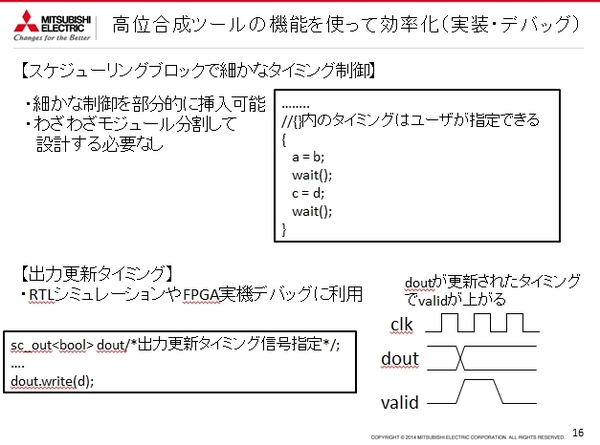

「CyberWorkBench」の機能としては、細かなタイミング制御機能によって一つのソースに制御回路と演算回路を混在できるため、わざわざモジュール分割せずに設計できる点、出力の更新のタイミングを知らせるオプションで回路の性能確認やデバッグが容易に可能となる点などを嬉しいところとして挙げた。

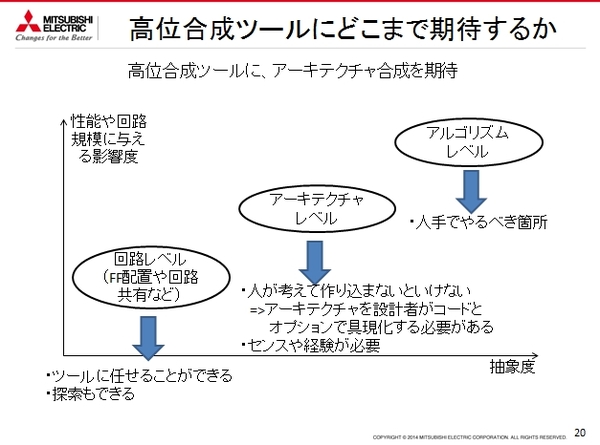

山本氏は講演の終わりに高位合成ツールへの要望として、配線の考慮や合成時間の短縮、ライブラリ・マニュアルの強化などを挙げ、今後は現状の更に上に行くアーキテクチャ・レベルでの合成の実現に期待するとした上で、「高位合成は、HW設計者のためだけのツールではなく、SW設計者やアルゴリズム開発者にとって、なくてはならないモノになる!」とコメント。合わせて発した「これからはアルゴリズムの性能だけを追求していてはダメ。アルゴリズム開発者も高位合成を上手く使って自分のアルゴリズムが安いコストで実現できる事を示していかなければならない」という言葉が印象的だった。

尚、今回の山本氏の講演はSystemC Japanとして公募した講演の一つで、セミナー会場で実施した聴講者によるアンケート結果から最優秀公募講演として表彰され、主催のAccellera Systems Initiativeより賞品としてMac Book Airが進呈された。

※画像は全て山本氏の講演データ

|ページの先頭へ|