NEWS

Low LatencyならFPGA+高位合成、制御回路こそ高位合成、CWB生みの親NEC若林氏が語る※補足訂正あり

2014年2月5日、日本電気株式会社の本社にて、高位合成セミナー「CyberWorkBench Forum 2014」が開催され、100名近い参加者が集まった。

ここでは、同セミナーの冒頭に行われた高位合成ツール「CyberWorkBench」の生みの親である、日本電気株式会社 エンタープライズ共通ソリューション開発本部の若林一敏氏の講演についてレポートする。※補足訂正あり

今回、若林氏が話題に上げた中で興味深かったのが、低遅延(Low Latency)分野で流行っている「FPGA+高位合成」の話、そして制御回路向け高位合成の話の2点。いずれも高位合成技術のトレンドを表す話で、同分野に精通している若林ならではのもの。人によっては高位合成ツールの見方が変わるかもしれない話としてここで紹介したい。

金融分野でのFPGA利用は、株式の高速自動取引における株価ストリームの処理高速化を中心に数年前から北米や欧州で話題となっているが、若林氏の話はFPGAと高位合成を組み合わせて使うことで、容易かつ効果的にLow Latency処理を実現できるというもの。

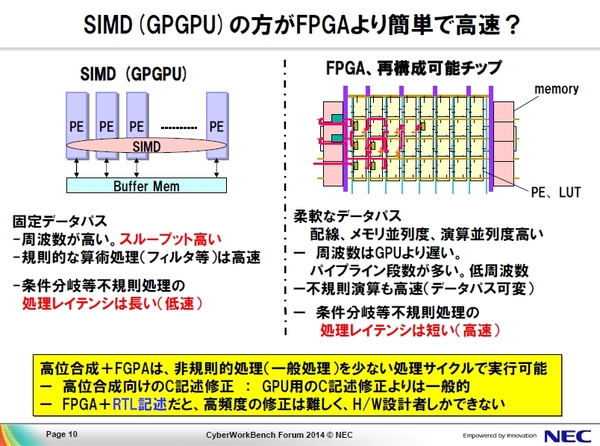

若林氏によるとこの「FPGA+高位合成」は、USの学会などでも活発に議論されており、EDAの学会とは違い最近のFPGAの学会では高位合成関連のセッションが幾つもあるような状況。スループット求めるにはGPGPU、Low Latencyを求めるにはGPGPUではなくてFPGA+高位合成という流れが出てきているとの事で、若林氏はその利点を解説してくれた。

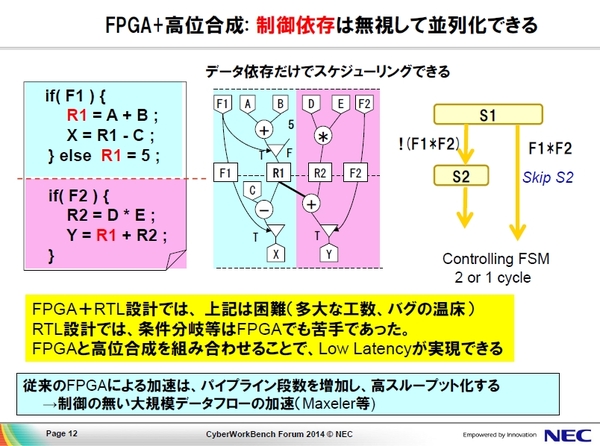

FPGA+高位合成の利点として若林氏が挙げたのは「並列度の高さ」で、高位合成によるCコードのハード化は配線が自由で、演算器、メモリの並列度が極端に高い。またGPGPUは制御の依存関係、複数の条件分岐があると並列化できないが、高位合成の場合は制御の依存関係を無視しデータ依存だけで並列化が可能で、例えばif文が100個ネストしてても並列化できると若林氏。この並列度の高さがLow Latency処理を実現しており、同じ事を従来のRTL設計手法(HDLによる手設計)で実現することは不可能であり、パイプライン段数を増やしてスループットを上げる高速化手法はもはや限界だと若林氏は語った。実際にNECではFPGAを搭載したNIC(Network interface card)を高位合成で開発し、金融向け計算処理の高速化(Low Latency化)を実現しているという。

※画像は若林氏の講演データ

この話と前後して若林氏は、そもそも論として高位合成の使い方についても言及。

プログラム全体のループ部分とか加速したい部分だけをGPGPUやFPGAで加速し、残りの制御をCPUで実施というやり方よりも、Cアルゴリズムを丸ごとハード化というのが高位合成の旨味であり、複雑なアルゴリズムを制御も含めて丸ごとハード化するような使い方が増えてきたとの事。FPGA+高位合成の話はその延長線上にある訳だ。

若林氏は、高位合成ツールの合成する回路は言わば「Program Specific Instruction-set Processor」であり、難しいプログラムのコントロールは全部ステートマシンに押し込み演算器の数を減らして回路を折りたたんでいるプロセッサのようなものと語り、そもそも原理が違うためRTL設計と同じ構造の回路を出そうとしても無理。CでHDLと同じコードを書いて合成しても設計効率は上がらないと指摘。思った通りのアーキテクチャは出せないが、機能は同じでレジスタ間の遅延が可変になるので良しと割り切るべきとした。

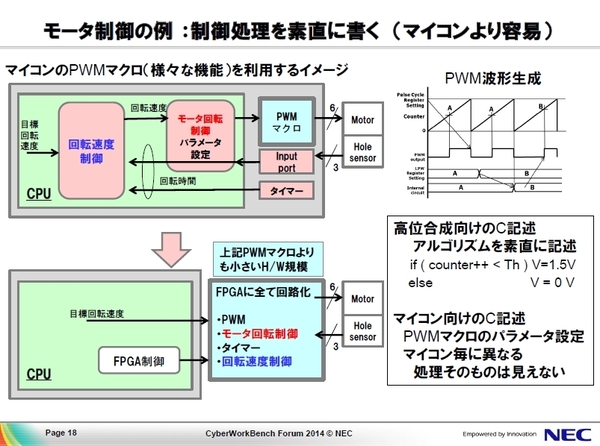

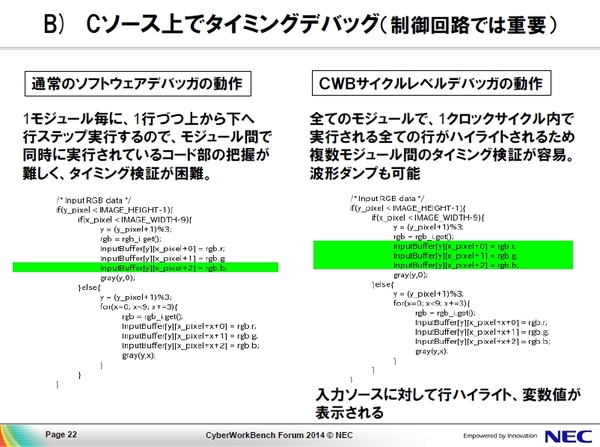

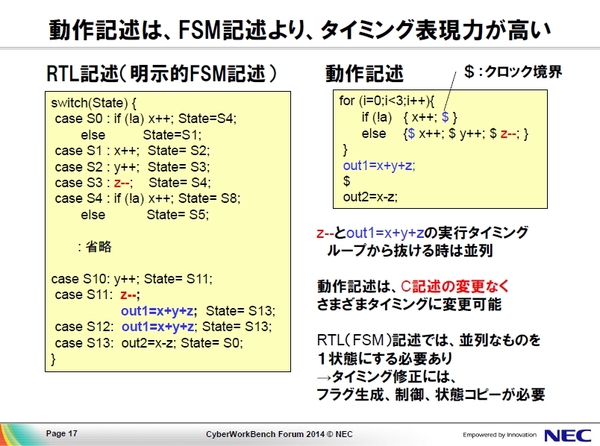

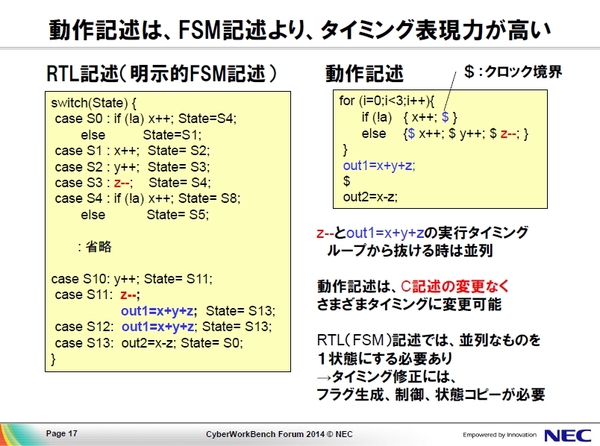

また、定説化している高位合成は制御回路の合成に不向きという話に対して若林氏は、「制御回路にこそ高位合成」とコメント。SystemCのsc_methodでステートマシンを書いて合成するなどナンセンス、sc_cthreadで動作記述から合成するのが本当の高位合成で、Cの動作記述の方がRTL記述よりもタイミングの表現力が高く、C記述を変更せずにタイミングを変更できるのは作業工数やバグ回避の面でも大きなメリットだとした。更に若林氏によると、モータ制御や複数機器のリアルタイム制御などの制御処理をCで記述し、それを高位合成してFPGA化するという従来のマイコン利用とは違う手法が海外で流行りつつあるとの話で、NECでも取り組みを進めているという事であった。ちなみに「CWB」では、合成した制御回路のタイミングをCソース上でデバッグ出来るようにサイクルレベルのCソース・デバッガを用意しているという。

尚、若林氏によると「CWB」は以前、プロ向けのツールとして合成する回路構成を細かくコントロールする方向で開発を進めていたが、現在はプロ向きの制御性を残しつつも、プッシュボタン式に誰でも合成できる「Easy to use」路線を強化する方針に変更。RTL設計とは全く違う発想で簡単に使う。それが高位合成の旨味を引き出す方向だと考えているようだ。

※日本電気株式会社

※日本電気株式会社

|ページの先頭へ|