NEWS

【DAC50】CadenceとForteのコラボ・トーク「どうやって高位合成の利用を広めるか?」

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

Cadenceはここ数年、DACの展示会会期を通じて連日自社のステージでユーザー企業やパートナー企業による、ツールの活用事例や利用法のショート・プレゼンテーションを実施している。

今年は異例となる高位合成ツールの競合企業Forte Design Automationとのコラボレーション・プレゼンを行なっていた。タイトルは、「How to broadly deploy High Level Synthesis」。登壇したのは、CadenceのSystem Level Design groupのディレクターMark Warren氏とForteのテクニカル・マーケティングVPのMike Meredith氏の両名。

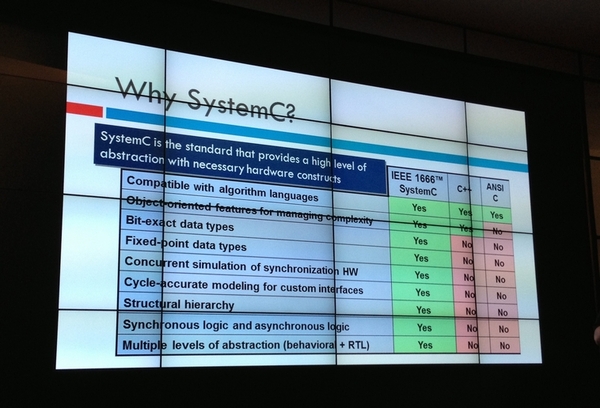

高位合成ツールの販売では競合関係にある両社だが、ツールの入力言語がSystemCという共通点があり、話は「なぜSystemCなのか?」というところから入っていった。CadenceのMark Warren氏は、C/C++に対するSystemCの優位点を幾つか並べ、ビット精度が指定できない言語はハードウェア設計に向かないとした。

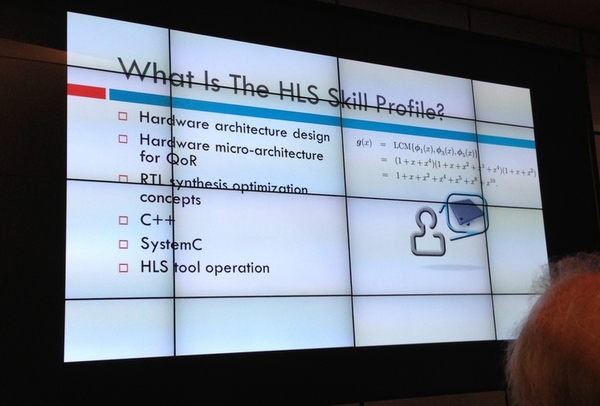

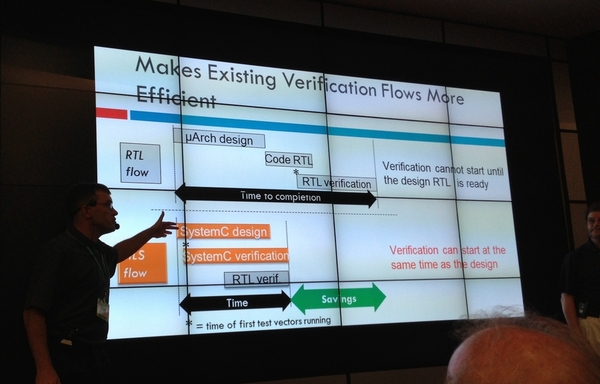

また、Mark Warren氏は、高位合成ツールを用いたハードウェア設計に必要なスキルについても幾つか挙げ、中でも重要なのはRTL設計のスキルとC++言語のスキルであるとし、SystemCベースの高位合成ツールを用いた設計フローのメリットとしては、設計と検証を同時にスタートできる事を挙げ、SystemCを用いる事でアーキテクチャ設計とRTL設計の2ステップを要する既存のフローを一本化できると説明した。ForteのMike Meredith氏は、これらいずれの点についても同意した。

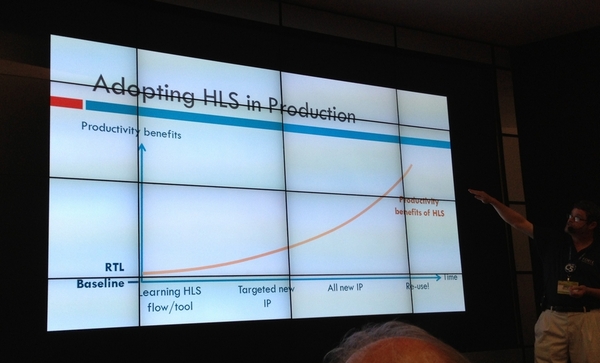

高位合成ツールを用いる事で設計生産性をどの程度向上できるかについては、ForteのMike Meredith氏が説明し、高位合成の導入→部分的なIP設計→新規IP設計→再利用設計と時間を費やしその利用範囲を拡大する事で設計生産性は大きく向上すると語った。

最後にCadenceのMark Warren氏が、高位合成の導入効果は明確でおり、あとはより良いツールを如何に使いこなすかが重要として締めくくった。

同プレゼンテーションは好評で、多数の展示会来場者が訪れ立ち見客も多かったが、第50回DACを通じて、高位合成の利用事例はテクニカルセッションやユーザートラックなど、いたるところで語られており、日本市場がその立ち上げに一役買った高位合成ツールが、世界で浸透している現状を再認識させられた。

|ページの先頭へ|