NEWS

EDSF2012で見たSynopsysのHWベース検証ソリューション「HAPS」と「ZeBu」

2012年11月14-16日、パシフィコ横浜で開催されたEDSFair2012にて、日本シノプシス社のブースを取材した。

まずはEDSF2012直前に発表されたFPGAベースのプロトタイピング・ソリューション「HAPS-70」の話から。Synopsys本社のソリューション・グループ、プロダクト・マーケティング、ディレクターのMick Posner氏に話を聞いた。

※プレスリリース文

※プレスリリース文

Mick Posner氏によると、新製品「HAPS-70」のスペック的な大きな特徴は3つ。

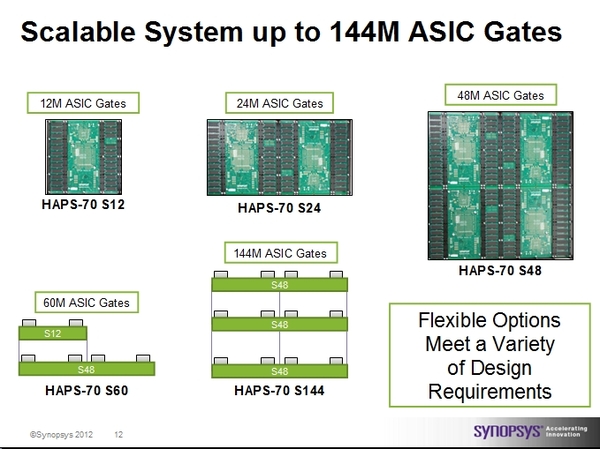

まず、新しい「HAPS-70」はXilinxの最新の28nmFPGA「Virtex-7 2000T」を搭載することで、そのデザイン容量が大幅にアップされた。これまでの「HAPS-60」は最小デザイン容量は450万ASICゲートだったが、「HAPS-70」はFPGAワンチップ搭載の製品で1200万ASICゲートに対応。ベースとなるボードは「Virtex-7 2000T」の搭載数により3種類(1個、2個、4個)用意されており、最大の「HAPS-70 S48」を3枚スタックすると1億4400万ASICゲートものデザイン容量を実現可能となった。デザインに応じて各ベースボードを組み合わせて利用する事もできる。

※画像は日本シノプシス提供のデータ(以下、同様)

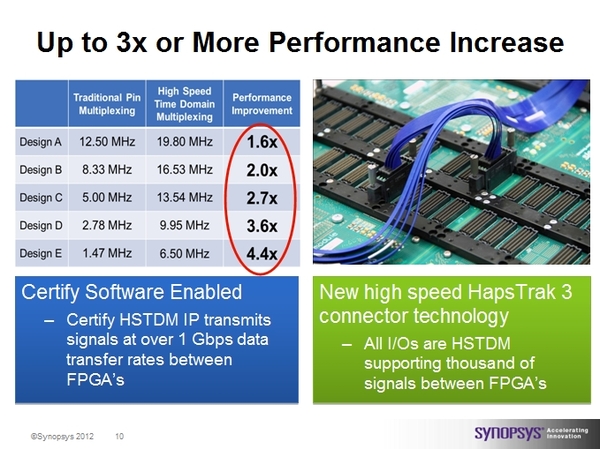

そしてパフォーマンス。「HAPS Trak 3」と呼ぶ独自開発の新たなコネクタと既存のHSTDM(ハイスピード・タイムドメイン・マルチプレキシング)技術の改良によって、「HAPS-60」よりも3倍以上高速なシステム・パフォーマンスを実現した。「HSTDM」機能は、FPGAインプリメント・ツール「Certify」が実現するFPGA間通信の多重化技術で、これにより限られたFPGAのピン数を最大限活用した高速なデータレートを実現する。また、ホストPCからのリモート・コントロールに使用する独自バス「UMRBus」も8ビットから32ビットにエンハンスされ、データ転送速度が従来の最大100MB/秒から最大400MB/秒に向上された。

更に、「HAPS-70」の開発に合わせてFPGAへのインプリメント・ツール「Certify」の機能が強化され、既存のソリューションよりもデザインの分割効率が10倍向上した。最新版の「Certify」では、「HAPS-70」上のリソースを考慮したインテリジェントなデザイン分割が可能で、自動分割後の手修正を少なく抑える事が可能となった。これにより例えば1600万ゲート規模のデザインを数時間でFPGAに実装できるという。

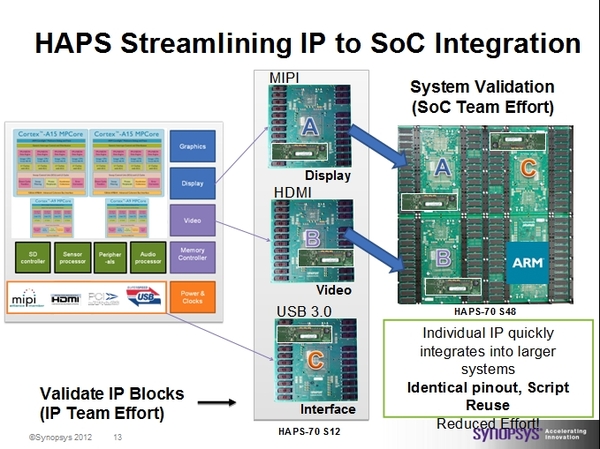

尚、「HAPS-70」は新たなモジュール式のアーキテクチャで実現されており、個別のボードに実装したIPブロックの統合やリユースが容易なため、IP単体の開発からSoCの開発まで柔軟かつ効率良く対応可能。プロトタイプ・ボードでありながら、スケーラビリティと柔軟性を兼ね備えている点は新しい「HAPS-70」の大きな特徴と言える。

その他、「HAPS-70」における改良点は幾つもあるが、熱管理を考慮した冷却ファン付きの骨組み構造の筐体が新たに用意された点、「HAPS-70」専用のデバッグ用拡張メモリ・ドータカードが用意された点などが目を引くところ。既存のドータボードの利用にあたっては、「HAPS-70」用のアダプタが用意される予定と聞いた。

ちなみにMick Posner氏によると、「HAPS」シリーズ製品は既にワールドワイドで計400社、4500セットの納入実績があるとの事。2010年にリリースした先代の「HAPS-60」が大ヒットとなりユーザー企業が100社近く増えたとの事で、新製品「HAPS-70」のリリースによって更なるシェア拡大を目指しているという。

※画像はEDSFair2012会場で展示されていた「HAPS-70」の実物

※画像はEDSFair2012会場で展示されていた「HAPS-70」の実物

※画像はEDSFair2012会場で展示されていた「HAPS-70」の実物

※画像はEDSFair2012会場で展示されていた「HAPS-70」の実物続いて新たにSynopsysのハードウェア・ベース検証ソリューションに加わった、旧EVE社製品「ZeBu」の話。来日していたEVEの元CEO Luc Burgun氏に話を聞いた。

※写真はLuc Burgun氏

Luc Burgun氏は、今年10月に発表されたSynopsysによるEVEの買収により、現在はSynopsysの一員として旧EVE社製品の責任者を務めている。Luc Burgun氏によると、Synopsysの傘下となった事でこれまでも進めていたエミュレーション・システム「ZeBu」とSynopsys製品のインテグレーションが更に加速。現在、仮想プロトタイピング・ツール「Virtualizer」、論理シミュレータ「VCS」と「ZeBu」とのインテグレーションを進めており、よりタイトなコ・シミュレーションが実現される予定との事。

また、間もなくSynopsysによる買収手続きが完了する予定となっているSpringSoftのデバッグ・ツール「Verdi」についても、「ZeBu」とのインテグレーションが進められるだろうとし、デバッグ能力の強化は「ZeBu」のユーザーに大きな価値をもたらすとコメントした。更に「ZeBu」単体の開発ロードマップについては、既にXilinxのVirtex-7ベースの「ZeBu」の開発を進めており、早ければ来年初旬には新しい「ZeBu」が出てくるかもしれないと語った。

尚、Luc Burgun氏にSynopsysにおける「HAPS」と「ZeBu」との棲み分けについて尋ねたところ、「ZeBu」はSoCのハードウェア設計の段階での利用が中心となるのに対し、「HAPS」はソフトウェア(ドライバ、ファーム、OSなど)開発での利用が中心であるため、棲み分けは容易に可能との事。現に両製品を使うユーザーも複数存在しており、両製品はオーバーラップする部分もあるが補完関係を築けるとした。ちなみに同じ質問を先出のMick Posner氏にしたところ同様の回答で、「HAPS」と「ZeBu」は協調した形で顧客に提案していくという話だった。

ちなみに話は逸れるが、昨年のEDSFair会期中に行われたEVE主催のパーティーは、今年も「Synopsys featuring EVE presents 0-Bug Special Night」として開催され、100人以上の参加者を集めた。業界の交流の場として貴重なこのパーティーは、引き続き来年も開催される見通しだ。

|ページの先頭へ|