NEWS

【49DAC】第49回Design Automation Conference-今年のDACは。。

2012年6月3日-8日、米カリフォルニア州サンフランシスコで第49回Design Automation Conferenceが開催された。

今年のDACは3年振りのサンフランシスコ開催だった。3年前の46DACでは来場者は約5100人、出展社は192社を数えたが、今回のDACは最終的に来場者数7388人、出展者は主催者発表によると200社以上だった。(重複カウントやイベント・ブースを除いた純粋な出展企業・団体数は179社。EDA Express調べ。)

数字だけを見比べると、49DACは46DACを超える開催規模と見て取れるが、展示会スペースが46DACの半分になっていたためか、随分と開催規模が小さくなったイメージだった。

様々な情報から推測すると、日本からの参加者はEDAベンダ関係者を除いて40名前後といったところ。大学の先生なども数名見掛けたが、それ以外の企業からの参加者としては、比較的若い世代の方が多かった。

カンファレンスの参加者は前年比9%増の1901名で、49DACで発表された論文は計163本だった。論文の投稿数は計741本で地域別内訳は米国50%、アジア・パシフィックが31%、欧州が19%だった。49DACのBestPaperおよびUSER TRACK Best Papeは以下の通り。その他各アワードの受賞者はDAC公式サイトに掲載されている。

・Best Paper

「Triple Patterning Aware Routing and its Comparison with Double Patterning Aware Routing in 14nm Technology」

Qiang Ma - Univ. of Illinois at Urbana-Champaign, Urbana, IL

・USER TRACK Best Paper

「Deploying Model Checking for Bypass Verification」

Prashant Aggarwal - Oski Technology, Inc., Gurgaon, India

例年通り今年のDACでも様々な話題があったが、関係者を驚かす、または関係者の多くが注目するといった類の大きな話題は特に無かった。話題の方向性としては、昨年に続いて20nm以降の先端プロセスへの対応、3D-ICの実装といった、これからの物理的な課題への対応に関するものが多く、TSMCとサムスン電子は49DAC開催に合わせて20nmプロセス向けの採用ツールおよびフローを相次いで発表した。また3D-IC関連ではCadenceとTSMCが3D-IC設計インフラの開発に関する協業を発表した。

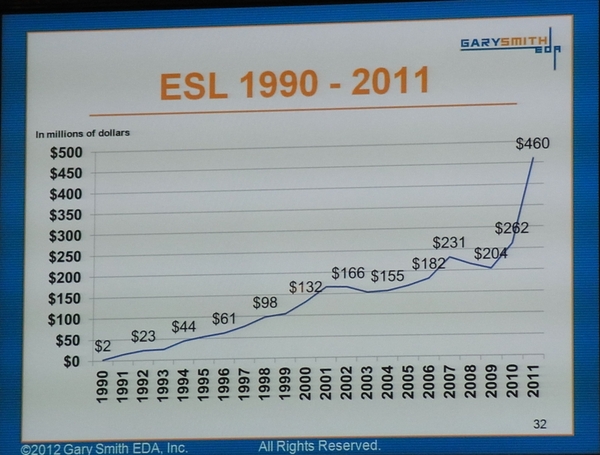

組込みソフトウェア開発を含めたシステムレベルでの設計手法、いわゆるESLに関する話題も依然多かった。特にEDAベンダとしてのプレーヤーが増えた訳では無いが、企画としてESL関連のセッションが多く、いずれもそれなりに人を集めていた様子。Gary Smith EDA社の調査結果によると2011年のESL市場は前年比75%増の成長を遂げたという事で、49DACで耳にした様々な話から北米市場におけるESLの急速な立ち上がりを実感した。

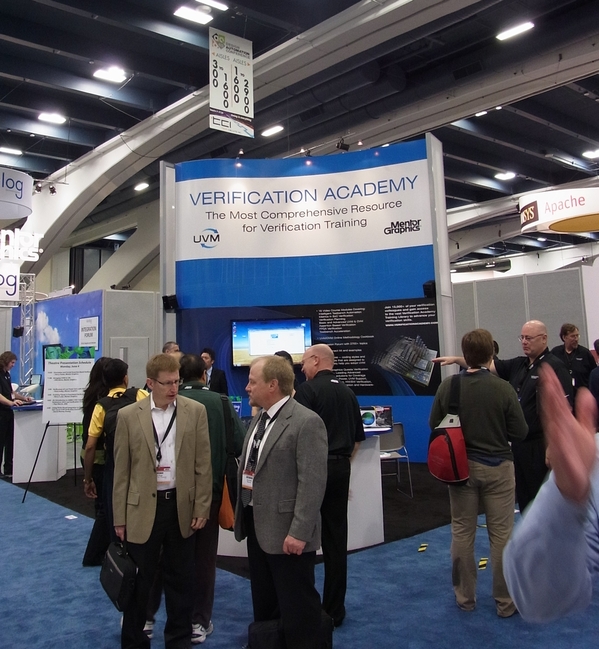

更に今年は検証関連の話題も例年以上に目についた。検証メソドロジUVMのユーザー事例を多数目にしたほか、DAC会期中にVHDL向けの検証メソドロジ「OS-VVM」のユーザー会も開催された。また標準化団体Accellera Systems Initiativeは、DAC会期中にカバレッジ・データベースのアクセス用API標準「UCISバージョン1.0」を発表した。展示製品としてはFPGAベースのプロトタイピング・ソリューションが多かった。

その他目についたは、展示会場におけるフランス企業数の多さ。EVEやDolphin Integrationといった名のあるベンダ以外に、Codasip,DOCEA Power,MagillemなどのESL系ベンダ、DFTツールのDeFacTo Technologies、FPGAパーティショニング・ツールの新興ベンダFlexras Technologies、フィジカル検証ツールのEDXACT、アナログ検証ツールのAsygnなど様々なツールベンダのほかに、Alteris,Cortus,MentaなどIP系ベンダも出展。フランスチームだけで全出展社の1割近い計17社を数えた。フランス政府が進めるエレクトロニクス産業への投資策がEDAベンダを育てる一つの要因となっているようだ。このあたりは日本政府も是非見習って欲しいものである。

DACの開催規模は縮小しつつも、EDA業界の売上は2011年実績で前年比16%増と大手3社を中心に好調を維持しており、その売り上げを支えているのはDACの来場者の属する企業であるが、今回のDACではNVIDIA,Qualcomm,Broadcomm,AMDといったファブレズ勢の企業ロゴを非常に多く目にした。大手に限らず中小EDAベンダにおいても、ユーザー事例となるとこれらファブレス大手の名が必ずと言っていい程登場し、ツールへの積極的な投資を間接的に確認できた。

一方、かつて採用企業としてブースの飾りとなっていた日本企業のロゴを目にする機会は少なく、企業からの参加者も推定数十人レベルと依然少ない。半導体を製造するかどうかはさておき、半導体回路の設計を続けていく以上、設計技術の進化に対応し続けなければ世界の競合と戦うことは出来ないはずである。辛い時だからこそ、緻密な情報収集や次なる一手に向けた投資が必要なのではないだろうか? 49DACにて元気な北米、アジア勢を見て切にそう感じた。もう塞ぎ込んでいる場合ではない。

来年のDACはテキサス州オースチンで6/2-6の開催。DAC開催50年目の節目のカンファレンスとなる。

|ページの先頭へ|