NEWS

SpringSoft Community Conference 2012「ProtoLink」を用いたESL環境の構築

2012年5月10日、新横浜のホテルでSpringSoft社のプライベート・セミナー「SpringSoft Community Conference 2012」が開催され、定員を大幅に上回る約100名の参加者を集めた。

ここでは、同セミナーで発表された「ProtoLink」の活用事例について紹介する。

「ProtoLink」とは、昨年5月にリリースされた、FPGAベース・プロトタイピング・ボードのデバッグ向けのハード及びソフトのツール・セットである。(関連記事)

■ProtoLink活用による上流設計の加速化!!

Cedar-ESLによるアーキテクチャ設計ソリューションのご紹介

富士通セミコンダクター株式会社 開発本部 SoCソリューション統括部 第一設計技術部

プロジェクト課長 蓮實 直信(はすみ なおのぶ)氏

蓮實氏の講演は、同社の設計サービス「Cedar-ESL」において「ProtoLink」を活用してESL環境を構築した事例で、同環境のデモは昨年のET2011にて公開済み。(関連記事)今回の講演では、「ProtoLink」を利用した背景と合わせて同社の考える理想的なESLフローについて語った。

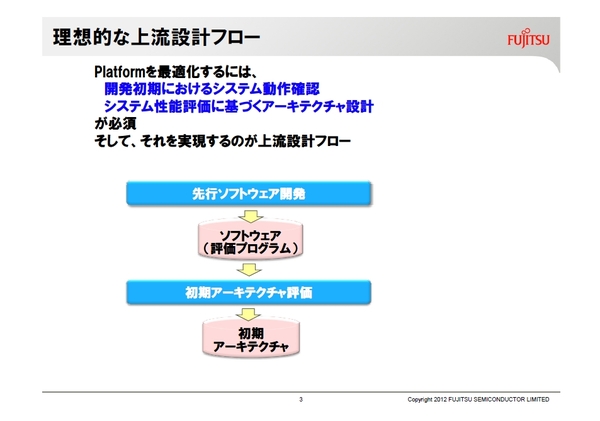

蓮實氏によると、同社では現在主流のIPベースのSoC設計に対して、ユーザー固有のロジック設計に注力してもらうべく、ユーザー・ロジックの開発に最適な仮想プラットフォームの提供に向けて様々な工夫を凝らしている。そのために、SoC初期アーキテクチャー評価用プログラム(ソフトウェア)の作成、次いでそれを用いた初期アーキテクチャー評価と2段階のステップを踏む必要があると考えており、それぞれの作業にはベースは同じだが内容構成の異なる2種類の仮想プラットフォームを使用している。2種類の仮想プラットフォームを使用するのは、シミュレーションの速度と精度という2つのニーズに対応するためであるが、そこに「ProtoLink」を使うのには訳がある。

※画像は富士通セミコンダクター蓮實氏の講演データ

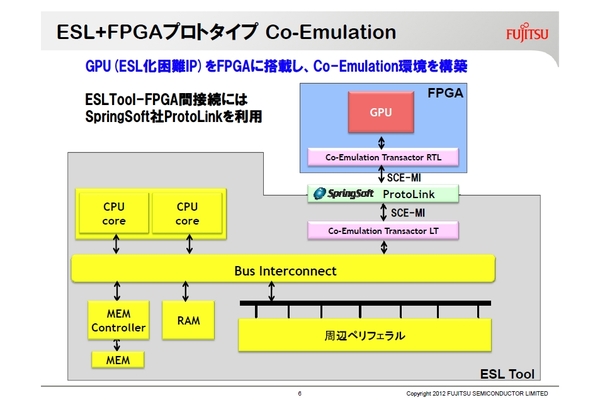

一般的にESLツールで実現される仮想プラットフォームは、ソフトウェアの先行開発やハードウェア・アーキテクチャの評価に向けて用意されるが、その環境構築は簡単に済むものではない。蓮實氏曰く「特にシステム性能を決定する重要なIPのESL化が困難」という事で、本来必要とされている設計の初期段階でフルシステムの仮想プラットフォームを用意することは非常に難しいという現実がある。そこで同社は、ESLモデルの作成が困難なIPをFPGAに搭載し、仮想プラットフォームとFPGAプロトタイプ・ボードとを接続する形を取る事にした。その接続に利用されるのが「ProtoLink」だ。

※画像は富士通セミコンダクター蓮實氏の講演データ

SpringSoftは、「ProtoLink」を用いたESL環境とFPGAプロトタイピング・ボードとの接続ソリューション「CoEmu Verification System」を提供しており、ESL環境側との接続に使うTransactor APIとFPGA側との接続に使うTransactor RTLを用意している。富士通セミでは、このソリューションを用いてS2C社製のFPGAプロトタイプ・ボードとMentor社ESLツール「Vista」ベースの仮想プラットフォームを接続。FPGAボード上にESLモデル化が困難なGPUをマッピングして、ソフトウェア先行開発用および初期アーキテクチャー評価用の2つの協調エミュレーション環境を構築した。

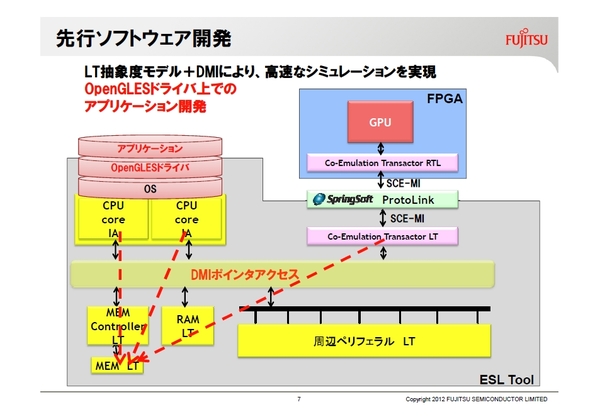

※画像は富士通セミコンダクター蓮實氏の講演データ

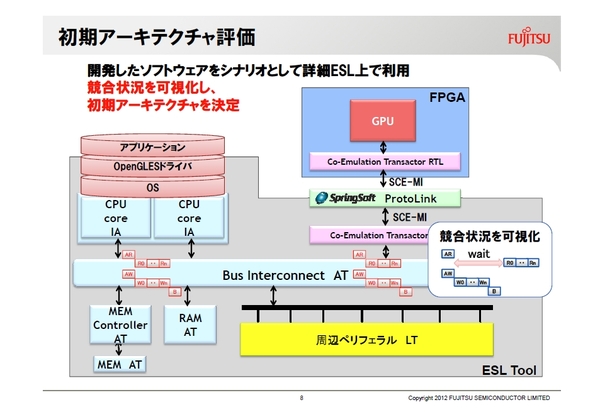

2つの環境の違いは、環境を構成する各種モデルの抽象度で、大きな違いはバスモデル。

ソフトウェア先行開発用の環境では、高抽象度化による高速なシミュレーションを実現すべく、バスはスキップするような形でDMIポインタ・アクセスを用いているのに対し、初期アーキテクチャー評価用の環境ではバスの競合状況を可視化すべく、TLM AT(Approximately-timed)モデルを用いた。両環境で接続に用いるトランザクタはSpringSoftと共同開発した。この2つの環境を用いることで、「まず動くソフト」を開発しGPUの振る舞いを明確化。そして、そのソフトを用いて初期アーキテクチャーの評価を行うという2段階の作業ステップを踏み、設計初期の仕様設計の段階でのプロトタイプ評価を実現した。

※画像は富士通セミコンダクター蓮實氏の講演データ

蓮實氏は、これら環境を使えば、ソフトおよびハードのモデル資産を用いた「モデルを動かしながらの開発」が可能となり、ハードとソフトの整合性のとれた効率的な開発が実現できるとし、更に高位合成ツールを用いればモデルの完成度に応じて開発を加速できるだろうと述べた。

尚、ソフトウェア先行開発と初期アーキテクチャー評価という2ステップの作業は、あくまでも詳細アーキテクチャー評価のための前段の作業で、同社では初期アーキテクチャー評価を完了した後に仮想プラットフォームのモデルを更に詳細化し、サイクル・アキュレートなモデルを用いた評価を経てハードウェア設計を開始しているということ。この評価においてはソフトウェアを用いず擬似モデルで動きを再現しているという。

蓮實氏は講演の中で同社の「Cedar-ESL」で「ProtoLink」を採用した理由を以下のように紹介していた。

【「ProtoLink」の採用理由】

・高速高機能である

・AXI/AHBなどの高速トランザクタをサポートしており、かつリクエストにも対応してくれる

・FPGAボードを選ばない(これが一番大きい)、ESL環境もSCE-MIインタフェースで何にでも繋がる

・Full Visibility機能でFPGA側のバグ解析が可能

・ソフト開発者向けにも提供可能な低価格

・SpringSoftのEDAベンダとしての信頼性、スキルのあるエンジニアによるサポート体制(これも大きい)

|ページの先頭へ|