NEWS

Cadence C-to-Silicon Compilerセミナー-池上通信機のFPGA設計適用事例

2012年5月18日、Cadenceはイノテックと共同で「C-to-Silicon Compilerセミナー」を開催した。

ここでは同セミナーで発表された、池上通信機株式会社のFPGA設計適用事例について紹介する。

■高位合成ツールを使ったFPGA用映像処理回路の開発例

池上通信機株式会社 開発本部 前里真一氏

前里氏の所属は放送機器向けの画像処理ハードウェアの開発が中心で、アルゴリズムの検討も含めてハードウェアを設計している。これまではASICを設計していたが、最近はFPGAの設計が中心ということで、今回の事例もタイトル通りFPGAをターゲットとしている。

今回前里氏のチームが高位合成ツールを用いて設計したのは、XilinxのVertex-6 2個をターゲットとする映像処理回路で、設計者7名、12ヶ月間で実施。元々、C言語は使わず仕様から直接RTLをコーディングするという設計スタイルで、設計チーム7名のうち6名がC/C++/SystemC、高位合成初心者だった。使用したツールはもちろんCadenceの「C-to-Silicon Compiler」である。

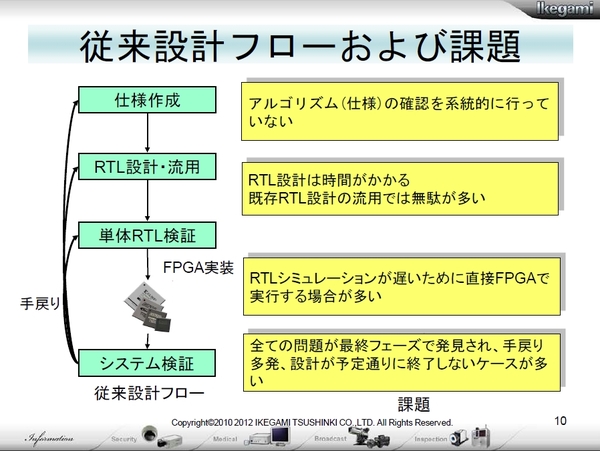

「C-to-Silicon Compiler」を利用するモチベーションは色々とあったが、一番大きかったのは、設計における手戻りの削減。全ての問題が最終的なシステム検証のフェーズで発見され、手戻り多発によってスケジュールに遅れが生じるという課題を何とかしたかったと前里氏。また、過去のRTL資産をそのまま最利用するという無駄も解消したかったという理由も頷けるものだった。

※画像は前里氏の講演スライド

高位合成ツールを導入したC言語ベースの設計フローを実践することにより、設計工数を既存のRTL設計よりも新規設計で半分、流用設計で1/10にする事を目標に掲げた前里氏のチームは、初心者でも効率良く高位合成ツールやSystemCを使えるように、幾つかの工夫を凝らした。

まず、「C-to-Silicon Compiler」の入力となるSystemCモデルの記述スタイルを統一し、記述をパターン化した。アルゴリズム本体記述は、C++のテンプレートクラスをフル活用し、処理はデータクラスに記述する事にして、SystemCの利用はハードウェア・モジュールおよびモジュール間の接続のみに限定した。また制御については構造体で引き渡す形をとった。これによりSystemCによるコーディングの敷居を下げ、効率的なコーディングを実現した。更に入出力端子名やモジュール間の配線名などにルールを設け、チームによる設計作業をスムーズに進めた。

※画像は前里氏の講演スライド

更に「C-to-Silicon Compiler」による高位合成についてもパターン化し、全て内部ループ展開、クラスのメソッドをインライン化、メインループは「C-to-Silicon Compiler」に任せてパイプライン化、という方針で合成を行い、タイミングがメットしない時は合成設定の変更やソースコードの修正を行った。

これらパターン化した記述と合成により、アルゴリズムの検証および合成共に作業を簡略化でき、アルゴリズム検証の段階で機能不具合の95%を検出。合成後のRTLシミュレーションはSystemCのテストベンチを流用した。残りの5%の不具合は最終的な実機でのシステム全体検証で発見した。

デザインのうちSystemCおよび高位合成には向かない、入出力バッファ、DDRメモリ制御、PLL、クロックの切り替え回路については手書きでRTLを起こしたが、最終的にデザイン全体の97%はSystemC/C++から合成したRTLとなった。このRTLで周波数、スループット、面積、設計期間ともに目標を達成し、当初目標としていた早期仕様検討、手戻り削減、設計効率の向上を一通りクリア。高位合成した結果、実機に持って行って動かなかったモジュールは一切無かったという。

※画像は前里氏の講演スライド

尚、前里氏は設計完了後にデザインの一部をASIC向けに合成。幾つかのパターンで試したところ、実デザインの倍の動作周波数300MHzの設定でも高位合成をし直すとタイミング・メットできた。合わせて消費電力も評価したところ、ASICの場合、FPGAよりも1/2-1/7と消費電力が少ない事を確認。同一のソースからターゲットを変えて回路を合成できる事から、高位合成を用いたCベース設計の再利用性の高さも確認できた。

※画像は前里氏の講演スライド

前里氏は最後に幾つかのツールへの改善要求を述べていたが、基本的に「C-to-Silicon Compiler」は使えるという結論でCadenceのサポートにも及第点をつけた。但し、高価なツールであるため、価格だけを見るとFPGA設計には不向きと付け加えた。

■C-to-Silicon Compiler最新のロードマップ

日本ケイデンスの朱氏によると、今年1月にリリースされた現行バージョン11.2.0は、大幅なバージョンアップにより数々の新機能が追加された。

例えば、コードを書き換える事無くコメンドで配列の分割やリストラクチャが可能な「配列のスプリット/リストラクチャ機能」、TLMベース設計で利用するインタフェースのソケット・ライブラリ「Flex Channel」、ゲート・ネットリストを直接生成する機能などが新たに追加された。また、既存の「シーケンシャル・クロック・ゲーティング機能」や、「リソース共有機能」、タイミングがメットするまでレイテンシを延ばしていく「リラックス・レイテンシ・スケジュール・モード」などが大きく機能改善された。

更に今月末(5/27予定)リリース予定のバージョン12.1では、タイミング・クロージャや、パイプラインのマルチ・ストール機能など幾つかの既存機能の改善が予定されているとの事。更にその先には2012年11月のバージョンアップも計画されており、方向性としては、SystemCにおけるUVM検証フローの確立、仮想環境「VSP」との接続、エミュレーター「Palladium」との統合などが予定されているという話であった。

■セミナー参加者へのアンケート結果

当日、日本ケイデンスAvi氏より、セミナー参加者に対して、事前に実施したアンケート結果(回答者数45名)が紹介された。興味深いと思えたポイントは以下の通り。

・SystemC設計・検証における課題は?

A:CとRTLの等価性検証(回答の50%超 ※複数回答あり)

A:記述スタイルの確立(回答の40%超 ※複数回答あり)

・C/C++/SystemCモデルに対してLintチェックを行なっていますか?

A:導入している(回答の約35%)

・高位合成の適用によって従来設計より設計の短縮期間は?

A:1/2-1/5(回答の52%)

A:1/5-1/10(回答の20%)

・今後高位合成技術が普及するために最も重要なポイントは?

A:設計者の意識改革(回答の32.5%)

A:ツールの改善(回答の30%)

・今後5年以内に高位合成技術が従来のRTL設計を取って代わると思いますか?

A:代わる(回答の32.5%)

A:代わらない(回答の32.5%)

A:分からない(回答の35%)

|ページの先頭へ|