NEWS

Synopsysが検証IPのアーキテクチャーを刷新、速度向上ほか大幅機能強化

2012年2月27、Synopsysは、アーキテクチャーを刷新した同社の新しい検証IP「Discovery VIP」を発表した。

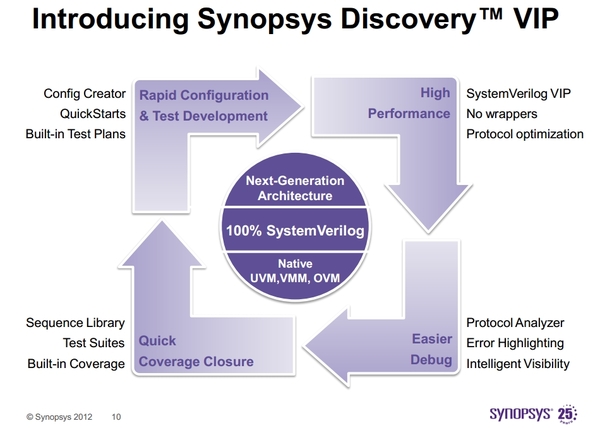

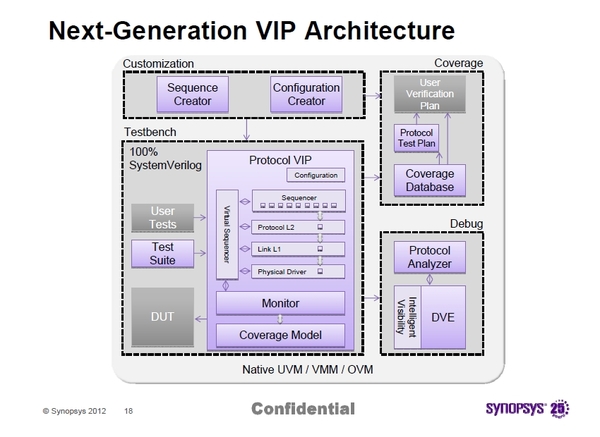

発表によると新しい「Discovery VIP」は、これまで「OpenVera」をベースとしていた検証IPのアーキテクチャーを刷新し、新しいVIPERアーキテクチャーをベースに開発されたもので、100% SystemVerilogでコーディングされており、既存のSystemVerilogベースの検証メソドロジUVM、VMM、OVMの全てで利用することが可能。新たなVIPERアーキテクチャーによって、既存の検証IPには無かった様々なメリットを提供する。

※画像はSynopsys社Web掲載上のデータ

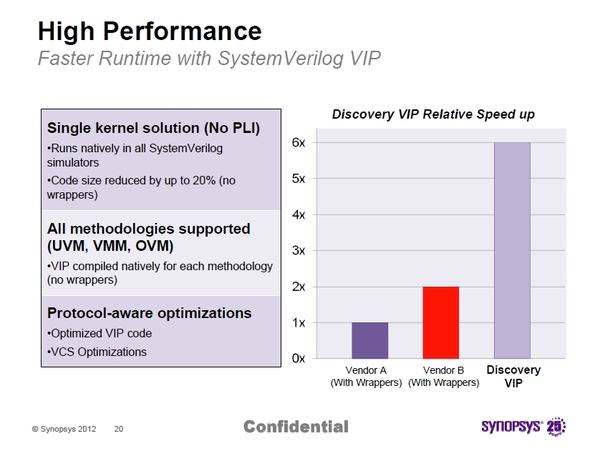

まず、検証IPのアーキテクチャーが変更され、100% SystemVerilogでコーディングしたことにより、検証IPを利用する上で従来使用していたラッパーやデータ変換などが不要となった。これにより検証をより高速化可能で、Synopsysによると最大で従来比4倍相当のパフォーマンスを実現する。CadenceやMentorの検証IPもSynopsysがこれまでVeraをベースとしていたようにeやCをベースとしているため、検証速度に関してはSynopsysの「Discovery VIP」より劣る事になる。尚、「Discovery VIP」は、Synopsysの「VSC」以外の主要な市販シミュレーターでも利用可能で同様の高速化を実現可能だが、最適化により最もパフォーマンスが高いのは「VCS」のようだ。

※画像はSynopsys社提供のデータ

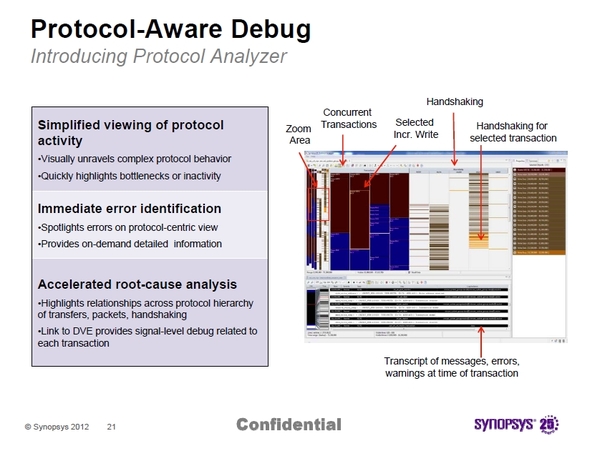

また、今回新たに「Discovery VIP」用のデバッグ環境「Protocol Analyzer」が用意された。同ツールは検証IPとは独立した形で別売される検証IP専用のデバッグ環境で、GUIを用いてプロトコル・トラフィックをトランザクション・ベースでデバッグする機能を提供する。これまでは信号レベルのデバッグしか出来なかったが、VIPERアーキテクチャーにより抽象度の高いプロトコルのデバッグが可能となった。「Protocol Analyzer」はシミュレーター「VCS」に接続して使用するものだが、ライセンスを購入すれば複数の環境でコピーして利用できるという。

※画像はSynopsys社提供のデータ

更に今回「Discovery VIP」の自動コンフィギュレーションを行うGUIも用意された。これまでコンフィギュレーションはソースコードレベルで人手の作業で行われていたが、GUIベースの自動設定が可能となった。また、コンフィギュレーションに応じたテスト・プランの自動生成やカバレッジの作成も可能となった。

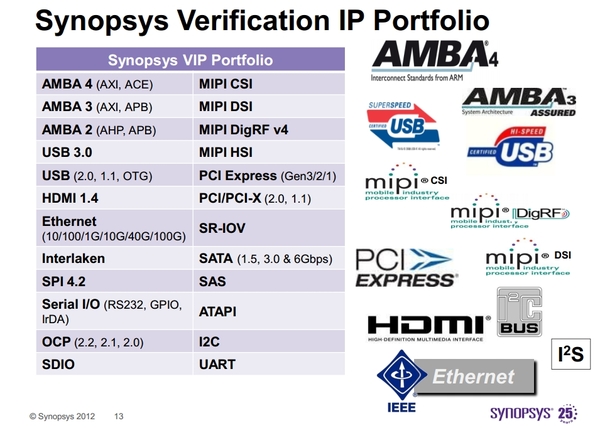

Synopsysは既に新アーキテクチャーの「Discovery VIP」の最新製品として、USB 3.0、ARM AMBA AXI3、AXI4、ACE、HDMI、MIPI、Ethernet 40G/100G、PCI Express、SATA、OCP、などの検証IPを提供しており、今後も順次既存の検証IPをVIPERアーキテクチャーに置き換えていく計画。既に7割方の製品は改版が完了しているようだが、全ての検証IPが100% SystemVerilog化されるには、あと半年ほどかかる予定だという。

|ページの先頭へ|