NEWS

【EDSFレポート】アルデック、VHDLサポート完了の「ALINT」は今後も機能拡張予定

Electronics Design and Solution Fair 2009に出展していたアルデック・ジャパンブースレポート。

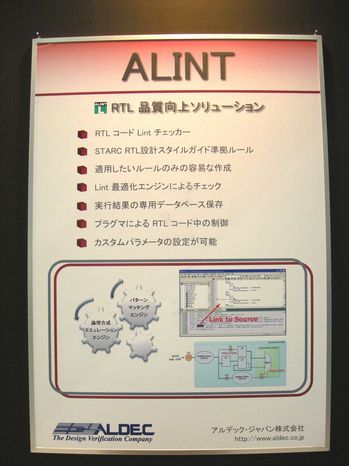

アルデックが最近力を入れているのはRTLリントチェッカ「ALINT」。昨年の1月にSTARCの「RTL 設計スタイルガイド Verilog HDL 編 第2版」のルールをサポートした製品をリリース、昨年12月にはVDHLもサポート。STARCルールをチェックできるLintチェッカは数製品しか市販されていなく、そのコストパフォーマンスの高さで国内の採用が順調に進んでいる。

アルデック・ジャパンの藤永氏によると、今後はSTARCルール以外にも海外の標準ルールなどに対応していく予定。製品戦略としては、低消費電力設計のためのPowerフォーマットやCDCのチェックなどの機能も取り込んでいく計画と聞いた。

主力の論理シミュレータについては、この不景気の影響もありコストパフォーマンスの高い「Active-HDL」の引き合いが増加。高機能製品の「Riviera」については、アサーションを利用するユーザーを中心に導入が増えているという事で、今後は「Active-HDL」と合わせてOVMライブラリの早期サポートを目指しているという話だった。

主力の論理シミュレータについては、この不景気の影響もありコストパフォーマンスの高い「Active-HDL」の引き合いが増加。高機能製品の「Riviera」については、アサーションを利用するユーザーを中心に導入が増えているという事で、今後は「Active-HDL」と合わせてOVMライブラリの早期サポートを目指しているという話だった。

※OVM:Open Verification Methodology

関連記事:

関連記事:

アルデック、Actelユーザー向けプロトタイピング・アダプタボードのリリースとLINTツールのバージョンアップを発表

http://www.eda-express.com/2008/12/actellint.html

※アルデック・ジャパン株式会社

http://www.aldec.co.jp

|ページの先頭へ|